中国科学院大学数字集成电路作业开源——组合逻辑章节

中国科学院大学数字集成电路作业开源——第1-3章

0、说明

开源内容为中国科学院大学《高等数字集成电路分析与设计》课程的个人作业答案,此开源仅供学习交流,禁止未经作者同意的转载或抄袭。此外作业中可能有一些不严谨甚至出错的地方,欢迎各位读者在评论区中指出,一些有疑问的地方也欢迎讨论。

所有代码均已上传gitee

https://gitee.com/sasasatori/ucas_digital_intergrated_circuit.git

1、基础概念问题

1.1请简要描述集成电路设计过程中,抽象分层的常规做法?抽象分层对集成电路设计所带来的意义何在?

答:抽象分层的常规做法一般会通过抽象和分层思想,将整个集成电路设计分作系统层级、模块层级、门电路层级、电路层级、器件层级共五个层级。

抽象分层对集成电路设计带来的意义包括:

-

提高集成电路的设计效率,使得单个设计人员可以更快速的完成更大规模的电路设计,设计者可以更多聚焦到特定边界下的极致任务高效优化

-

实现了整个产业链从系统到器件的层次化、精细化的任务分工,不同的设计层级有不同的公司钻研,促进了产业的飞速发展

-

整个产业可以充分借助高性能机器、EDA工具实现按规则的优化迭代

-

抽象分层思想一定程度上避免了整个设计在架构和实现上的缺陷,关心对象属性的缩小,往往可以研究出问题某一方面的本质规律和问题

1.1请简要描述为何典型的超大规模集成电路,通常是采用CMOS工艺为基础进行的设计,而不是采用基于其他工艺为基础进行VLSI设计?

答:因为CMOS工艺相比其他工艺具备结构简单,集成度高,耗散功率小的优点。结构简单意味着电路制备更容易,成本更低、集成度高意味着电路面积可以减小,电路频率可以提高、耗散功率小意味着大规模电路的能量损失相对少。

1.2 请简要描述ASIC/FPGA前端设计流程?简要描述Top-Down设计流程的意义及挑战?

答:ASIC前端设计流程: RTL级代码----功能仿真----逻辑综合----等价性检查,形式验证----静态时序分析

FPGA设计流程:RTL级代码----功能仿真-----逻辑综合-----门级仿真-----布局布线----时序仿真----版级验证与仿真

Top-Down设计流程的意义:可以优化设计流程、提高设计效率,并确保工程设计整体的关联性

Top-Down的挑战:需要制定清楚各个流程间的边界条件;需要在特定边界条件的约束下完成对特定任务的高效收敛设计

1.3 请简要描述在CMOS电路设计过程中,如何避免或降低寄生电感引起的同步开关噪声(SSN)所导致的电路性能不稳定?

答:1. 减小信号的电源和地平面的阻抗

\2. 减小电源和地的回路电感

\3. 合理分配芯片的信号、电源和地引脚的数量比值

\4. 在芯片电源和地引脚附件添加合理的去耦电容

1.4 请分析针对CMOS反相器电路设计优化,在输出驱动一定的前提下,通过哪些技术手段可提高CMOS反相器的驱动能力?

答:可以通过增大反相器尺寸来提高其驱动能力,尺寸即CMOS反相器中的CMOS与NMOS的宽长比。

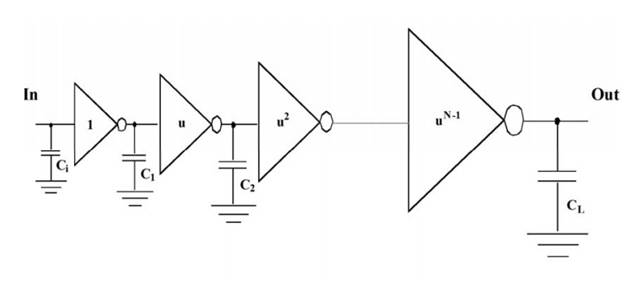

由于大尺寸的反相器其输入电容也会增大,造成前一级电路驱动反相器的时间增加,可以通过锥形反相器链的方式,通过逐级增加尺寸的级联反相器链平衡驱动能力和延时。

1.5 请结合所在课题组研究课题方向,对如何学好本课程内容并结合课程内容更好的开展研发工作进行简要论述。

答:本课题组主要研究存算一体与神经网络加速方向,需要进行芯片设计和流片,其中存算一体神经网络芯片的行列控制、时序产生等均需要数字集成电路设计的知识。为了更好地学习本课程的内容,需要结合课堂内容与课题组项目的实际需求,深入理解设计方法学,并吸收一些课题组过去的工程经验,结合课程内容加深理解。

1.6 请简要描述基于VerilogHDL语言对VLSI/FPGA设计带来的意义?

答:VerilogHDL语言使得VLSI/FPGA设计变为可以通过语言描述的方式进行;

通过VerilogHDL可以对电路进行不同层级的建模(系统级、算法级、RTL级、门级、开关级),更容易的通过分层抽象的思想完成Top-Down的设计流程

1.7 请简要描述基于VerilogHDL语言完成的可综合电路与不可综合电路的特点?

答:可综合电路:可以通过综合工具转化为门级网表的RTL级电路;不可综合电路:无法通过综合工具转化为门级网表的RTL级电路

可综合电路:保证可综合性,包括:

(1) 不使用initial

(2) 不使用延时语句

(3) 不使用循环次数不确定的循环语句,如forever,while等

(4) 不使用用户自定义原语

(5) 尽量使用同步方式设计电路

(6) 除非是关键路径的设计,一般不采用调用门级元件进行描述设计的方法,采用行为语句进行设计

(7) 用always块描述组合逻辑,在敏感信号列表中列出所有的输入输出信号

(8) 所有的内部寄存器应能够被复位,使用FPGA实现设计时尽量使用器件的全局复位端作为系统总的复位

(9) 对时序逻辑的描述和建模尽量使用非阻塞赋值方式,对组合逻辑建模可以使用阻塞赋值也可以使用非阻塞赋值,但在同一个过程块中,避免同时使用阻塞和非阻塞赋值

(10)不在一个以上的always块中对同一个变量赋值,对同一个赋值对象不能既使用阻塞赋值又使用非阻塞赋值

(11)在if或case语句中对所有条件分支明确赋值,避免变量被推导成锁存器

(12)避免混合使用上升沿和下降沿触发

(13)同一个变量的赋值不能受多个时钟控制,不能受两种不同的时钟条件(或不同的时钟沿)控制

(14)避免在case语句的分支项中使用x值或z值

不可综合电路:使用了不可综合的语句或违反了综合规则等,包括:

(1) 使用initial,events,force,release,fork,join等不可综合的语法

(2) 使用real,time等不可综合的数据类型

(3) 对reg数据类型进行assign或deassign

(4) 使用非门级原语

(5) UDP和table

(6) 敏感列表中同时带有posedge和negedge的信号,如always@(posedge clk or negedge clk)

(7) 同一个reg变量被多个always块驱动

(8) 延时语句

(9) 与x值或z值的比较

1.8 请简要描述阻塞描述语句与非阻塞描述语句的各自适用电路与使用注意事项?

答:阻塞描述语句:适用于组合逻辑电路结构的设计,在描述组合逻辑的always块中使用阻塞赋值,会将电路综合成组合逻辑的电路结构

非阻塞描述语句:适用于时序逻辑电路结构的设计,在描述时序逻辑的always块中使用非阻塞赋值,会将电路综合成时序逻辑的电路结构

阻塞赋值语句计算RHS后更新LHS,此时不允许别的赋值语句的执行。非阻塞计算RHS到更新LHS的期间,其他的Verilog语句也能同时计算RHS和更新LHS。

注意事项:

(1) 时序电路建模时,用非阻塞赋值

(2) 锁存器电路建模时,用非阻塞赋值

(3) 用always块建立组合逻辑模型时,用阻塞赋值

(4) 在同一个always块中简历时序和组合逻辑电路时,用非阻塞赋值

(5) 在通过一个always块中不要既用非阻塞赋值又用阻塞赋值

(6) 不要在一个以上的always块中为同一个变量赋值

(7) 用$strobe系统任务来显示用非阻塞赋值的变量值

(8) 在赋值时不要使用#0延迟

1.9 请简要分析全同步电路与异步电路在常规VLSI电路设计过程中的设计应用注意事项与考虑思路?

答:(1) 全同步电路中所有触发器共用一个触发信号源,异步电路所有触发器不共用触发信号源

(2) 全同步电路所有的触发器状态同时刷新,信号延迟时间短,但结构复杂。异步电路结构简单,但触发器刷新不同步,信号延迟可能会累积导致状态异常

(3) 同步电路可以有效避免毛刺的影响,提高设计可靠性,并可以简化静态时序分析过程,便于验证时序性能

(4) 异步电路设计时必须要考虑跨时钟域可能会导致的亚稳态问题

1.10 请简要分析Latch与D-Flip-Flop电路在常规VLSI电路设计过程中的设计应用注意事项与考虑思路?

答:(1) Latch为电平敏感电路,D-Flip-Flop为边沿敏感电路

(2) Latch由电平触发,非同步控制,在使能信号有效时Latch相当于通路,使能信号无效时Latch保持输出状态,D-Flip-Flop由时钟沿触发,同步控制

(3) Latch容易产生毛刺,D-Flip-Flop不易产生毛刺

(4) Latch消耗的门资源少于D-Flip-Flop

(5) Latch使得静态时序分析变得极为复杂

一般设计时应避免产生Latch,由于Latch不能够过滤毛刺,会对时序造成很大的危害。

2 基于VerilogHDL进行逻辑电路设计

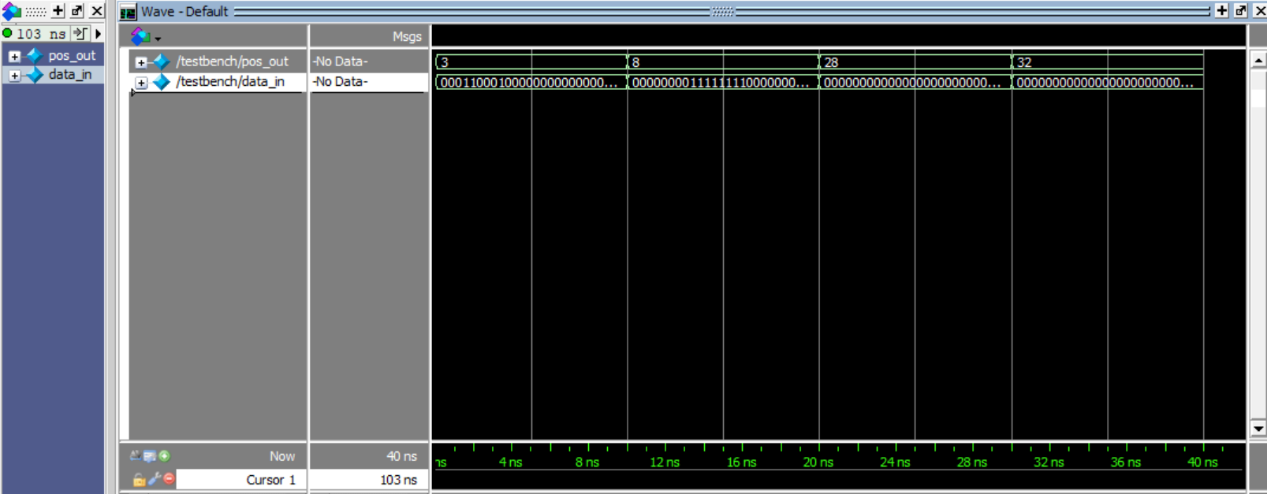

2.1向量前导1检测器

设计一个组合逻辑电路,检测输入32位0/1向量中从高到低第一个1出现的位置,如果向量为全0则输出32。例如:

输入00011000 10000000 00000000 00000000,输出3;

输入00000000 11111111 00000000 00000000,输出8;

输入00000000 00000000 00000000 00001010,输出28.

模块输入输出功能定义:

| 名称 | 方向 | 位宽 | 描述 |

|---|---|---|---|

| data_in | I | 32 | 输入0/1向量 |

| pos_out | O | 6 | 前导1出现位置,取值范围0 ~ 32 |

设计要求:

Verilog实现代码可综合,逻辑延迟越小越好,给出仿真结果。

module Leading_1_Vector_Detector (

input [31:0] data_in,

output reg [5:0] pos_out

);

integer i;

always @(data_in) begin

for(i = 0; i < 32 ; i = i+1) begin

if (data_in[i]) pos_out = i;

else pos_out = pos_out;

end

if(data_in) pos_out = 6'd31 - pos_out;

else pos_out = 6'd32;

end

endmodule

module testbench ();

reg [31:0] data_in;

wire [5:0] pos_out;

initial begin

data_in = 32'b00011000_10000000_00000000_00000000;

#10

data_in = 32'b00000000_11111111_00000000_00000000;

#10

data_in = 32'b00000000_00000000_00000000_00001010;

#10

data_in = 32'b00000000_00000000_00000000_00000000;

end

Leading_1_Vector_Detector U_L1VD(

.data_in(data_in),

.pos_out(pos_out)

);

endmodule

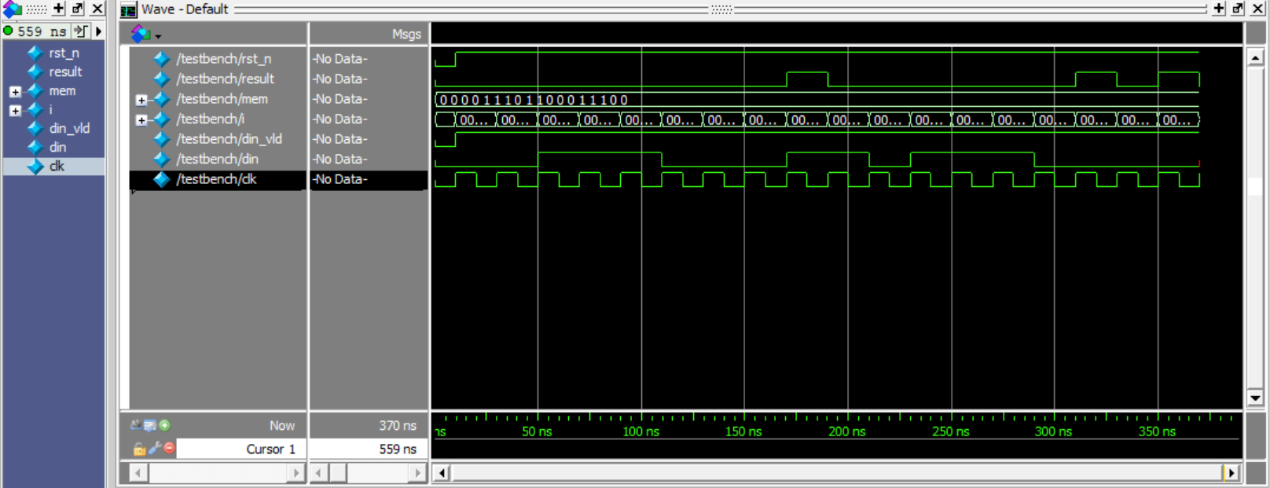

2.2序列检测器

设计一个序列检测同步时序逻辑电路,要实现的功能如下:

当已有输入码流出现序列111000或101110时输出检测信号为1,否则输出为0。在时序上检测到完整序列的下一个时钟周期输出检测结果。输入信号有效为1时表示当前输入有效,否则表示无效。之前输入依旧计入序列中并不清零,即允许序列重叠检测。例如:

输入码流(设输入数据均有效)和输出检测为

[I] 0 0 1 1 1 0 0 0 1 1 0 1 1 1 0 0 0 0

[O] 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 1

模块输入输出功能定义:

| 名称 | 方向 | 位宽 | 描述 |

|---|---|---|---|

| clk | I | 1 | 系统时钟 |

| rst_n | I | 1 | 异步复位,低电平有效 |

| din_vld | I | 1 | 输入数据有效指示 |

| din | I | 1 | 输入数据 |

| result | O | 1 | 输出检测结果 |

设计要求:

Verilog实现代码可综合,面积越小越好,给出仿真结果。

module Sequenial_Detector (

input clk,

input rst_n,

input din_vld,

input din,

output result

);

reg [5:0] seq;

assign result = ((seq == 6'b111000) || (seq == 6'b101110)) ? 1'b1 : 1'b0;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

seq <= 0;

end

else if (!din_vld) begin

seq <= seq;

end

else begin

seq <= {seq[4:0],din};

end

end

endmodule

module testbench ();

reg clk;

reg rst_n;

reg din_vld;

reg din;

wire result;

Sequenial_Detector U_SD(

.clk(clk),

.rst_n(rst_n),

.din_vld(din_vld),

.din(din),

.result(result)

);

always #10 clk = ~clk;

initial begin

rst_n = 1'b0;

clk = 1'b0;

din_vld = 1'b0;

#10

rst_n = 1'b1;

din_vld = 1'b1;

end

integer i;

reg mem[17:0];

initial $readmemb("input.txt",mem);

always @(posedge clk or negedge rst_n) begin

if(!rst_n == 1) begin

i = 0;

din <= 0;

end

else begin

din <= mem[i];

i = i + 1;

end

end

endmodule

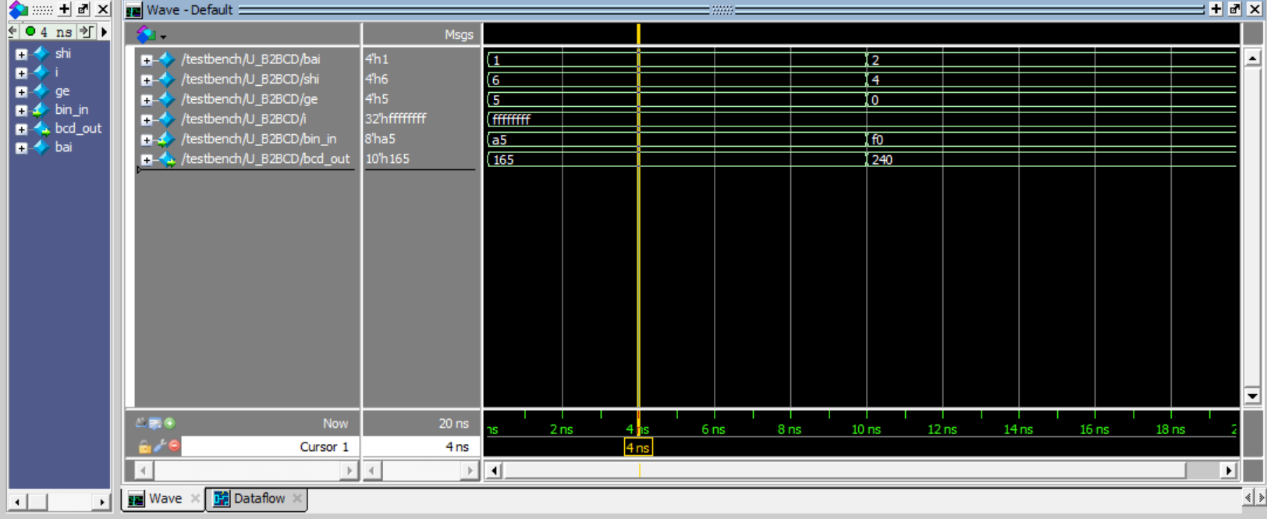

2.3二进制转BCD码逻辑

设计一个8位无符号二进制数(取值范围0 ~ 255)到10位BCD码的转换组合逻辑电路。其中12位BCD码定义如下:

| 数据位 | 描述 |

|---|---|

| 9:8 | 百位BCD码,取值0 ~ 2 |

| 7:4 | 十位BCD码,取值0 ~ 9 |

| 3:0 | 个位BCD码,取值0 ~ 9 |

例如:

输入8'b10100101(十进制165),输出10'b01_0110_0101;

输入8'b11110000(十进制240),输出10'b10_0100_0000.

模块输入输出功能定义:

| 名称 | 方向 | 位宽 | 描述 |

|---|---|---|---|

| bin_in | I | 8 | 输入二进制数 |

| bcd_out | O | 10 | 输出BCD编码 |

设计要求:

Verilog实现代码可综合,逻辑延迟越小越好,给出仿真结果。

module Binary2BCD (

input [7:0] bin_in,

output [9:0] bcd_out

);

integer i;

reg [3:0] ge,shi,bai;

always @(bin_in) begin

bai = 4'b0;

shi = 4'b0;

ge = 4'b0;

for (i = 7; i >= 0; i = i-1) begin

if(bai >= 5) bai = bai + 3;

if(shi >= 5) shi = shi + 3;

if(ge >= 5) ge = ge + 3;

bai = bai << 1;

bai[0] = shi[3];

shi = shi << 1;

shi[0] = ge[3];

ge = ge << 1;

ge[0] = bin_in[i];

end

end

assign bcd_out = {bai[1:0],shi,ge};

endmodule

module testbench ();

reg [7:0] bin_in;

wire [9:0] bcd_out;

Binary2BCD U_B2BCD(

.bin_in(bin_in),

.bcd_out(bcd_out)

);

initial begin

bin_in = 8'b10100101;

#10

bin_in = 8'b11110000;

end

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号