数字asic流程实验(六) 静态时序分析&等效性检验&后仿真

数字asic流程实验(六) 静态时序分析&等效性检验&后仿真

1.静态时序分析

PrimeTime(以下简称PT)是Synopsys的一个全芯片、门级静态时序分析工具,是当今大型芯片设计的设计和分析流程的重要组成部分。

时序分析手段可分为动态时序分析(Dynamic Timing Simulation)和静态时序分析(Static Timing Analysis)

动态时序分析是通常的仿真,因为不可能产生完备的测试向量,覆盖门级网表中的每一条路径。因此在动态时序分析中,无法暴露一些路径上可能存在的时序问题。动态时序验证在验证功能的同时验证时序,需要输入向量作为激励。随着规模增大,所需要的向量数量以指数增长,验证所需时间占到整个设计周期的50%,且这种方法难以保证足够的覆盖率,因而对片上系统芯片设计已成为设计流程的瓶颈。

静态时序分析是采用穷尽分析方法来提取出整个电路存在的所有时序路径,计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延时和最小路径延时的分析,找出违背时序约束的错误。

动态时序分析的优点为:

较为精确,可以进行功能验证

缺点为:

分析速度慢,需要输入矢量,可能会遗漏关键路径

静态时序分析的优点为:

分析速度快,对所有路径检查,不会遗漏关键路径

缺点为:

不能验证功能

本次实验实验采用PrimeTime进行静态时序分析,再通过Modelsim进行后仿真验证电路功能,从而实现对电路的全面检验。

通过编写TCL脚本的方式操作PrimeTime,本次实验对布局布线(layout)前的门极网表电路(由DC综合得到)和布局布线后的门极网表电路(由ICC布局布线后导出)进行静态时序分析。

DC综合后的门级网表的静态时序分析TCL脚本的内容如下:

set search_path "../../lib/logic"

set link_path "* slow.db" #读入标准元件库

set active_design cic_filter

read_verilog "../../dc/outputs/cic_filter_post_dc.v" #读入DC综合后的门级网表

current_design $active_design

#定义设计环境和设置设计约束的参数必须与DC综合脚本文件内容一致!!!

set_wire_load_model -name "smic18_wl10"

set_wire_load_mode top

create_clock -period 156 -waveform {0 78} [get_ports clk] -name clk

create_generated_clock [get_pins div/clk_div] -source [get_ports clk] -divide_by 64 -name clk_div

set_ideal_network [list clk clk_div] -no_propagate

set_clock_latency 2.5 clk

set_clock_transition 0.3 clk

set_clock_uncertainty 1.5 -setup clk

set_clock_uncertainty 0.3 -hold clk

set_drive 0 [list clk rst_n]

set_driving_cell -lib_cell NAND2X1 in

set_load 2 [all_outputs]

set_input_delay 35 -clock clk [list in rst_n]

set_output_delay 35 -clock clk_div [all_outputs]

report_constraint -all_violators

report_timing -to [all_registers -data_pins]

report_timing -to [all_outputs]

#exit

#start_gui

ICC布局布线后导出的门级网表的静态时序分析TCL脚本的内容如下:

set search_path "../../lib/logic"

set link_path "* slow.db" #读入标准元件库

set active_design cic_filter

read_verilog "../../icc/outputs/cic_filter_post_layout.v" #读入ICC布局布线后的门级网表

current_design $active_design

#set_wire_load_model -name "smic18_wl10"

#set_wire_load_mode top

#read_sdf "/home/yhd/yjx/shiyan/icc/shiyan_post_layout.sdf"

read_parasitics "../../icc/cic_filter.spef.max" #读入寄生参数文件

#定义设计环境和设置设计约束的参数必须与DC综合脚本文件内容一致!!!

create_clock -period 156 -waveform {0 78} [get_ports clk] -name clk

create_generated_clock [get_pins div/clk_div] -source [get_ports clk] -divide_by 64 -name clk_div

set_propagated_clock [get_clocks clk]

set_drive 0 [list clk rst_n]

set_driving_cell -lib_cell NAND2X1 in

set_input_delay 35 -clock clk [list in rst_n]

set_output_delay 35 -clock clk_div [all_outputs]

set_load 2 [get_ports out]

report_constraint -all_violators

report_timing -to [all_registers -data_pins]

report_timing -to [all_outputs]

#exit

#start gui

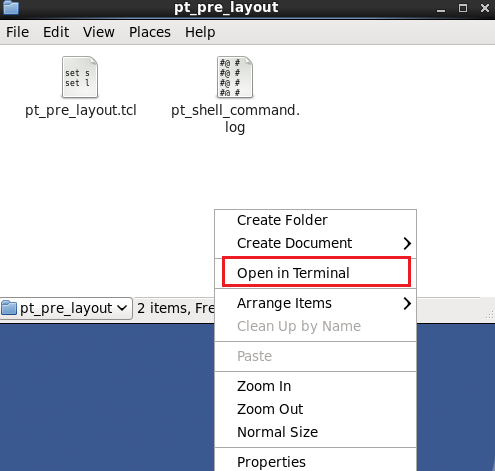

1.打开虚拟机,在/home/crazy/Desktop/experiment/pt/pt_pre_layout 下右键Open in terminal

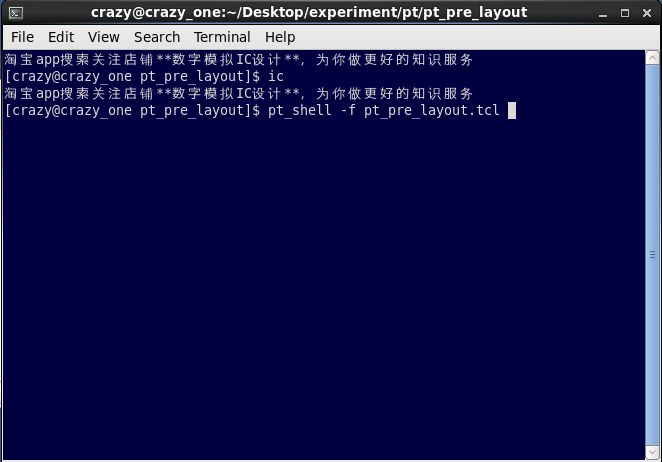

2.在terminal中依次输入

ic

pt_shell -f pt_pre_layout.tcl

执行TCL脚本

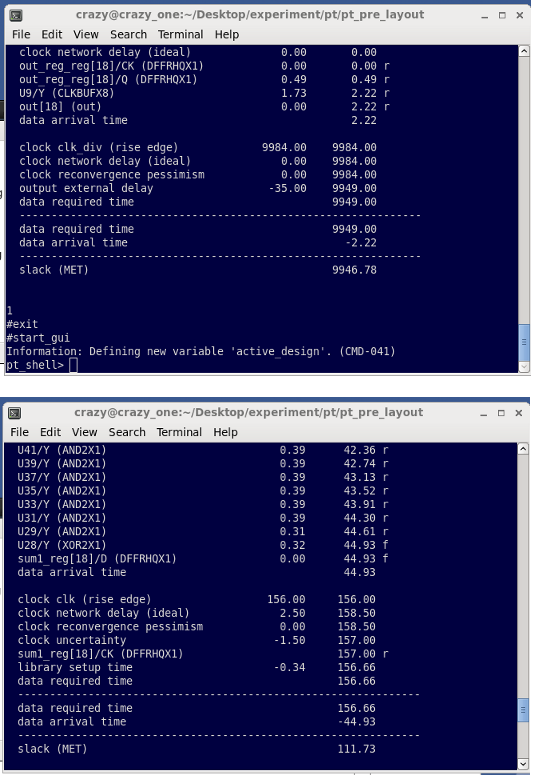

3.检查结果是否存在报错(如果出错会terminal中会打印0并输出报错信息),如果存在报错则根据报错信息返回修改脚本,或修改Verilog并重新进行DC综合

此外还需要确保所有的slack均大于0

4.同理至/home/crazy/Desktop/experiment/pt/pt_post_layout 下运行脚本并观察结果,如果出现报错则返回修改脚本或重新进行ICC布局布线步骤

2.等效性检验

Formality是Synopsys的形式验证工具,你可以用它来比较一个修改后的设计(如ECO)和它原来的版本,或者一个RTL级的设计和它的门级网表,再或者综合后的门级网表和做完布局布线及优化之后的门级网表在功耗上是否一致。

所谓形式验证,就是通过比较两个设计在逻辑功能上是否等同的方法来验证电路的功能。这种方法的优点在于它不仅提高了验证的速度,可以在相当大的程度上缩短数字设计的周期,而且更重要的是,它摆脱了工艺的约束和仿真testbench的不完全性,更加全面地检查了电路的功能。

同样通过编写TCL脚本的方式操作Formality,本次实验分别对DC综合前的Verilog电路与综合后的门级网表、ICC布局前后的门极网表进行等效性检验。

对DC综合前的Verilog与综合后的门级网表进行等效性检验的TCL脚本内容如下:

start_gui

set search_path "../../src/ ../../dc/outputs" #设置搜索路径

#读入Verilog电路

create_container ref

read_verilog cic_filter.v

read_verilog divider64.v

set_top cic_filter

set_reference_design ref:/WORK/cic_filter

#link $ref

read_verilog -c impl -netlist cic_filter_post_dc.v #读入DC综合后门级网表

read_db ../../lib/logic/slow.db #读入标准元件库

set_top cic_filter

set_implementation_design impl:/WORK/cic_filter

current_design $impl

verify #执行比较

对ICC布局前后的门极网表进行等效性检验的TCL脚本内容如下:

create_container ref

read_verilog -netlist "../../dc/outputs/cic_filter_post_dc.v" #读入DC综合后门级网表

read_db "../../lib/logic/slow.db" #读入标准元件库

set_top cic_filter

set_reference_design ref:/WORK/cic_filter

read_verilog -c impl -netlist "../../icc/outputs/cic_filter_post_layout.v" #读入ICC布局布线后门级网表

read_db "../../lib/logic/slow.db" #读入标准元件库

set_top cic_filter

set_implementation_design impl:/WORK/cic_filter

current_design $impl

verify #执行比较

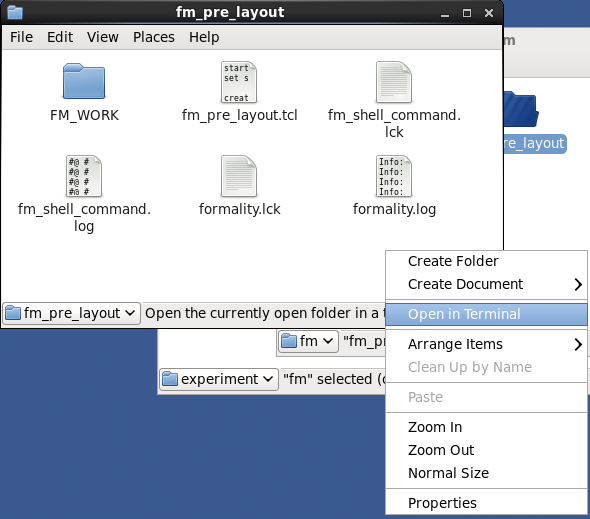

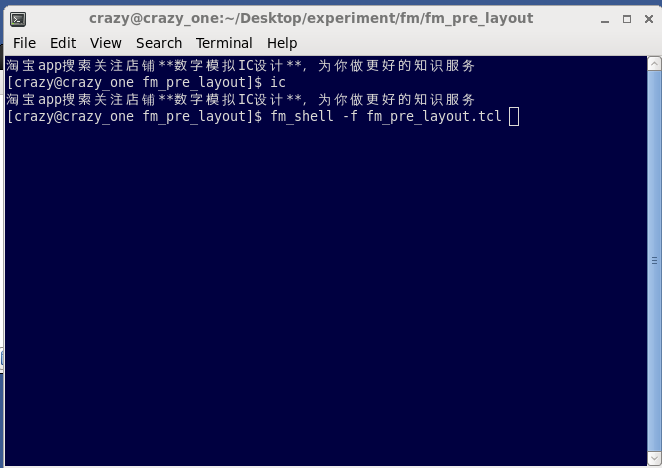

1.打开虚拟机,在/home/crazy/Desktop/experiment/fm/fm_pre_layout 下右键Open in terminal

2.在terminal中依次输入

ic

fm_shell -f fm_pre_layout.tcl

执行TCL脚本

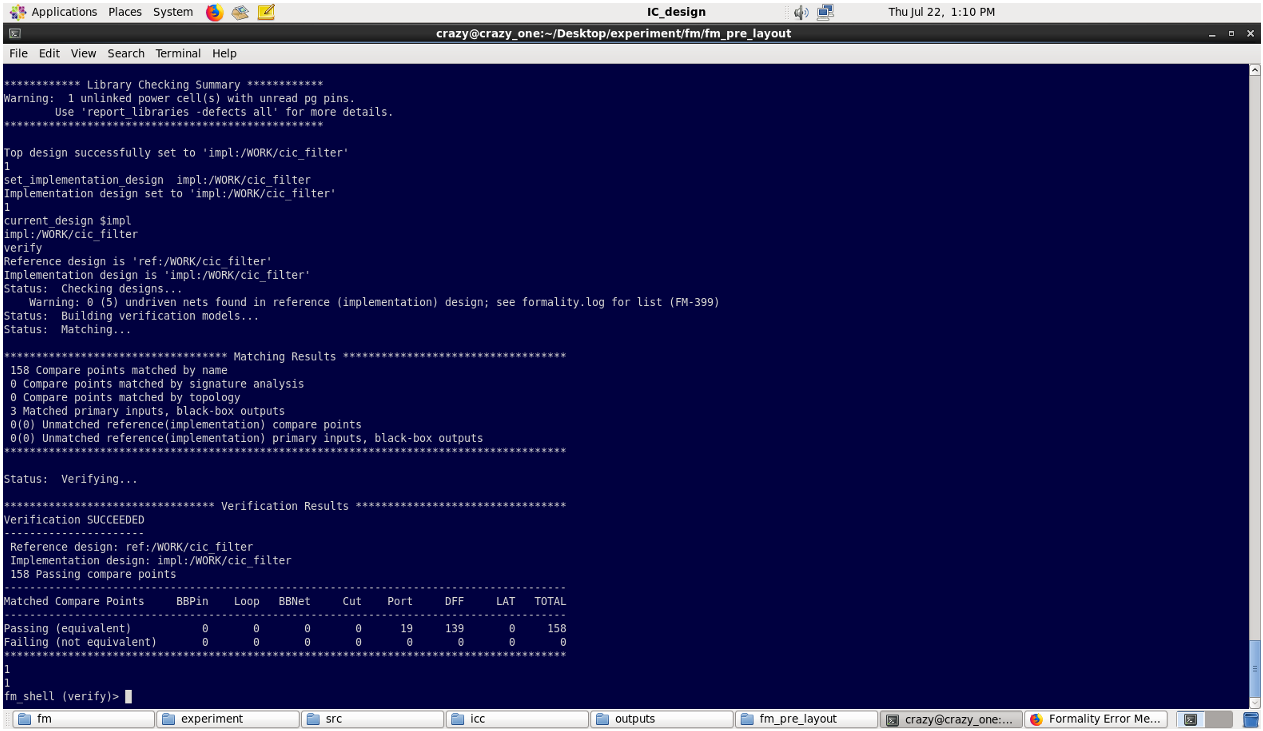

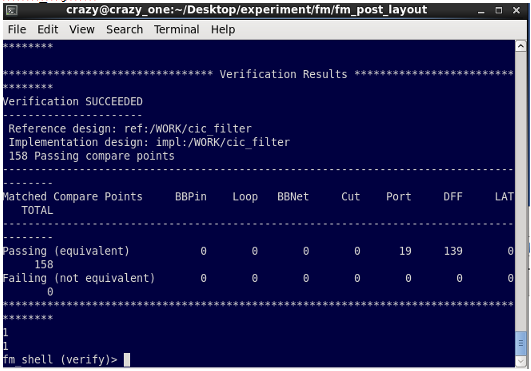

3.检查结果是否存在报错(如果出错会terminal中会打印0并输出报错信息),如果存在报错则根据报错信息返回修改脚本,或修改Verilog并重新进行DC综合

4.同理至/home/crazy/Desktop/experiment/fm/fm_post_layout下运行脚本并观察结果,如果出现报错则返回修改脚本或重新进行ICC布局布线步骤

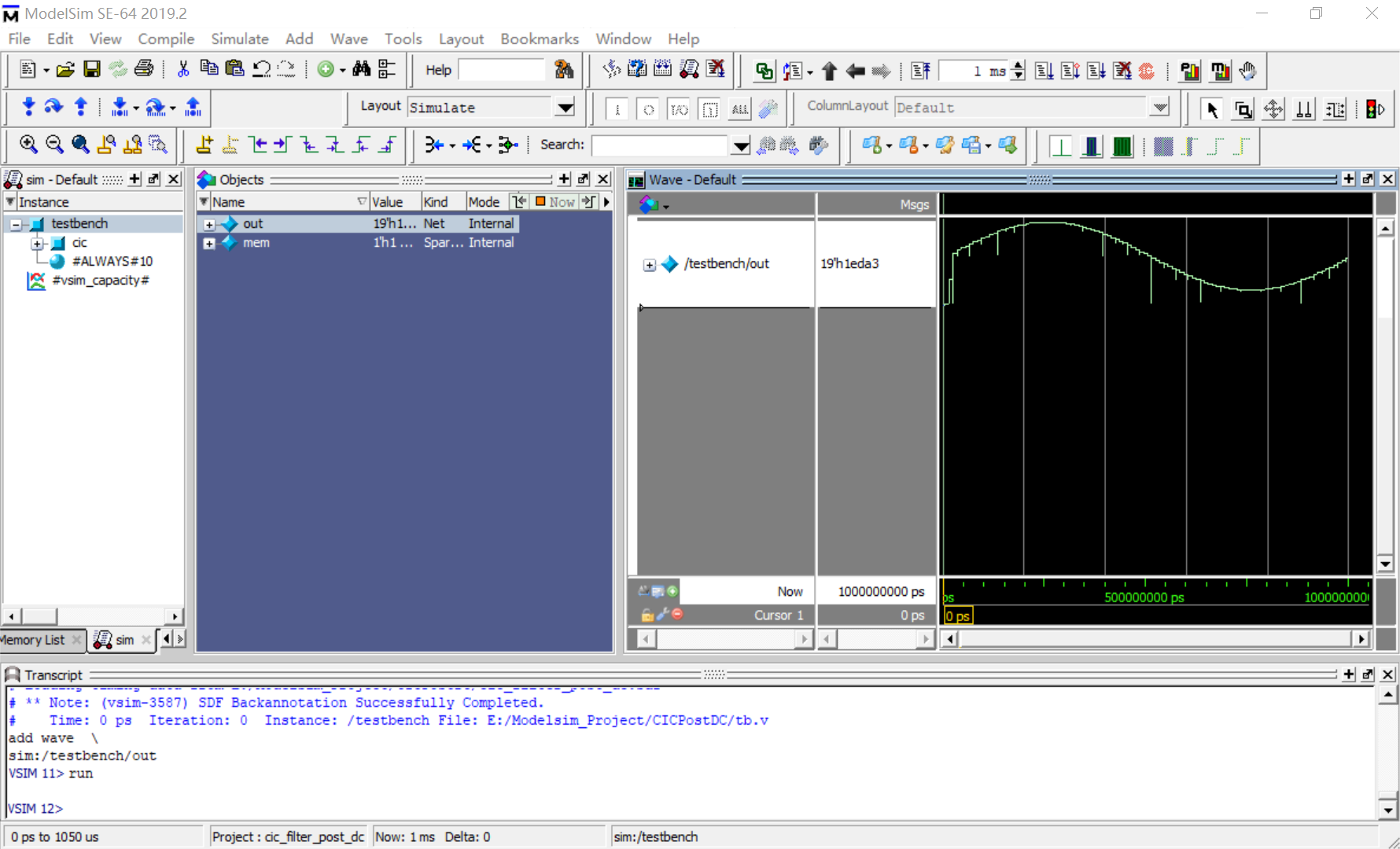

3.后仿真

现开始进行Modelsim后仿真,对Modelsim操作不熟悉的可以参考第三章的前仿真流程。

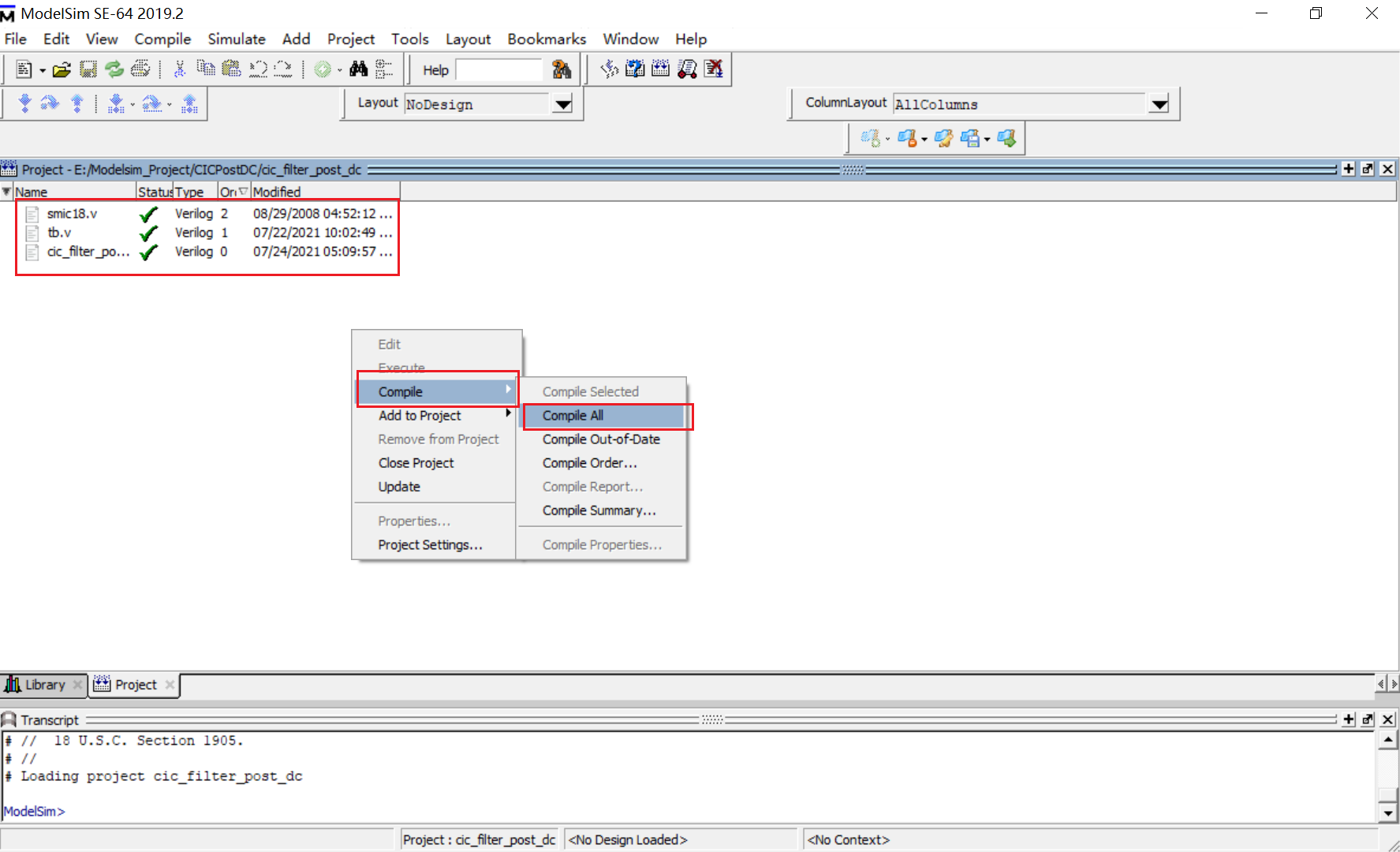

1.新建Modelsim工程,并将ICC布局布线后导出的门极网表、ICC布局布线后导出的时序描述文件、前仿真所使用testbench、代工厂提供的smic18.v拷贝到工程目录下

2.将门极网表,testbench,smic18.v导入到Modelsim中并编译

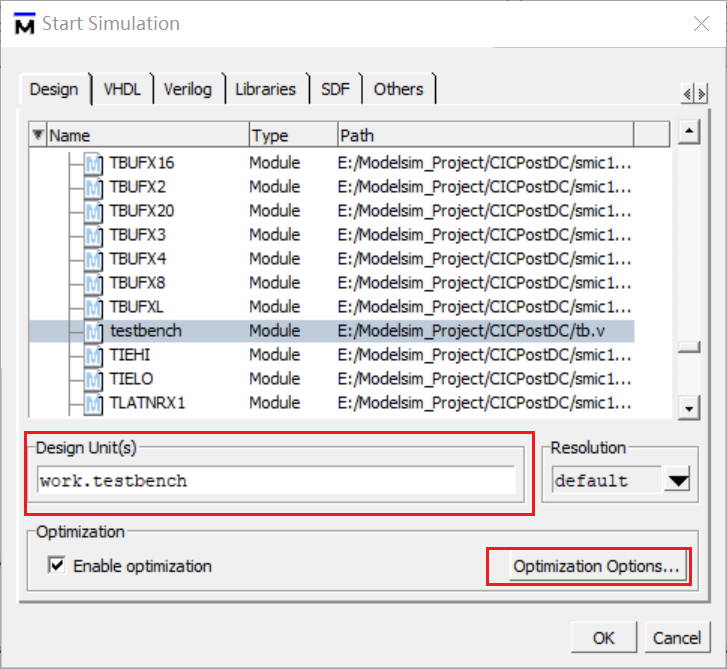

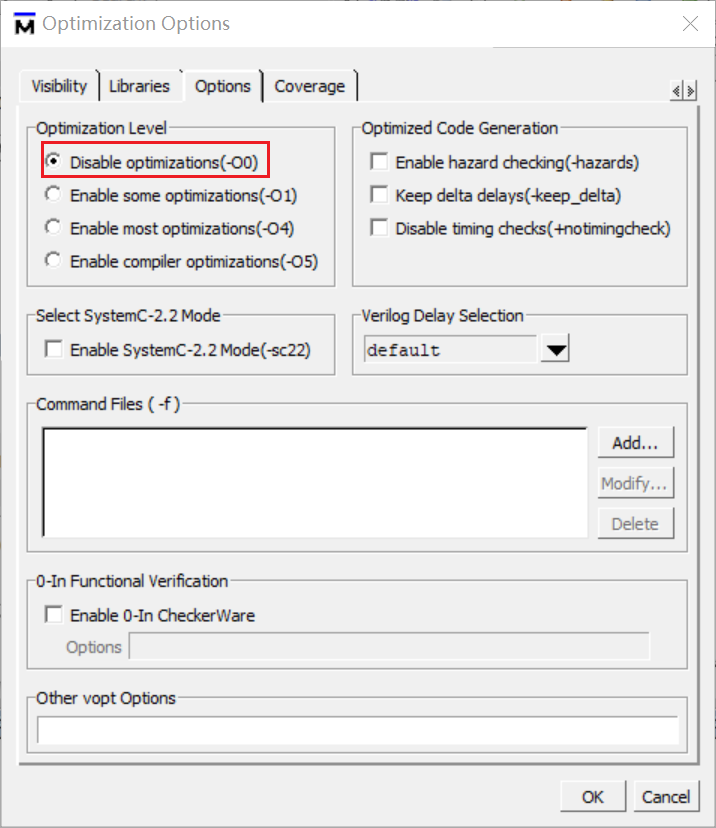

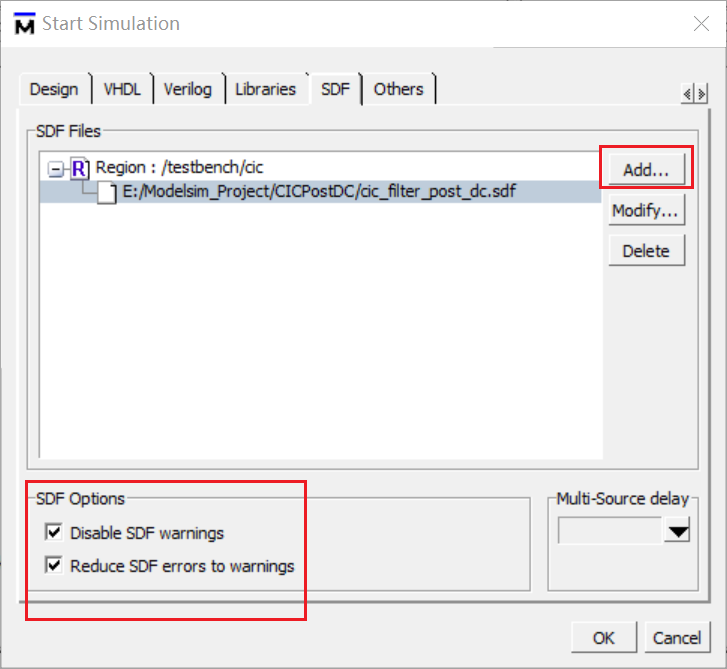

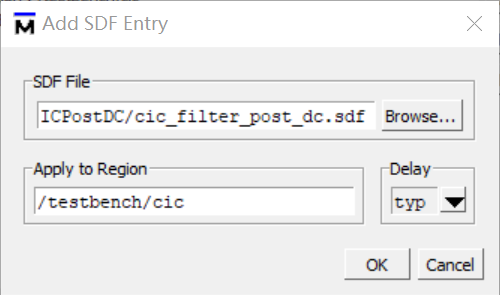

3.Simulate ----> Start Simulation,在Design标签下,展开work后选中testbench,在Optimization Options标签的Options表情下选择Disable optimizations(-O0)。接着,在SDF标签下点击Add,添加时序描述(.sdf)文件,并在Apply to Region中填写/testbench/cic,最后在SDF Options中勾选两个选项

4.开始仿真,将Out信号添加到Wave窗口观察,可以看到量化后的正弦波信号,说明布局布线后的电路功能正确。由于实际工艺的非理想性,对比前仿真的波形可以在后仿波形中看到明显的毛刺

至此后仿真完成。数字asic流程实验全部结束,感谢你的阅读。

4.参考资料

《PrimeTime User Guide》

https://www.jianshu.com/p/7eac9841f814

https://blog.csdn.net/weixin_43755290/article/details/105097210

浙公网安备 33010602011771号

浙公网安备 33010602011771号