TMS320F28002x——中断详解

中断概念

中断是指MCU处理程序运行中出现的“紧急事件”的整个过程,程序运行过程中,系统外部、系统内部或者现行程序本身若出现紧急事件,MCU立即终止现行程序的运行,自动转入相应的处理程序——中断服务程序,待处理完成后,再返回原来的程序运行,整个过程为程序中断。

中断可分为可屏蔽中断和不可屏蔽中断:可由程序控制其屏蔽的中断称为可屏蔽中断,屏蔽时,MCU将不接受中断(不进入中断服务程序);不能由程序控制其屏蔽的,MCU一定要立即处理的中断为不可屏蔽中断。

外设中断

中断架构

C28x内核CPU拥有14个外设中断线。其中两个(INT13和INT14)分别直接连接到CPU timer1 和timer2。剩余12个外设中断线通过ePIE模块(enhanced Peripheral Interrupt Expansion module)与CPU连接。每一根连接到CPU的外设中断线最多能接16个外设中断。

中断路径分3个阶段——外设、ePIE以及CPU。每个阶段都有其中断使能和标志寄存器。如下图所示:

外设阶段

一些外设允许多个不同的事件触发相同的中断信号。如:通信外设可能使用相同的中断来指示数据已经被接收或存在传输错误。中断生成的原因可以通过读取外设的状态寄存器进行确定,通常在生成另一个中断之前,需要手动清除状态寄存器。

PIE阶段

PIE为每个外设中断信号提供单独的标志和使能寄存器位,会根据相关的CPU中断进行分组。每个PIE组有一个16位使能寄存器(PIEIERx)、一个16bit标志寄存器(PIEFIRx)和一个1bit确认寄存器(PIACK)。

当CPU接收到中断时,CPU从PIE获取ISR的地址。PIE返回中断向量表中标志位已经置位并且编号最低的通道,这样当多个中断标志置位时,能够保证更高优先级的中断能被相应。

CPU阶段

与PIE一样,CPU为每个中断提供标志和使能寄存器位,使能寄存器(IER)和标志寄存器(IFR)。这两个寄存器都是内部CPU寄存器。在ST1寄存器中的INTM位,是一个全局的中断掩码,可以使用CPU的SETC和CLRC指令来进行置位和清除。在C代码中,一般使用DINT和EINT来实现。

中断输入顺序

下图展示了外设中断如何传输到CPU的过程:

当外设生成一个中断信号时(假设是PIE group x,channel y),它会触发以下事件序列:

①PIEIFRx.y位置1;

②如果PIEIERx.y位为1,中断传递到下一步

③如果PIEACK.x位为0,中断传递到下一步并且PIEACK.x置1

④IFR.x位置1

⑤如果IER.x位为1,中断传递到下一步

⑥如果INTM位0,CPU接收中断。

⑦在Data-read Data bus上的指令或者后续流程的指令都会被完整执行

⑧CPU在栈中保存中断跳转现场

⑨IFR.x和IER.x被清零,INTM被置位,EALLOW被清零

⑩CPU从PIE获取ISR中断向量,PIEIFRx.y被清零

⑪CPU执行ISR分支

最小的中断延迟时间是14个SYSCLK周期,等待ISR的置位和栈内存会增加延迟的时间。

初始化和使用中断

芯片刚上电时,默认不会使能任何的中断。PIEIER寄存器和IER寄存器都是默认值,INTM置位1。应用代码负责配置和使能所有外设的中断。

使能中断

使能外设中断,需要有以下几个步骤:

①禁能全局中断(DINT或SETC INTM)

②设置PIECTRL寄存器的ENPIE位,使能PIE

③将中断的ISR向量写入PIE向量表中

④设置合适的PIIERx位

⑤设置CPU的IER位

⑥使能外设对应的中断

⑦使能全局中断(EINT或CLRC INTM)

中断处理

中断处理函数与普通功能函数一样,但必须要有以下几步:

①有必要的话保存和恢复某些CPU寄存器的状态

②清除中断group中的PIEACK位

③使用IRET指令返回

步骤①与③如果函数使用了__interrupt关键字,会被编译器自动添加处理。PIEADCK位需要在代码中手动清除,一般在中断处理函数完成后执行。

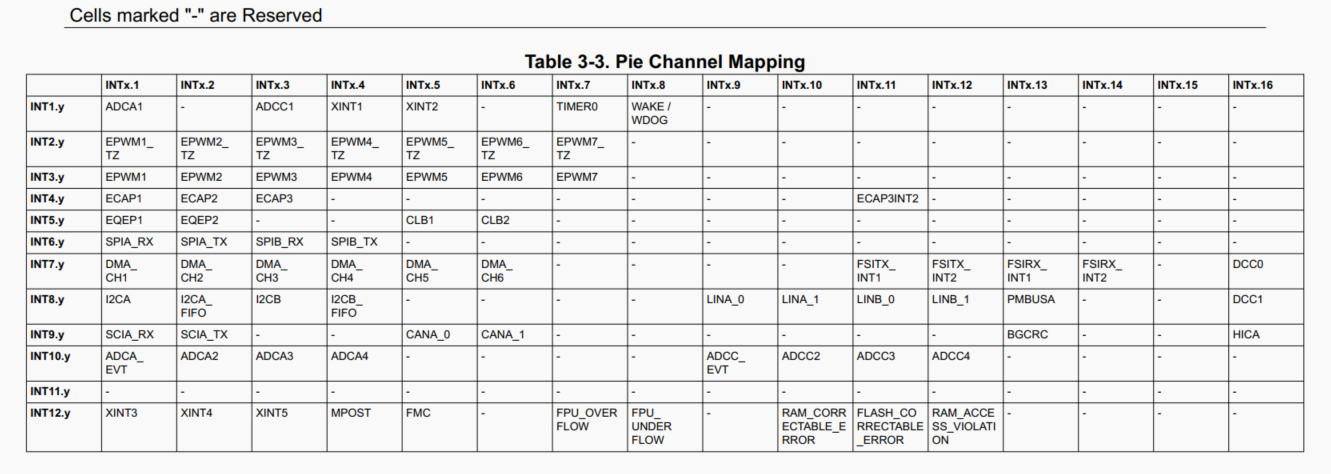

PIE channel映射

下表为PIE group和channel在每个中断的映射表:

异常与不可屏蔽中断

初始化和使用NMI

传入的NMI会在NMIFLG寄存器中设置一个标志位,并启动NMI看门狗计数器。计数器的时钟由SYSCLK提供,如果计数器计数值到达NMIWDPRD寄存器的值后,计数器会触发一个NMI看门狗复位信号(NMIWDRS)。为了避免这个信号产生,NMI处理函数必须使用NMIFLGCLR寄存器清除NMIFLG标志位。

NMI源

Missing Clock Detection

时钟丢失检测管理OSCCLK是否异常。如果OSCCLK的时钟源停止,PLL会被旁路,OSCCLK被连接到INTOSC1,并且NMI传递到CPU。

RAM ECC错误

RAM读取时单bit校验错误和双bit ECC数据错误或者单bit ECC地址错误都会触发NMI。

FLASH ECC错误

FLASH读取时双bit ECC错误或单bit ECC地址错误都会触发NMI。

CPU HWBIST错误

芯片自带的模块检测到CPU存在故障,触发NMI。

Software-Forced 错误

在NMIFLGFRC寄存器中置位SWERR可以通过软件强制触发NMI。

浙公网安备 33010602011771号

浙公网安备 33010602011771号