TMS320F28002x——时钟树详解

时钟源

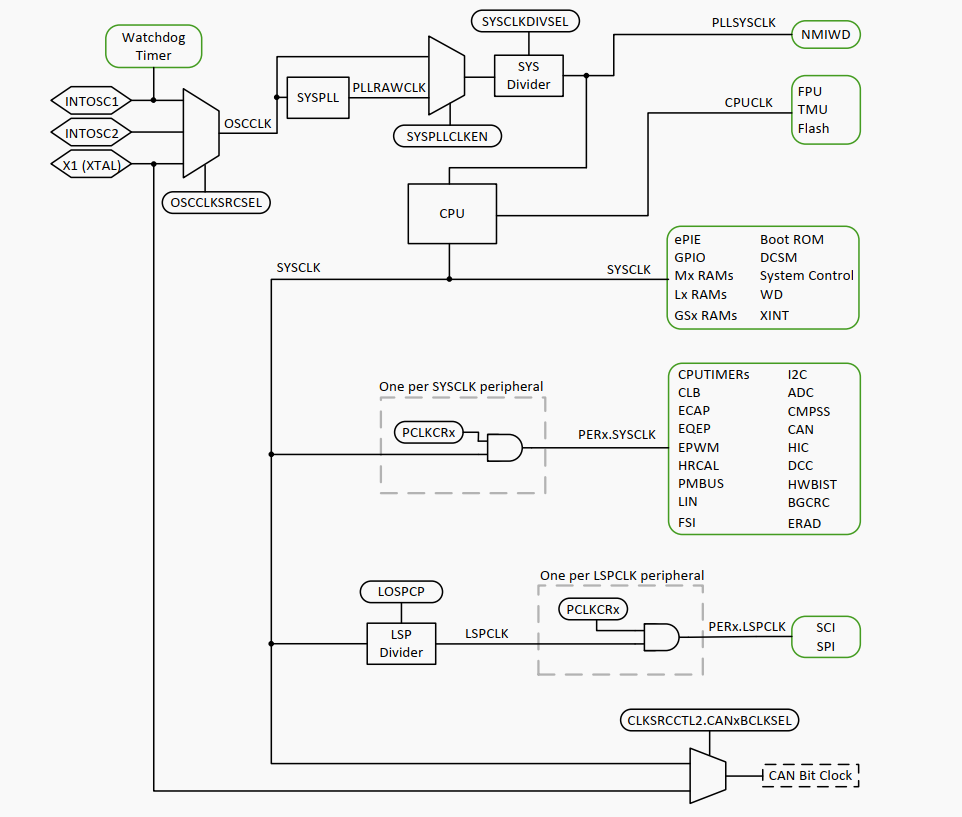

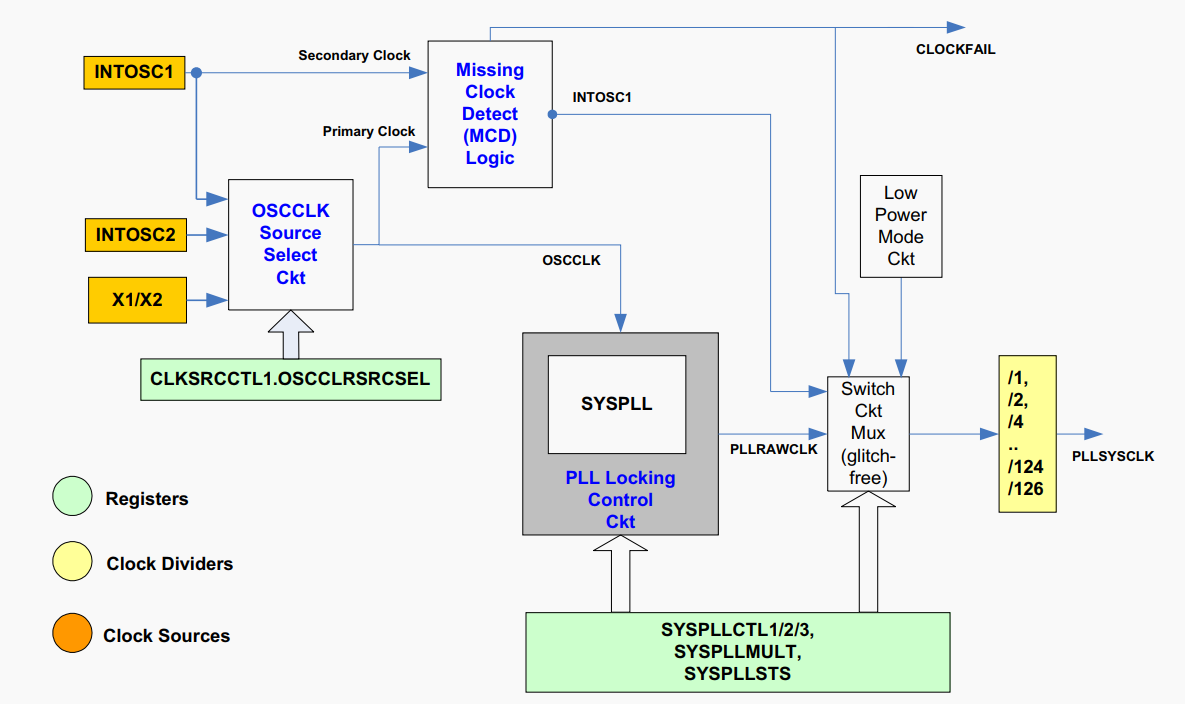

芯片中涉及到的所有时钟都通过四个时钟源之一来提供。芯片的时钟树如下图所示:

主要内部晶振1(INTOSC2)

上电的时候,由10MHz内部晶振(INTOSC2)进行锁频。INTOSC2是主要的内部晶振源,是系统在复位时默认的系统时钟。一般用在boot ROM和应用的系统时钟源。

需要注意:INTOSC2的精度不能满足CAN应用的要求,所以在使用CAN模块的时候,需要使用外部晶振。当INTOSC2作为系统时钟源时,GPIO19和GPIO18可以被用作GPIO引脚。

备用内部晶振2(INTOSC1)

备用内部晶振INTOSC1也是芯片内置的10MHz晶振。主要用在看门狗的时钟源或丢失时钟检测电路(MCD)后的时钟源。如果MCD功能使能,并且系统时钟无法被检测到,系统PLL会被旁路并且所有系统时钟都会自动连接到INTOSC1。若有debug需要,也可手动切换INTOSC1为系统时钟源。

外部晶振(XTAL)

芯片支持一个外部时钟源(XTAL),可以用作系统时钟源和CAN模块的时钟源。外部时钟源使用GPIO19和GPIO18两个引脚。

芯片支持3种类型的外部晶振:

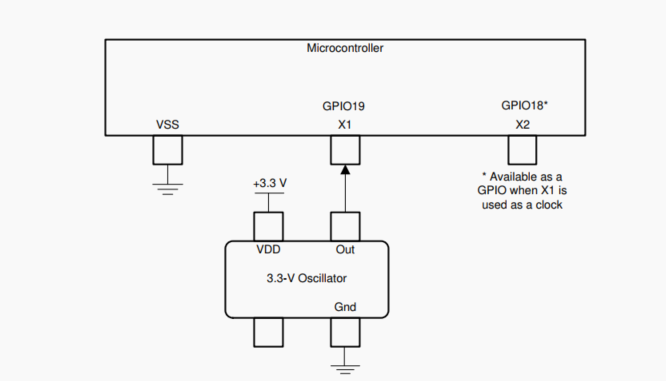

①单端3.3V外部晶振。时钟信号应该连接芯片的X1引脚(GPIO19),如下图所示:

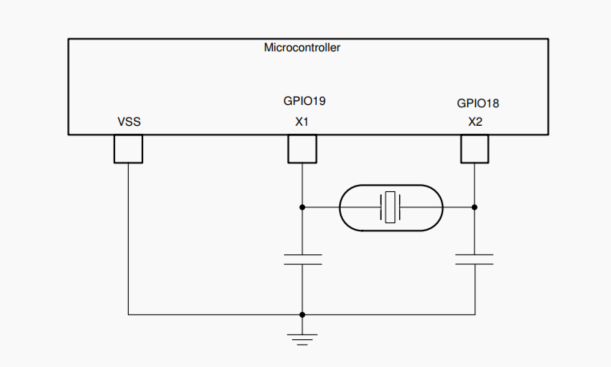

②外部晶振。时钟信号分别连接芯片的X1(GPIO19)和X2(GPIO18)引脚,通过电容与芯片的VSS引脚接地相连,如下图所示:

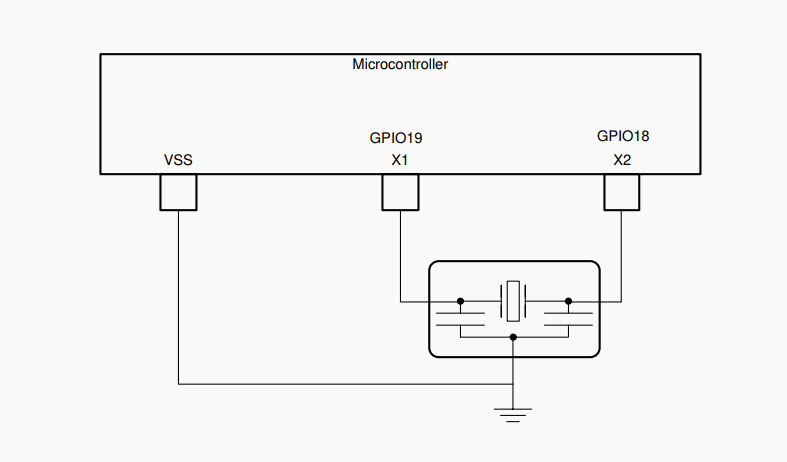

③自带电容的外部晶振。时钟信号分别连接芯片的X1(GPIO19)和X2(GPIO18)引脚,与芯片的VSS引脚接地相连,如下图所示:

派生时钟

上述的时钟源可以通过倍频(PLL)并向下进行不同的分频产生应用程序所需要的时钟频率。

OSCCLK

INTOSC2,XTAL或者INTOSC1三个之一需要被选择作为OSCCLK的时钟源,用作CPU和大部分外设的时钟。OSCCLK可以被直接使用,或通过系统倍频后使用,以达到更高的频率。复位的时候,OSCCLK是默认的系统时钟,并连接到INTOSC2。

PLLRAWCLK

系统PLL允许设备在其最大额定工作频率下工作,并且在多数的应用中作为主系统时钟。系统PLL以OSCCLK作为参考,PLLRAWCLK输出的时钟频率是VCO的倍频,如下图所示:

芯片时钟域

芯片时钟域向芯片的不同模块的时钟提供输入。它们通过直接或除法器导出后连接。

PLLSYSCLK

NMI看门狗定时器有独立的时钟域——PLLSYSCLK。它可以连接到系统PLL(PLLRAWCLK)或OSCCLK。所选的时钟源通过分频器,使用SYSCLKDIVSEL寄存器配置。

CPUCLK

CPUCLK用于CPU内核FPU,TMU以及FLASH模块。这个时钟和PLLSYSCLK时钟频率相同,当CPU进入IDLE,STANDBY或HALT模式后选通。

SYSCLK与PREx.SYSCLK

SYSCLK为专用RAM(M0、M1),本地共享RAM(LS4到LS7),全区共享RAM(GS0),boot ROM以及其他外设提供时钟。时钟频率与PLLSYSCLK时钟频率相同,当CPU进入HALT或STANDBY模式后选通。

每个外设时钟有独立的时钟门控,由PCLKCRx寄存器控制。

LSPCLK与PERx.LSPCLK

SCI和SPI模块可以使用低速时钟,以较慢的波特率进行通信。两个模块连接到共享时钟分频器(通过SYSCLK生成低速外设时钟)。LSPCLK默认使用1/4除法器,可以通过LOSPCP寄存器进行修改。每个SCI和SPI模块的时钟可以通过PCLKCRx寄存器配置独立选通。

CAN时钟

由于CAN时钟对时钟精度要求比较高,波特率的精度取决于未定时设置和网络设置,需要精确到0.1%。CAN时钟一般有外部晶振提供,并且时钟频率必须小于或等于SYSCLK频率。

时钟丢失检测

使用MCD(missing clock detection)可以实现系统时钟的安全检测。

|

时钟丢失检测功能 |

可被检测时钟 |

检测频率 |

使用限制 |

|

MCD |

INTOSC2、XTAL/X1 |

8192 INTOSC1 cycles |

不能检测INTOSC1 |

MCD使用INTOSC1作为参考时钟来检测OSCCLK的时钟故障,该功能只能检测OSCCLK的完全丢失,不能检测OSCCLK的时钟频率漂移。

INTOSC1作为备用时钟提供10MHz频率检测OSCCLK:

①OSCCLK时钟保持MCDPCNT这个7位计数器计数。该计数器与XRSn异步复位。

②INTOSC1时钟保持MCDSCNT这个13位计数器计数。该计数器与XRSn异步复位。

③每当MCDPCNT溢出时,MCDSCNT计数器被复位。所以只要OSCCLK时钟存在或不比INTOSC1时钟频率的64倍慢,MCDSCNT就不会溢出。

④若OSCKCLK由于某种原因停止或比INTOSC1慢至少64倍,MCDSCNT溢出,OSCCLK时钟丢失条件满足。

⑤上述的检测连续有效,除非MCD功能被禁用。

⑥如果MCD检测到时钟丢失:MCDSTS标志位置位;MCDSCNT计数器停止计数,防止下一次的时钟丢失检测;CLOCKFAIL信号置1,向PWM模块生成TRIP事件,并触发CPU1.NMIWD;PLL被强制旁路,OSCCLK源切换到INTOSC1;SYSPLLMUL.IMULT清零;当MCDSTS位被设置时,OSCCLKSRCSEL位不起作用,并且OSCCLK被强制

连接到INTOSC1;进入系统的PLLRAWCLK自动切换到INTOSC1。

浙公网安备 33010602011771号

浙公网安备 33010602011771号