在一块板子上,实现两个RapidIO IP核遇到的问题

问题描述:

[Place 30-140] Unroutable Placement! A GTXE_COMMON / GTXE_CHANNEL clock component pair is not placed in a routable site pair. The GTXE_COMMON component can use the dedicated path between the GTXE_COMMON and the GTXE_CHANNEL if both are placed in the same clock region. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets gtx1/srio_gen2_0/inst/k7_v7_gtxe2_common_inst/gt0_qpll_clk_out] >

gtx1/srio_gen2_0/inst/k7_v7_gtxe2_common_inst/gtxe2_common_0_i (GTXE2_COMMON.QPLLOUTCLK) is provisionally placed by clockplacer on GTXE2_COMMON_X0Y1

gtx1/srio_gen2_0/inst/srio_gen2_0_block_inst/srio_gt_wrapper_inst/inst/srio_gen2_0_i/gt0_srio_gen2_0_i/gtxe2_i (GTXE2_CHANNEL.QPLLCLK) is locked to GTXE2_CHANNEL_X0Y8

The above error could possibly be related to other connected instances. Following is a list of

all the related clock rules and their respective instances.

Clock Rule: rule_bufds_bufg

Status: PASS

Rule Description: A BUFDS driving a BUFG must be placed on the same half side (top/bottom) of the device

gtx1/srio_gen2_0/inst/srio_clk_inst/u_refclk_ibufds (IBUFDS_GTE2.O) is locked to IBUFDS_GTE2_X0Y5

gtx1/srio_gen2_0/inst/srio_clk_inst/refclk_bufg_inst (BUFG.I) is provisionally placed by clockplacer on BUFGCTRL_X0Y30

Clock Rule: rule_bufds_gtxchannel_intelligent_pin

Status: PASS

Rule Description: A BUFDS driving a GTXChannel must both be placed in the same or adjacent clock region

(top/bottom)

gtx1/srio_gen2_0/inst/srio_clk_inst/u_refclk_ibufds (IBUFDS_GTE2.O) is locked to IBUFDS_GTE2_X0Y5

gtx1/srio_gen2_0/inst/srio_gen2_0_block_inst/srio_gt_wrapper_inst/inst/srio_gen2_0_i/gt0_srio_gen2_0_i/gtxe2_i (GTXE2_CHANNEL.GTREFCLK0) is locked to GTXE2_CHANNEL_X0Y8

Clock Rule: rule_bufds_gtxcommon_intelligent_pin

Status: PASS

Rule Description: A BUFDS driving a GTXCommon must both be placed in the same or adjacent clock region

(top/bottom)

gtx1/srio_gen2_0/inst/srio_clk_inst/u_refclk_ibufds (IBUFDS_GTE2.O) is locked to IBUFDS_GTE2_X0Y5

and gtx1/srio_gen2_0/inst/k7_v7_gtxe2_common_inst/gtxe2_common_0_i (GTXE2_COMMON.GTREFCLK0) is provisionally placed by clockplacer on GTXE2_COMMON_X0Y1

出错原因:

同一个quad中重复使用GTXE_COMMON的问题

在进行例化时,两个相同的RapidIO IP核产生了GTCOMMON,相当于在物理层面只有一个GTCOMMON,但是在程序中却同时使用,因此产生了错误;

解决方法:

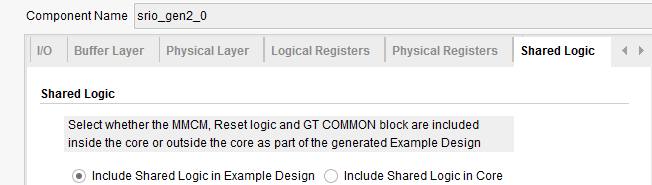

在生成srio_gen2 IP核时,勾选include shared logic in example design,将common、clk、rst等文件作为公共文件使用,这样就可以正常使用了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号