网络控制芯片AX88796B系列使用简介

AX88796B是一款针对嵌入式及工业以太网应用的低引脚数(LQFP-64) Non-PCI以太网控制芯片。AX88796B采用符合业界标准的8/16位SRAM-like主机接口,可与一般8/16/32位微控制器直接连接,无须任何外部逻辑线路。该组件内建符合IEEE 802.3/ IEEE 802.3u协议的10/100Mbps以太网物理层(PHY)及媒体存取控制器(MAC),整合8K*16位SRAM网络封包缓存器,以高效率的方式进行封包的储存、检索与修改。AX88796广泛支持各项规格包括双绞线正反接线自动校正(HP Auto-MDIX)、网络唤醒、低功耗管理及IEEE 802.3x/ backpressure流量控制。

项目需要用以太网进行数据传输,所以用到FPGA对AX88796B进行驱动。

1. 特性

- Non-PCI

- 8/16位SRAM-like主机接口,完全兼容NE2000

- MAC+PHY

- IEEE 802.3/ IEEE 802.3u,10/100Mbps

- 8k x 16位 SRAM

值得注意的是该芯片“完全兼容NE2000”,NE2000是什么呢,简单的说就是网卡标准。我们电脑网卡里面大多用的是Realtek(瑞昱)公司的芯片,所以在在学习过程中可以参考瑞昱的网络控制器芯片资料,如RTL8019.

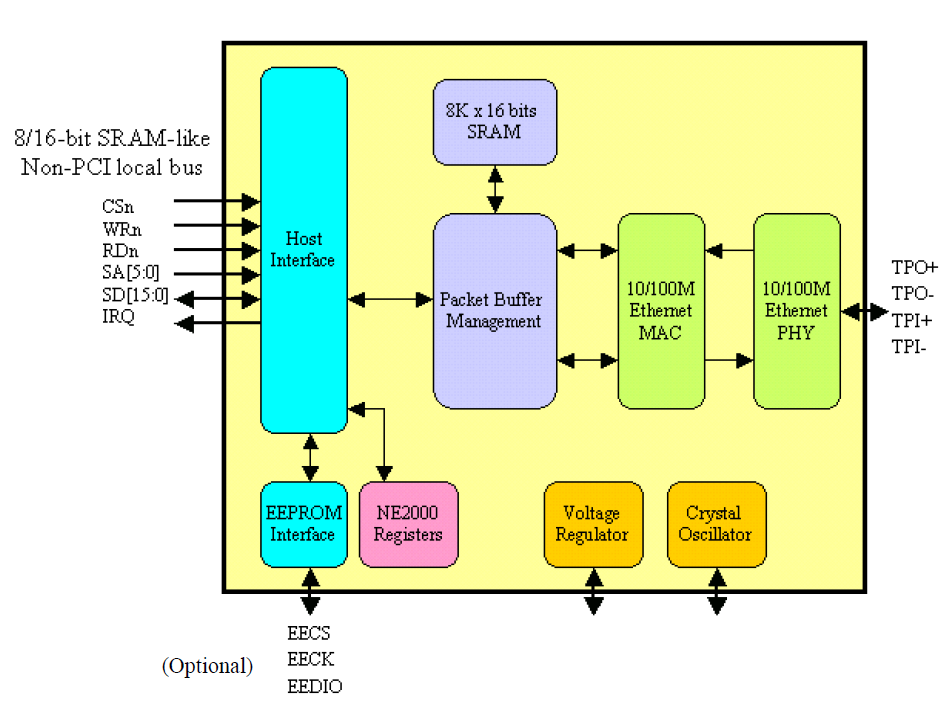

2. 结构框图

从框图中可以看到芯片集成了MAC和PHY,其工作方式可以简单的理解为用户通过Non-PCI local bus对芯片进行寄存器配置(主要是NE2000 Register),使芯片按照用户定义的方式进行工作。内部Packet Buffer Management对收发的数据包进行控制和管理(仲裁)。8k x 16bitsSRAM用户数据缓存。

关于芯片的基本配置,这里不再赘述,处理参考芯片的Datasheet外,还可以参考《AX88x96B_Software_Programming_Guide_v251》。下面着重说一下,关于芯片收发过程中对环形缓存的理解。

3. 接收

3.1 缓存空间

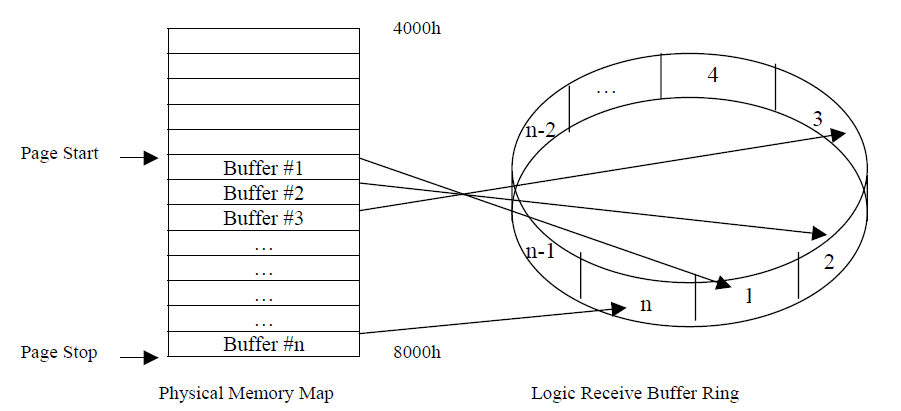

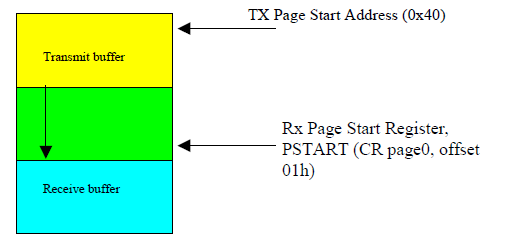

网卡含有16K字节的RAM,地址为0x4000-0x7fff,芯片将这些空间按256字节分成一个个buffer(或称一页),所以共有64 页。页的地址就是地址的高8位,页地址为0x40-0x7f。这16K的RAM一部分用来存放接收的数据包,一部分用来存储待发送的数据包。这么分的原因是以太网包大小是64 bytes ~1522 bytes之间,这样可以充分利用空间。

在网络传输中,对以太网包的接收缓存的协调是靠一个叫Buffer Management Logic内部模块控制,主要功能是:

- 按包拼接长的数据;

- 如果一包数据不完整或出问题,AX88x96B将拒绝接收,从而释放相关包占用的空间;

- 不断的计算包空间大小和控制指针,即多少包进来,多少包读走。

其中第三点应该是关注的重点。

3.2 Receiver Buffer Ring

Receiver Buffer Ring是对缓存机制理解的重点部分。16k RAM空间会有一部分用做接收缓存。接收空间大小用寄存器the Page Start Address Register (PSTART) 和 the Page Stop Address Register (PSTOP) 来定义,二者的值是空间也地址,即0x40-0x7f。缓存的时候,当DMA地址等于PSTOP所存的地址时,DMA又会从PSTART开始,如图所示就形成了一种环形结构。

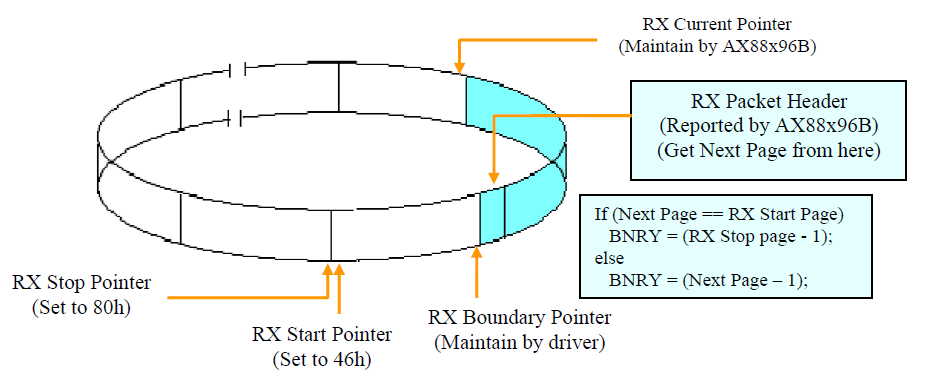

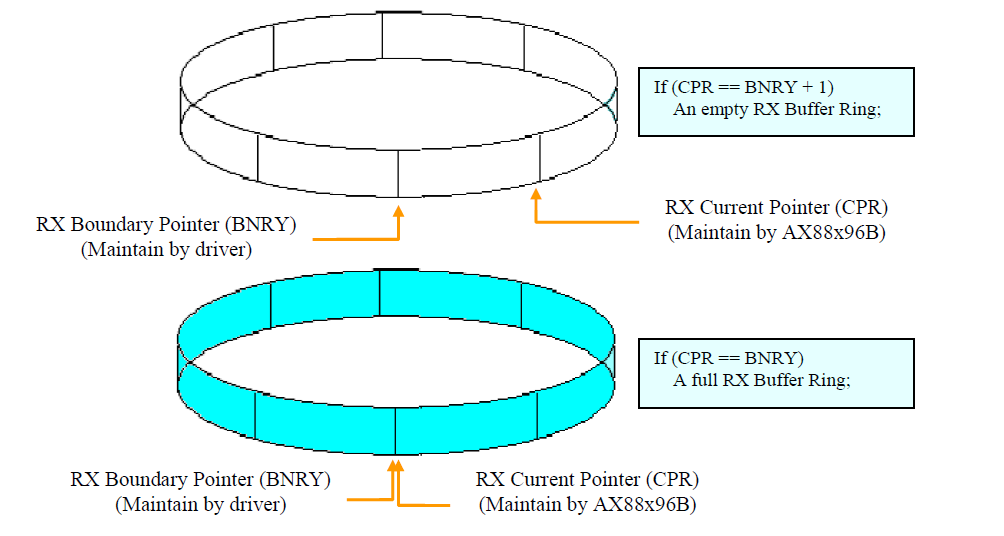

同时,要在缓存中完成正确的包的接收并且被主机读取,还需要两个动态指针,即The Current Page Register和The Boundary Register。简单理解,The Current Page Register是写指针(指包被写入进Receiver Buffer Ring),而 The Boundary Register是读指针。初始化状态下,Page Start Register、The Current Page Register和The Boundary Register均指向同一个地址的buffer。

3.3 接收机制

芯片在接收过程中,收到一包数据,通过DMA转给环形存储器,The Current Page Register存的地址就递增1(完整数据可能是多包)。The Boundary Register存的地址是还未被读走数据的地址,主机从环形存储器中读走一包,则The Boundary Register存的地址递增1.

在接收过程中,the Buffer Management Logic会进行两次比较。第一次比较存有DMA地址的下一个buffer的地址和the Page Stop Register中的值,如果两者相等,说明环形存储器存了”一圈“了,the buffer management logic会将DMA的地址存入Page Start Address Register指向的buffer中。第二次比较存有DMA地址的下一个buffer的地址和the Boundary Pointer Register指向buffer的地址,如果两者相等,则忽略下一包,因为表明之前的包还没读走,防止覆盖数据。

开始接收时,先获取包头4个字节的信息主要是NextPage地址和数据长度,分低、高两个字节。

4. 发送

发送过程相对要简单一些。16k 的RAM空间,前一部分用于发送缓存。其空间大小其实是由接收缓存的启示地址决定的,接收地址定了,剩余的部分就用作发送。

在发送过程中,主要控制的有三个寄存器:a Transmit Page Start Address Register (TPSR) and the Transmit Byte Count Registers (TBCR0, 1),即发送起始地址寄存器以及发送字节计数寄存器(包含两个寄存器来确定字节数的高低8位)。

在发送组帧过程中需要遵守相应的规定,可以参考手册。

5. 编程过程简要说明

5.1 初始化配置

芯片工作前,有上电复位,读取寄存器的软件复位,都操作一遍,注意时序要求。之后对工作类寄存器进行工作模式配置,然后有对上述决定收发缓存大小相关的寄存器进行配置。最后启动芯片开始工作。这部分可以在编程指南中找到。

如果配置正确,芯片就可以建立物理连接了。

5.2 接收

当芯片开始工作之后,根据需要就去读取The Current Page Register和The Boundary Register的值,从而判断有无数据接收。判断依据可以参考下图以及编程手册中的文字说明。

注意:编程过程中,先访问的是内部寄存器中当前的值来判读是否有接收数据,如果有,再往CR寄存器中写入0A,从而启动“读”,此后才可以从Data Port中读取有效数据。

5.3 发送

发送数据前,需要根据发送数据量来判断所需缓存空间。然后需要检查一些状态寄存器,如缓存空间大小、远端发送缓存空间或者发送命令队列是否full。之后才能将数据搬进缓存中。最后配置刚才提到的字节数等寄存器,并启动发送(发送前还有数据的搬移操作,即从缓存RAM中搬移至远端DMA)。

参考文献:

- 《AX88796BLF datasheet》;

- 《AX88x96B_Software_Programming_Guide_v251》;

- 《AX88796总结》(网络文档)

浙公网安备 33010602011771号

浙公网安备 33010602011771号