FPGA最小系统分析与电路设计

《FPGA最小系统分析与电路设计》

部分节选自《FPGA应用开发入门与典型.pdf 》

FPGA最小系统包括:FPGA芯片、下载电路、外部时钟、复位电路和电源。

如果使用NIOS II软嵌入式处理器还要包括SDRAM和Flash。

(1)配置管脚

MSEL[1..0]:用于选择配置模式,FPGA有多种配置模式,如主动、被动、

快速、正常、串行、并行等,以此管脚进行选择;

DATA0:FPGA串行数据输入,连接置配置芯片的串行数据输出管脚;

DCLK:FPGA串行时钟输出,为配置器件提供串行时钟;

nCSO(I/O):FPGA片选信号输出,连接至配置器件的nCS管脚;

ASDO(I/O):FPGA串行数据输出,连接至配置器件的ASDI管脚;

nCEO:下载链器件使能输出,在一条下载链种,当一个器件配置完成后,

此信号使能下一个器件开始进行配置。下载链的最后一个器件的nCEO应

悬空。

nCE:下载链器件使能输入,连接至上一个器件的nCEO,下载链的第一个

器件的nCE接地。

nCONFIG:用户配置模式起始信号;

nSTATUS:配置状态信号;

CONF_DONE:配置结束信号。

(2)电源引脚

VCCINT:内核电压,与工艺有关,例如130nm工艺为1.5V,90nm工艺为1.2V;

VCCIO:端口电压,一般为3.3V,也可以选择为5V、1.8V、1.5V;

VREF:参考电压;

GND:信号地。

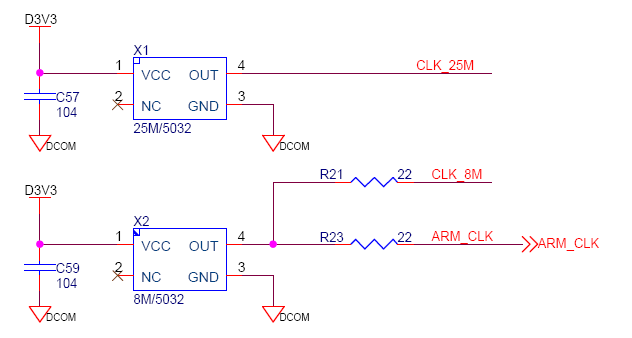

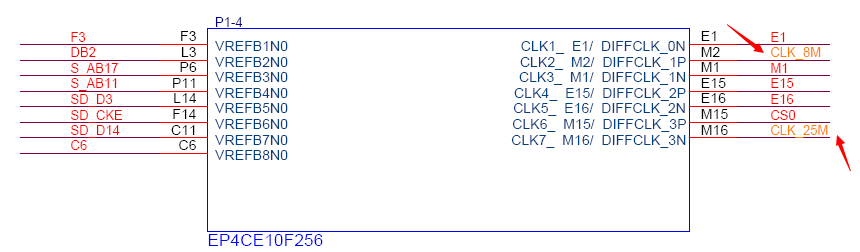

(4)时钟管脚

VCC_PLL:锁相环管脚电压,直接连VCCIO。

VCCA_PLL:锁相环模拟电压,一般通过滤波器连到VCCINT上。

GNDA_PLL:锁相环模拟地。

GNDD_PLL:锁相环数字地。

CLKnum(LVDSCLKnump):锁相环时钟输入,支持LVDS时钟输入,p接正端,num

表示PLL序号。

CLKnum(LVDSCLKnumn):锁相环时钟输入,支持LVDS时钟输入,n接负端,num

表示PLL序号。

PLLnum_OUTp(I/O):锁相环时钟输出,支持LVDS时钟输入,p接正端,num

表示PLL序号。

PLLnum_OUTn(I/O):锁相环时钟输出,支持LVDS时钟输入,n接正端,num

表示PLL序号。

(4)JTAG模式与AS模式

FPGA是SRAM型结构,本身不能固话程序。因此FPGA需要一片Flash结构的配置

芯片来存储逻辑配置信息,用于上电配置。

以Altera公司的FPGA为例,配置芯片分为串行(EPCSx系列)和并行(EPCx系列)

其中EPCx为老款配置芯片,体积大,价格高,现在常用EPCSx系列芯片。

JTAG模式是直接将程序下载到FPGA芯片上运行,可以无限擦写,AS模式是将程序

下载到编程配置芯片上,然后再配置FPGA。

(5)高速SDRAM

SDRAM可作为软嵌入式系统的(NIOS II)的程序运行空间,或者作为大量数据的缓

冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片

都是兼容的。

常用的有HY57V系列、三星K4S系列和美光MT48LC系列。

(6)电源设计:

AMS11117可以提供1A电流,线性电源(适用于144管脚以下、5万逻辑门以

下的FPGA)。

AS2830(或LT1085/6)可以提供3A电流,线性电源(适用于240管脚以下,

30万逻辑门以下的FPGA)。

TPS54350可以提供3A电流,开关电源(适用于大封装大规模的高端FPGA)。

(7)硬件调试方法

(1)先焊接电源部分,使用万用表测试,排除电源短路等情况后,上电测

试电压是否正确。

(2)然后焊接FPGA及其相关的下载电路,排除引脚粘连,再次测了电源地

之间是否有短路现象,上电测试电压是否正确,然后将手排除静电后触摸

FPGA有无发烫现象。如果出现FPGA发烫现象,一般是出现总线冲突的现象。

这种情况下需要检查外围总线是否出现竞争问题,通常是多片存储器片选

信号同时选通造成。

(3)以上步骤通过后,连接JTAG,上电运行,打开Quartus II,并打开

Programmer,点击Auto DEtect看能否检测到FPGA。

(4)焊接时钟电路、复位电路,并向FPGA下载一个程序,检查是否正常工作。

普及下 来自网友COM张 http://group.chinaaet.com/116/5263

刚学FPGA,谁能给俺解释一下SDRAM ,SRAM ,FLASH在FPGA中起的作用?最好能详细点~谢谢啦

在FPGA开发板上除了内部onchip memory,都有几种不同的存储器,比如SDRAM,SRAM,FLASH,EPCS。

1.EPCS

FPGA只是一个装载软核配置信息的一个工具,它是基于SRAM的查找表,上电的时候需要重新配置,因此一定需要一个配置芯片。一般来说Altera公司Cyclone或者CycloneII系列FPGA相应的配置器件会选择EPCS系列串行FLASH。一般使用AS模式下载EPCS系列器件。但有时候可能遇到AS模式不能成功下载的案例,原理图以及PCB板都是按照推荐电路设计,这时候我们可以通过Flash Loader检验EPCS器件是否良好。即通过JTAG方式下载EPCS系列器件。如果这种方式还是不能进行正确的AS模式的下载的话,可能EPCS器件本身已经不能正常工作了,此时可以建议更换配置芯片了。

在AS模式下,由目标FPGA来主动输出控制和同步信号(包括配置始终)给Altera专用的串行配置芯片EPCS*。

2.FLASH

属于EEPROM(电擦除可编程只读存储器),一种不挥发性(Non-Volatile )内存,在没有电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘,这项特性正是闪存得以成为各类便携型数字设备的存储介质的基础。

在FPGA开发板中一般用来存储应用程序(C程序等)。用户可以将程序或用户数据烧写入Flash,可以通过NiosII IDE中提供的工具“Flash Programmer”来实现,非常方便,当然也可以自己写代码来将数据烧写入Flash。

3.SDRAM

SDRAM是多Bank结构,例如在一个具有两个Bank的SDRAM的模组中,其中一个Bank在进行预充电期间,另一个Bank却马上可以被读取,这样当进行一次读取后,又马上去读取已经预充电Bank的数据时,就无需等待而是可以直接读取了。这也就大大提高了存储器的访问速度。为了实现这个功能,SDRAM需要增加对多个Bank的管理,实现控制其中的Bank进行预充电。在一个具有两个以上Bank的SDRAM中,一般会多一根叫做BAn的引脚,用来实现在多个Bank之间的选择。在FPGA开发板中一般作为NIOS 处理器的RAM和程序运行空间。

4.SRAM

一个SRAM中的位单元通常由4~6只晶体管组成,利用双稳态触发器来保存信息,当这个位单元被赋予0或1的状态之后,它会保持这个状态直到下次被赋予新的状态,或者断电之后才会更改或消失。SRAM的速度相对比较快,而且比较省电,但是存储1位的信息需要4~6只晶体管,制造成本较高。

SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积。