FPGA-PLL模拟供电方案

Cyclone IV E FPGA器件中,PLL电路需要两种供电,分别为模拟部分和数字部分供电。

PLL数字部分供电电压为1.2V,可直接使用内核供电电源提供。当然,如果有更高要求,也可以给PLL数字部分单独设计电源。

PLL模拟部分仅需最大200mA的供电电流,不过由于是模拟电路,对电源稳定性要求较高,不能有较大的纹波。该供电适合使用LDO提供,例如使用LP5900SD-2.5器件,或者其他可选LDO(如AMS1117-2.5)。

PLL供电管脚根据每个器件实际具有的PLL数量而不同,主要就是EP4CE6和EP4CE10两个器件例外,由于这两个器件片上只有两个PLL,因此也只有两个PLL模拟供电脚和数字供电脚,其他容量的器件,都是4个PLL。

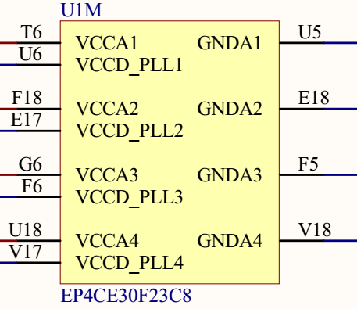

PLL模拟供电管脚在器件中被标注为VCCAx,数字供电管脚被标注为VCCD_PLLx。

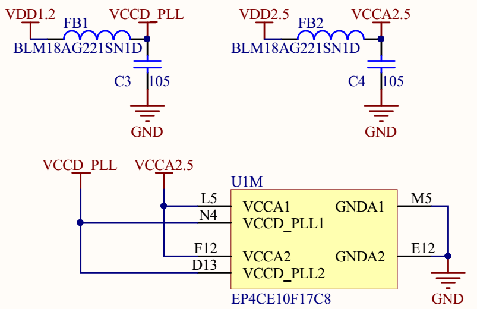

设计时,将VCCAx引脚连接到2.5V的PLL模拟供电专用电源上,VCCD_PLLx连接到1.2V内核供电上。

设计PLL电源时,最好设计磁珠+电容组成的滤波的电路,可以对电源质量进行进一步提升(理论依据等待填充)。

EP4CE10具有2个PLL的PLL供电引脚

EP4CE30具有4个PLL的PLL供电引脚

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 上周热点回顾(3.3-3.9)