FPGA使用DCDC设计内核供电方案笔记

使用DCDC电路,在提供更大输出电流的同时,可以提高电源转换电路效率,更加节能。

在设计时,可以使用NCP1529型专用DCDC降压器来设计该转换电路。

NCP1529输入电压范围为2.7V~5.5V,输出电压范围为0.9V~3.9V,可持续稳定的输出高达1A的电流。应对FPGA的内核功耗绰绰有余。

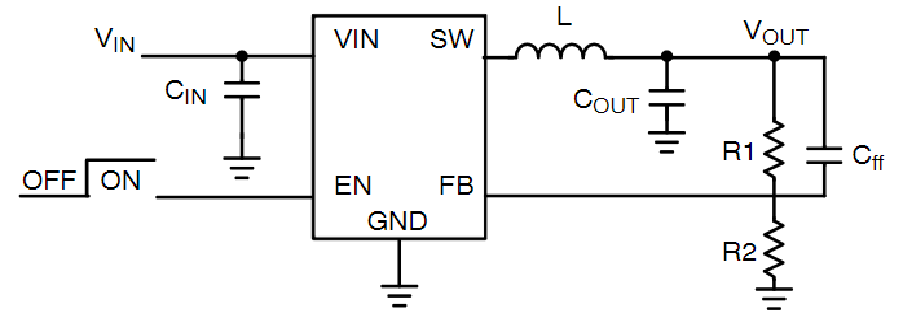

其输出电压可通过反馈电阻R1和R2不同的阻值组合来设置。

输出电压 V_out= V_FB × (1+R1/R2) 其中V_FB为反馈电压,固定为0.6V,为了实现低功耗和低噪声,要求R2的阻值大小在100K到600K之间(具体为啥暂时不清楚)。

当我们希望输出电压为1.2V时,只需选择R1和R2阻值相同即可。

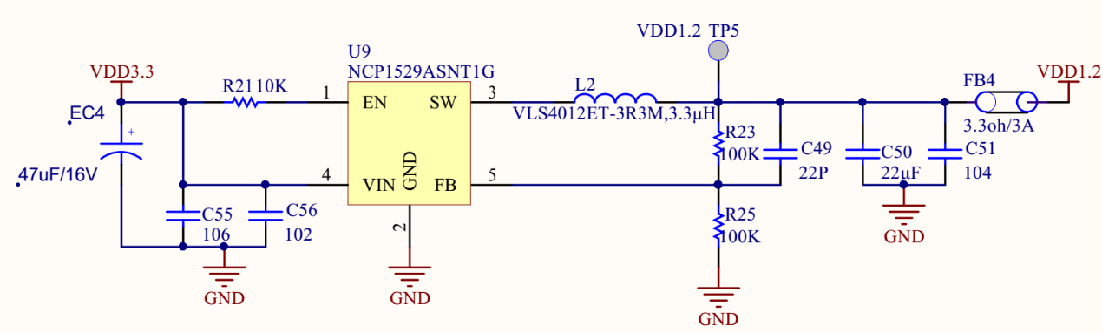

下图所式为AC620开发板上使用的1.2V电源电路,该电路使用NCP1529实现从3.3V电源到1.2V电源的转换,R23和R25为反馈电阻,设置两者阻值均为100K,即可实现稳定的1.2V输出。

为了实现电源和实际FPGA供电管脚之间的隔离,1.2V输出端还使用了一颗功率磁珠,当调试硬件需要将1.2V从FPGA管脚上断开时,只需拆掉FB4即可,这种设计思路在硬件设计中非常的常见。

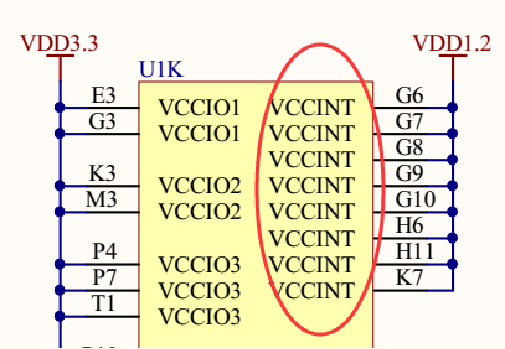

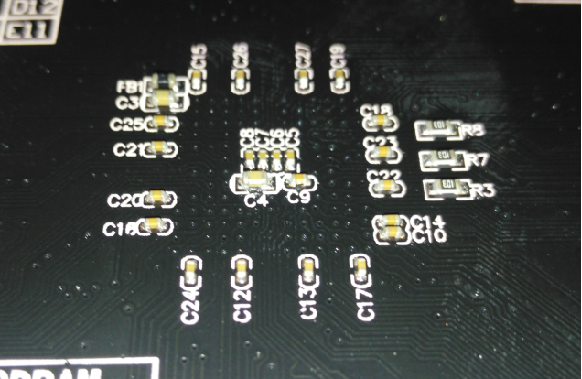

内核供电引脚在器件中被标识为VCCINT,因此,在设计时需要将标注为VCCINT的引脚都连接到内核供电电源1.2V上,如下图所示。这些电源引脚附近一般需要加高频滤波电容,因为内核功率是波动的,电流时大时小,但是内核电压却需要非常精确。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 上周热点回顾(3.3-3.9)