NMOS管和PMOS管阈值损失的简单理解

首先:输出端为带电容那端。

采用电容来模拟输出负载的原因:1.MOS的输出后面还会接其他MOS管的栅极,栅极和源、漏之间为直流开路状态。

2.栅极和源、漏以及沟道之间类似于一个电容的结构。

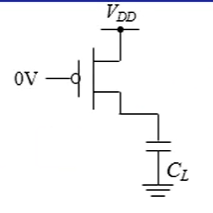

PMOS管

其次:源漏极的区分。(没加电源与地之前,没有源漏之分)

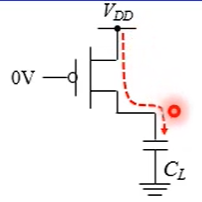

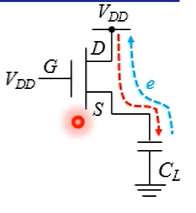

对于PMOS管,导电的多数载流子为空穴,而空穴可以视为带正电荷。上图为一个PMOS管,电流此时由VDD流向电容CL ,那么VDD作为源极,下面的输出端CL 作为漏极。

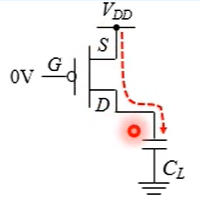

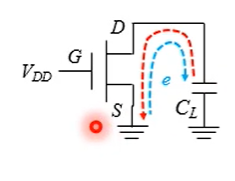

类似的,对于NMOS管,导电多子为带负电的电子,电子运动方向与电流的流向相反,则可以推断出电子出发端为源极(S),电子终点为漏极(D)。

4种情况:

PMOS输出“1”:接VDD的为源极(S),接输出负载电容的为漏极(D)。假设开始漏极(D)的电平为低电平0。PMOS的栅极(G)为低电平0V,源极(S)为高电平VDD。此时VGS =-VDD。所以|VGS |>|VTH |,PMOS管导通,电流由S流向D对输出电容充电,而VGS 保持不变,可以一直充电直到输出端的电平为VDD。

PMOS输出“0”:接负载电容的为输出端,假设开始负载电容上极板为高电平VDD(源极S),则下面接地的为漏极(D)。PMOS的栅极(G)接低电平0。开始时,|VGS |>|VTH |,PMOS管导通,电流由S流向D进行放电,源极(S)的电压逐渐减小,VG -VS 的差值逐渐变小,直到|VGS |=|VTH |时,PMOS管截止。源极(S)的电平保持为VTH 。

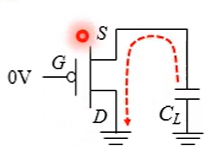

NMOS输出“1”:最上面接VDD的为漏极(D),接输出负载电容的为源极(S)。假设源极(S)的电平为低电平0。NMOS的栅极(G)为高电平VDD,漏极(D)为高电平VDD。开始时,VGS >VTH ,NMOS管导通,电流由D流向S对输出电容进行充电,电压VS 逐渐增大,VG -VS 的差值逐渐变小,直到VGS =VTH 时,NMOS管截止。源极(S)的电平保持为VDD-VTH 。

NMOS输出“0”:接负载电容的为输出端,假设电容上级板电平为高电平VDD,则上面为漏极(D),下面源极(S)。NMOS的栅极(G)接高电平VDD。VGS >VTH ,NMOS管导通,电流由D流向S对地放电,因为VGS 一直保持不变,可以一直放电直到输出端的电平为0。

小结:

1.NMOS传“1”只能达到VDD-VTH ,PMOS传“0”只能达到VTH,存在阈值损失。

2.NMOS管和PMOS管都是开关型器件。不管输出“1”还是“0”都要在导通状态下。

3.为解决阈值损失问题,采用CMOS管,让NMOS传“0”,PMOS传“1”。

本文是对:3_3_MOS开关的非理想性.mp4_哔哩哔哩_bilibili 的小记。

浙公网安备 33010602011771号

浙公网安备 33010602011771号