时序逻辑电路---从存储电路开始

组合逻辑电路的特点是,假设有足够的时间使逻辑门稳定下来,那么逻辑功能块的输出就只与当前的输入有关。

为了保存一些状态信息,则产生了时序逻辑电路。一个时序逻辑电路具有记忆功能。

存储信息的基本单元称为触发器,具有保持和接收(改变存储信息)的特点。

触发器按照电路功能分为:基本RS触发器、锁存器(电平触发器)、寄存器(边沿触发器)等。

按照存储原理可以分为:静态触发器和动态触发器(电容)。

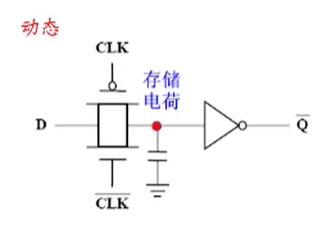

一、动态存储电路

将信息存储在高阻抗的存储电容上,当CLK为1时,传输门截止,此时存储电容为浮空状态(连接至后级的栅上)。反相器的是读出电路。

特点:1.需要定期刷新,防止电荷泄漏和电荷分享造成的电荷损失。

2.读出数据不能干扰到存储电容上的电荷,因此要使用静态反相器,加在栅上读出(不会有充放电电流产生)。

二、静态存储电路

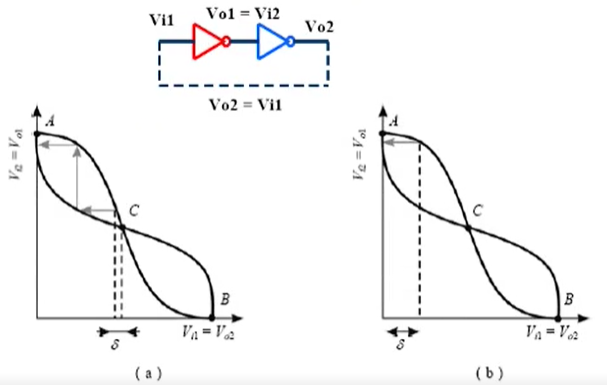

静态触发器使用正反馈(双稳态)来存储信息。

从上图可以看出,在C点处一个小的扰动![]() 就会经过INV1进行放大(C点增益大于1),然后作为INV2的输入继续放大。INV2的输出又作为INV1的输入。最终达到A或B(A和B的增益远小于1),稳定下来。所以称为双稳态电路。C点称为亚稳态点。

就会经过INV1进行放大(C点增益大于1),然后作为INV2的输入继续放大。INV2的输出又作为INV1的输入。最终达到A或B(A和B的增益远小于1),稳定下来。所以称为双稳态电路。C点称为亚稳态点。

时序逻辑电路中最简单的信息存储的电路可以由两个反相器首尾相连结而成,这种结构可以保存信息但很难改变(采用强写改变)。

那么要如何改变信息呢?可以采取:

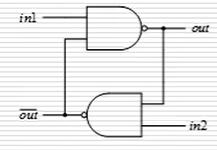

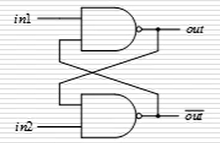

1.增加输入

这种增加输入的方式其实就是基本RS锁存器。

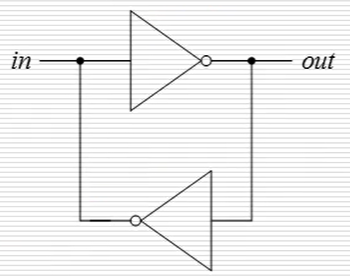

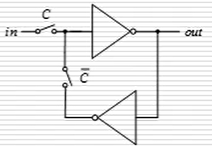

2.增加互补开关

一个作为输入开关,一个作为存储回路开关。通过信号C的控制来进行触发器保持与写入状态的转换。其中开关C可以是单个MOS管,也可以是传输门。上图为D锁存器。

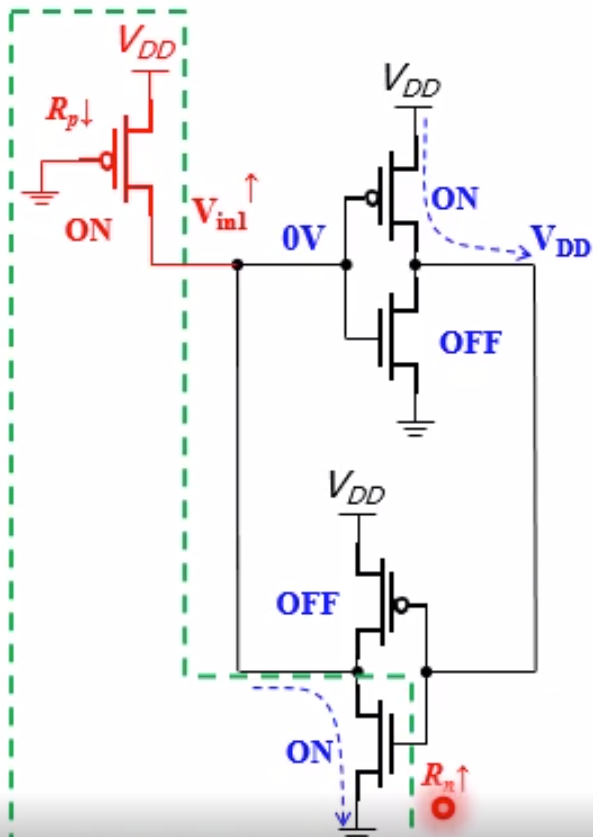

3.触发强度超过反馈环(有比逻辑)

采用强写的方式,如图,并且需要弱的反馈环路,反馈的反相器驱动能力要弱。

采用一个长通的PMOS管作为上拉(红色部分)进行强写,此时绿色方框内的NMOS和PMOS都处于导通状态,就是一个伪NMOS电路,此时NMOS和PMOS会进行电阻分压,我们希望Vin1尽可能高。所以要改变尺寸使得Rn尽可能大,Rp尽可能小。虽然拉不到VDD,但是反馈的环路会进行状态切换,从而导致绿框中的N管截止。

从锁存器开始

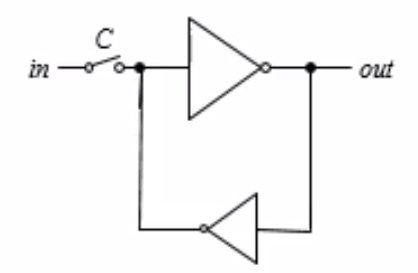

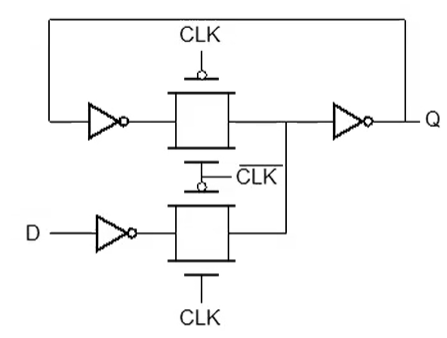

1.多路选择型的锁存器

![]()

可以看作由传输门构成的二选一的多路选择器。

CLK=1时,输入开关打开,环路开关截止,D的值可以传递到Q。

CLK=0时,输入开关截止,环路开关打开,双稳态的环路形成,输出Q值保持不变。

输入D直接连接一个反相器是为了:1.恢复电平 2.反相一次,使得输出的值Q=D。

优点:使用开关控制来存储信息,无比逻辑,不需要设计晶体管尺寸。

缺点:时钟CLK信号驱动了4个晶体管,时钟负载大。

2.传输管锁存器

将传输门换成传输管。

优点:面积小,并且时钟负载减小。

缺点:阈值电压损失。

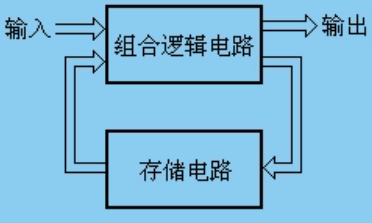

时序逻辑电路是由组合逻辑电路和存储电路构成的,如果上图的存储电路由锁存器构成,那么在锁存器的写入功能有效时,组合逻辑的输出会经过锁存器并且直接到达组合逻辑的输入,不停的运行下去,导致无法准确知道某一时刻存储电路的输入与输出。因此,时序逻辑电路中的存储元件一般使用边沿触发的触发器。

边沿触发器

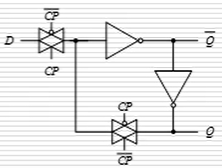

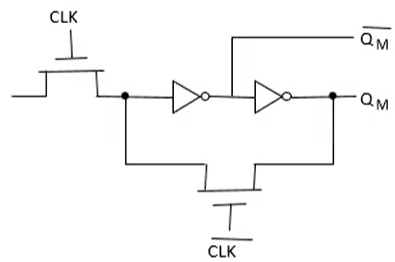

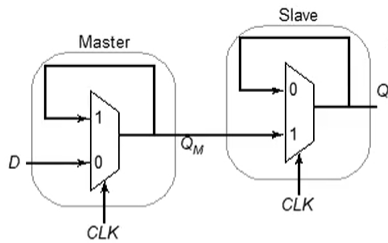

构成一个边沿触发寄存器的最简单方法是采用主从结构。即将一个负锁存器(主级)和一个正锁存器(从级)进行串联构成。

如上图为上升沿触发。CLK为低电平,主级接收,D->QM,从级保持Q不变。

CLK上升沿,QM->Q.

CLK高电平,主级保持QM,从级接收。

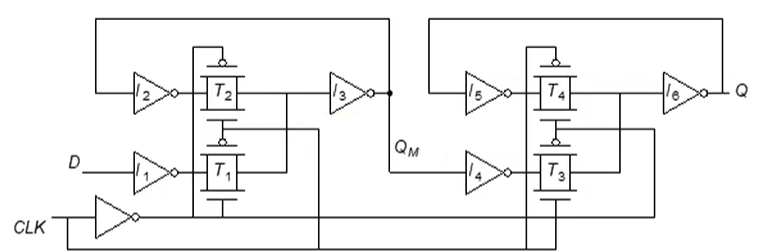

晶体管的电路如上图所示。

优点:只在始终边沿来接收数据,抗干扰能力强。

缺点:这样一个触发器需要20个晶体管,并且时钟负载也大。

1. 可以去掉环路开关T2和T4,但是这样使用强写来改变电路,需要考虑晶体管尺寸(有比逻辑)。

2.可以将传输门换成传输管

优点:无比逻辑,面积小。

缺点:传输管的阈值电压损失。

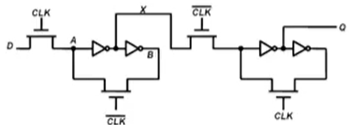

以一个正沿触发的寄存器为例:

边沿触发器的三个重要参数:建立时间Tsu、保持时间Thold和传播时间Tclock-q

建立时间Tsu:数据在时钟沿到来之前需要保持稳定的时间。

保持时间Thold:数据在时钟沿到来后需要保持稳定的时间。

传播时间Tclock-q:建立时间Tsu和保持时间Thold都满足要求的前提下,从时钟沿到产生稳定输出的时间。

......

时钟偏差:有正负之分,正的时钟偏差有助于提高频率,负的时钟偏差会降低频率。

(如果数据从前往后和时钟方向相同,并没有反馈,则可以提高频率)

时钟抖动:增大最短时钟周期。