TLB和CPU缓存

TLB(Translation Look=aside Buffer)

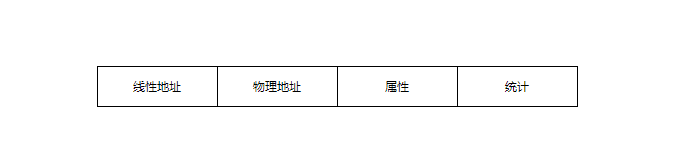

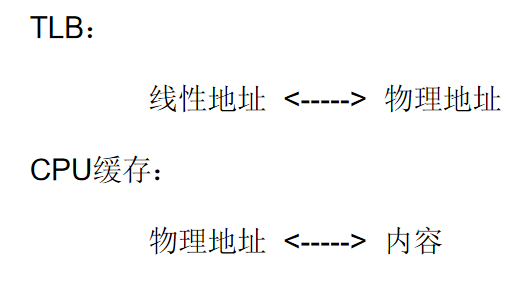

TLB地址转译快查缓冲区,如果每次应用程序访问一个线性地址都需要先解析(查PDT,PTT)那么效率十分低,为了提高执行效率CPU在CPU内部建立了一个TLB表,此表和寄存器一样访问速度极高。其会记录线性地址和物理地址之间的对应关系,这样以后当程序在访问此线性地址时就直接访问对应的物理地址了。

因为每一个进程都有对应的CR3寄存器,指向不同的页目录表或也目录指针表,当CR3变化时(进程切换)其对应的线性地址与物理地址的映射也变了。所以会将TLB刷新,但是对于高2GB的地址而言,其对应的TLB并不会刷新因为一般高2GB地址是不变的。高2GB对应的PDE或PTE的G位为1,表明其在CR3切换时并不会刷新TLB中对应的项。

INVLPG //特权指令,可以清除TLB

cpu缓存

CPU缓存是建立 物理地址和内容之间的联系,所以当应用程序访问数据时可以先从TLB中得到对应线性地址的物理地址,再从CPU缓存中取出物理地址对应的内容。

浙公网安备 33010602011771号

浙公网安备 33010602011771号