modelsim使用

手动使用

写好测试文件

挺好理解的放代码看一下就懂了:

文件名字为原本代码文件加上_tb

`timescale 1ns/1ns //精度1ns

module huiyidemo_tb;

reg sclk=0 ;

reg rst_n=0 ;

wire [2:0]test_out ;//这个是不需要写的

initial begin

#100 //100ns

rst_n<=1'b1;

end

always begin

#10 sclk<=~sclk;

end

huiyidemo huiyidemo_u(

.sclk (sclk),

.rst_n (rst_n)

);//调用模块

endmodule原本的代码:

module huiyidemo(

input sclk,//系统的时钟,自己设计

input rst_n,//复位信号

output [2:0]test_out//led

);

reg [2:0]test_out_s;

assign test_out=test_out_s;

always @(posedge sclk or negedge rst_n)begin

if(rst_n == 0)begin

test_out_s <= 3'b000;

end

else begin

test_out_s <= test_out_s+1;

end

end

endmodule打开modelsim

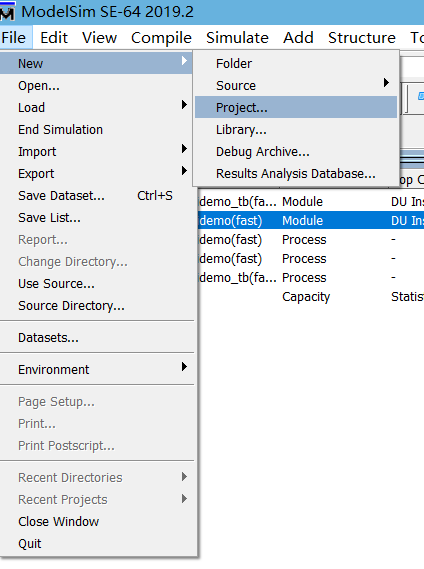

如果没有工作环境就创建一下项目

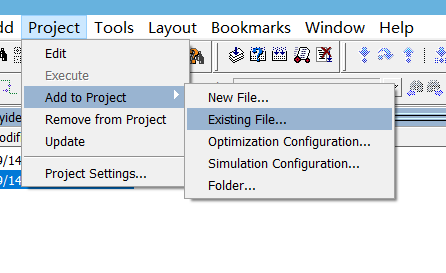

然后再项目中添加已经写好的代码:

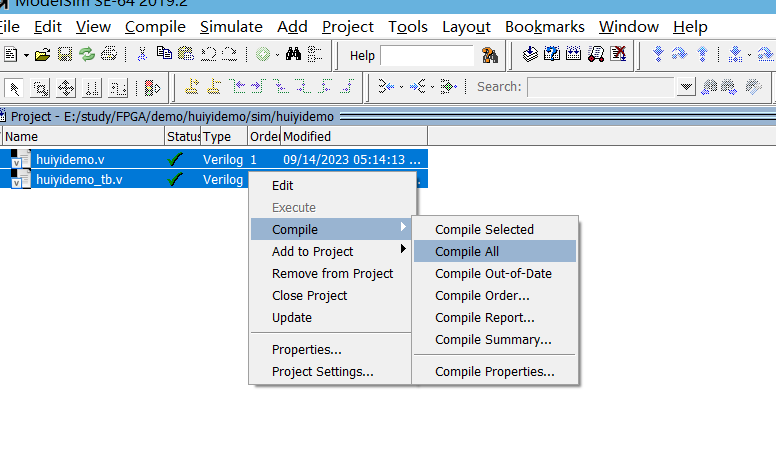

全选后全部编译

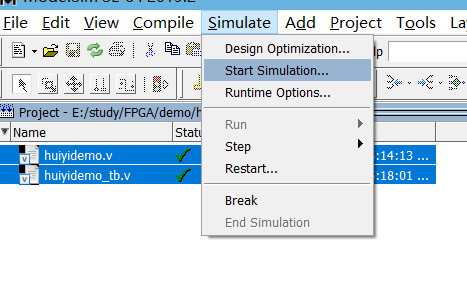

最后点击仿真

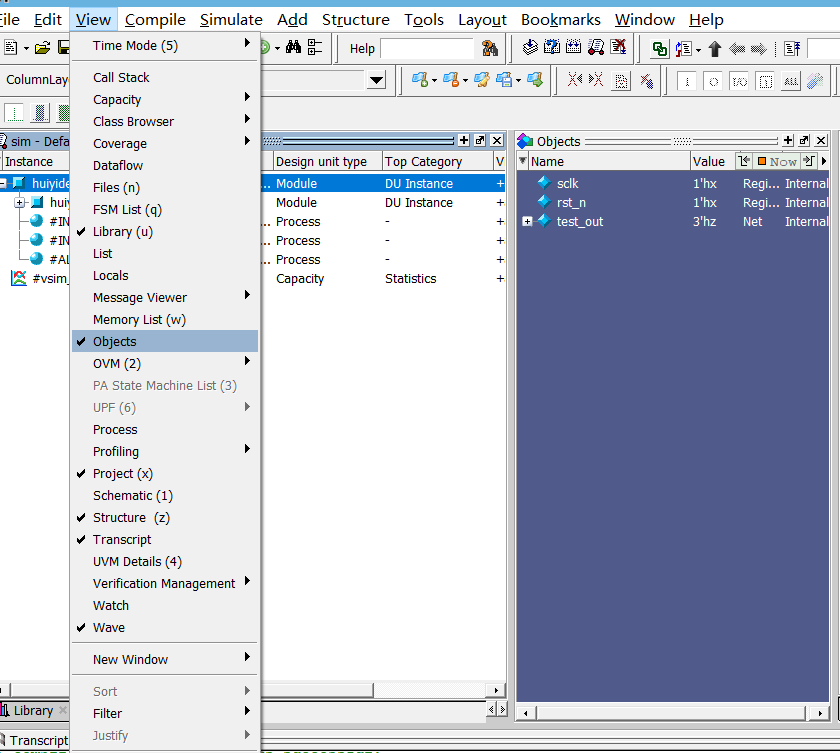

如果没有object再这里加

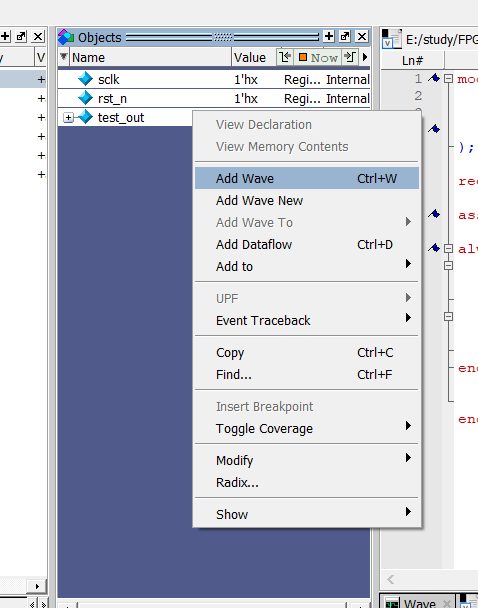

添加到波形模拟中

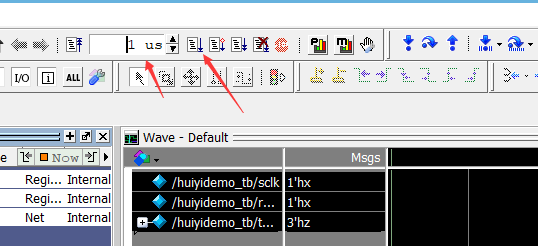

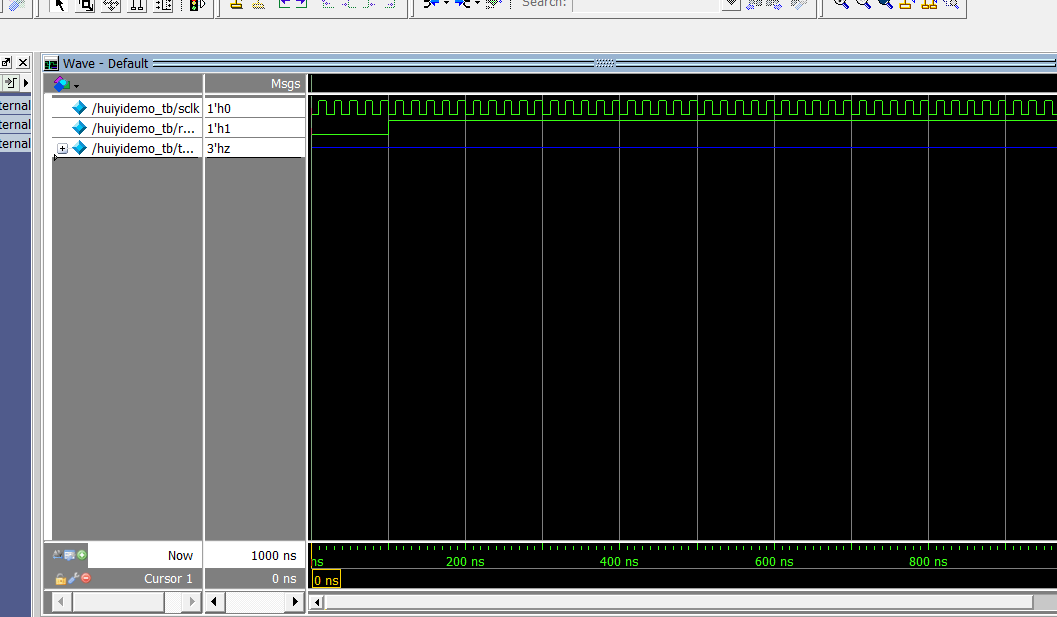

设置模拟时间和开始模拟

浙公网安备 33010602011771号

浙公网安备 33010602011771号