复习1

这么久没学都忘完了,复习一下之前学的东西

数码管verlog

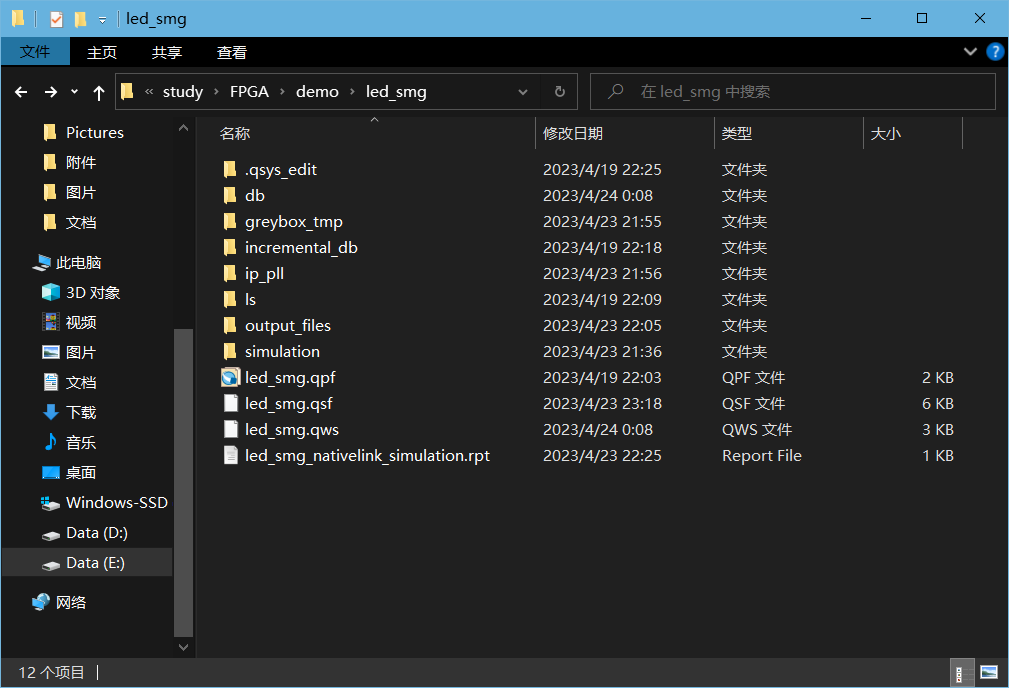

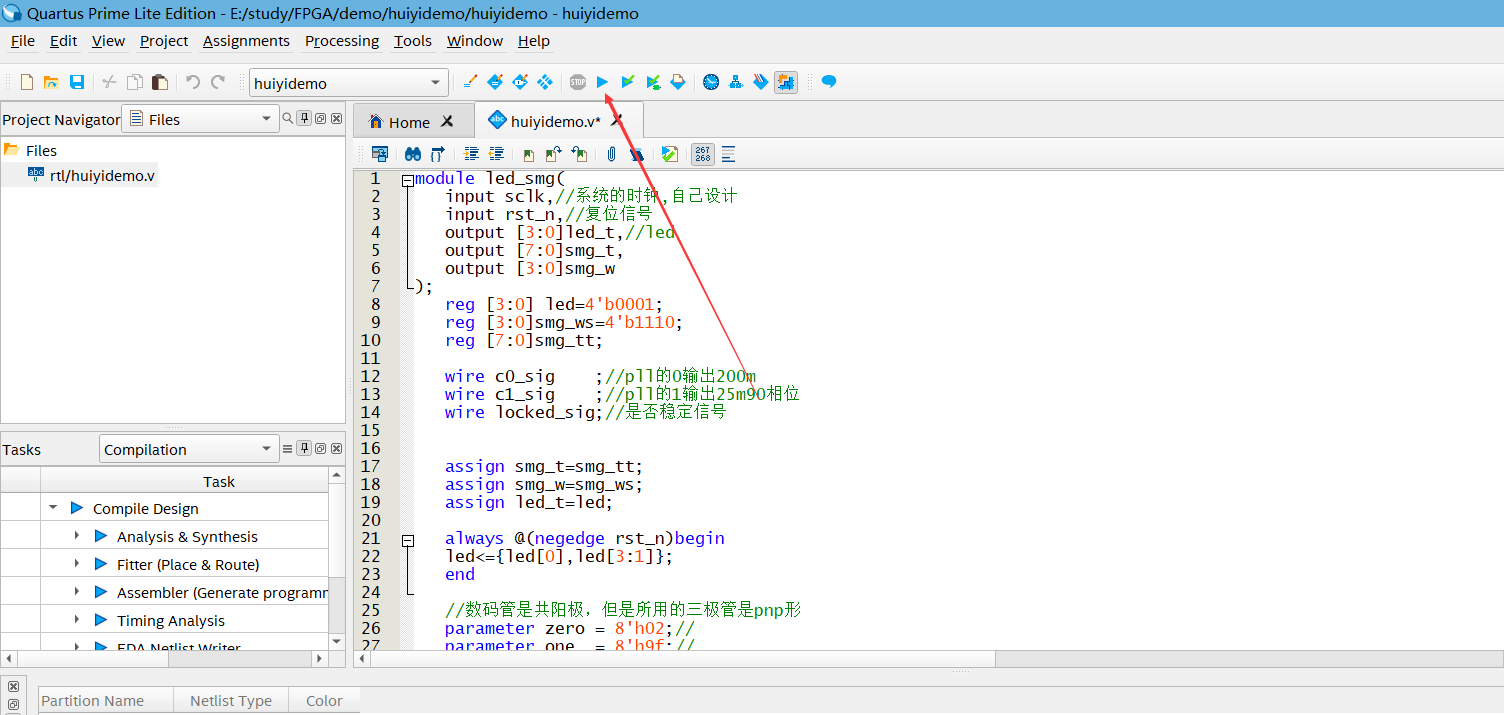

先看一下之前写的数码管文件

这些文件杂七杂八的,很多都忘了是什么作用了

基本文件

基本文件如上,doc是文档说明,rtl储存用户的代码verlog,sim存储仿真文件

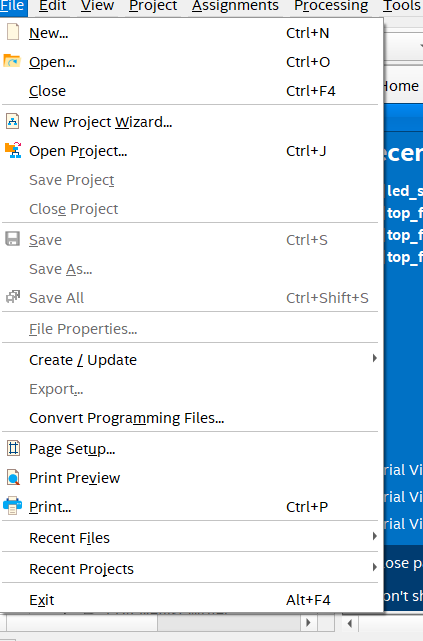

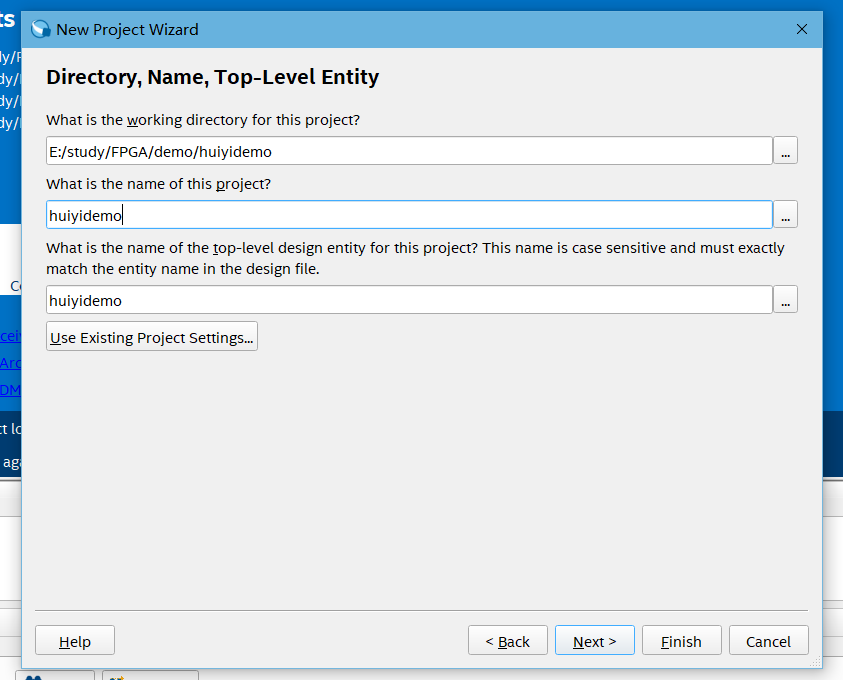

创建verlog

按照顺序点击这些步骤,写上工程路径、工程的名字和顶层名字,其中工程名字和顶层名字需要一致

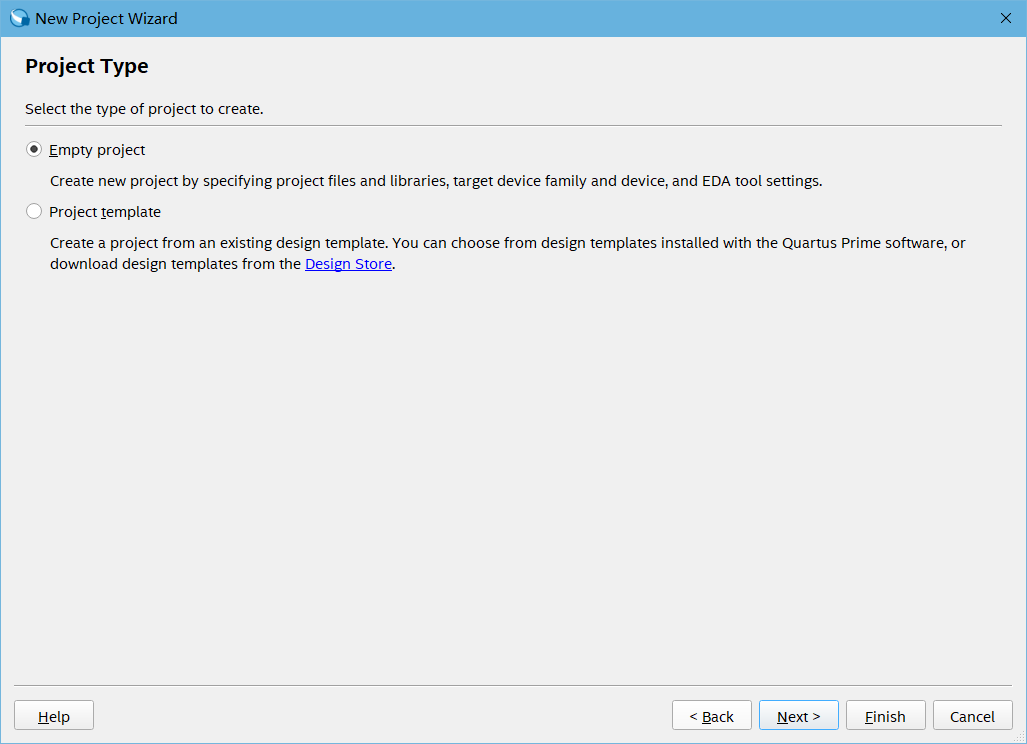

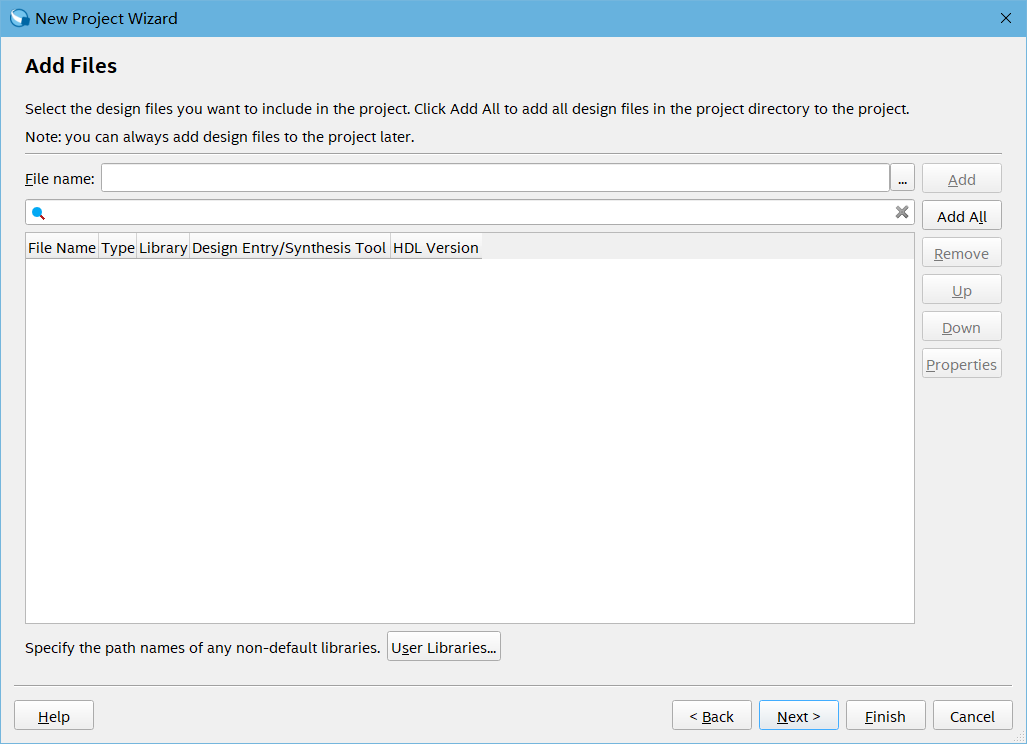

创建空文件

由于这个文件是需要我们后面加上代码,不需要加其他文件

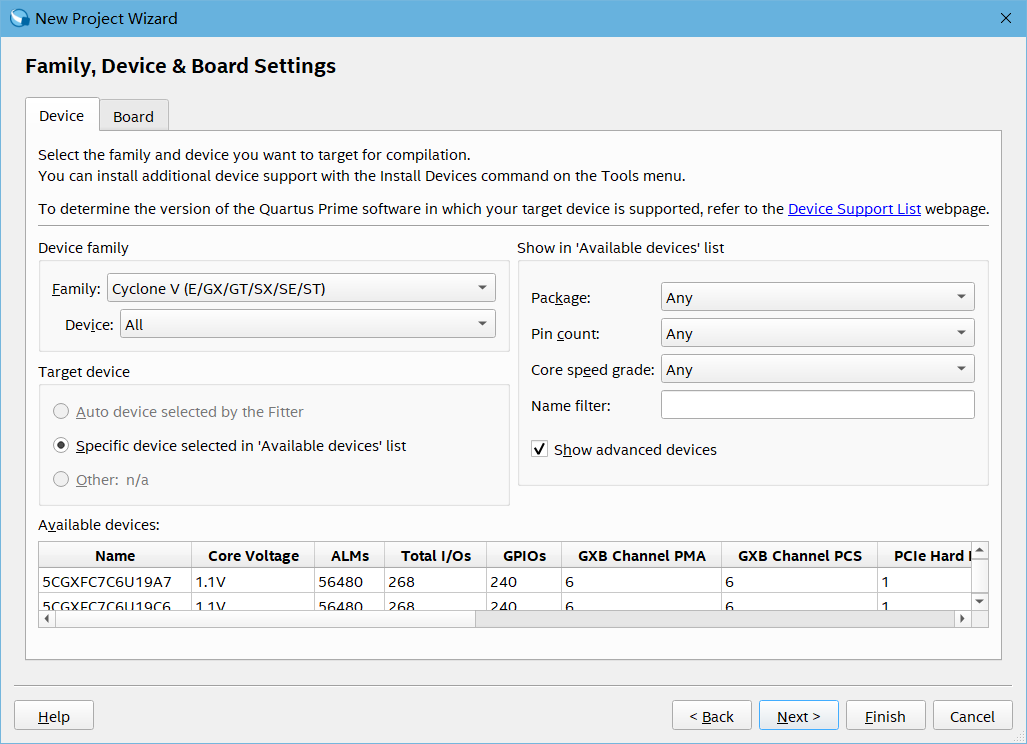

接下来就到选芯片了

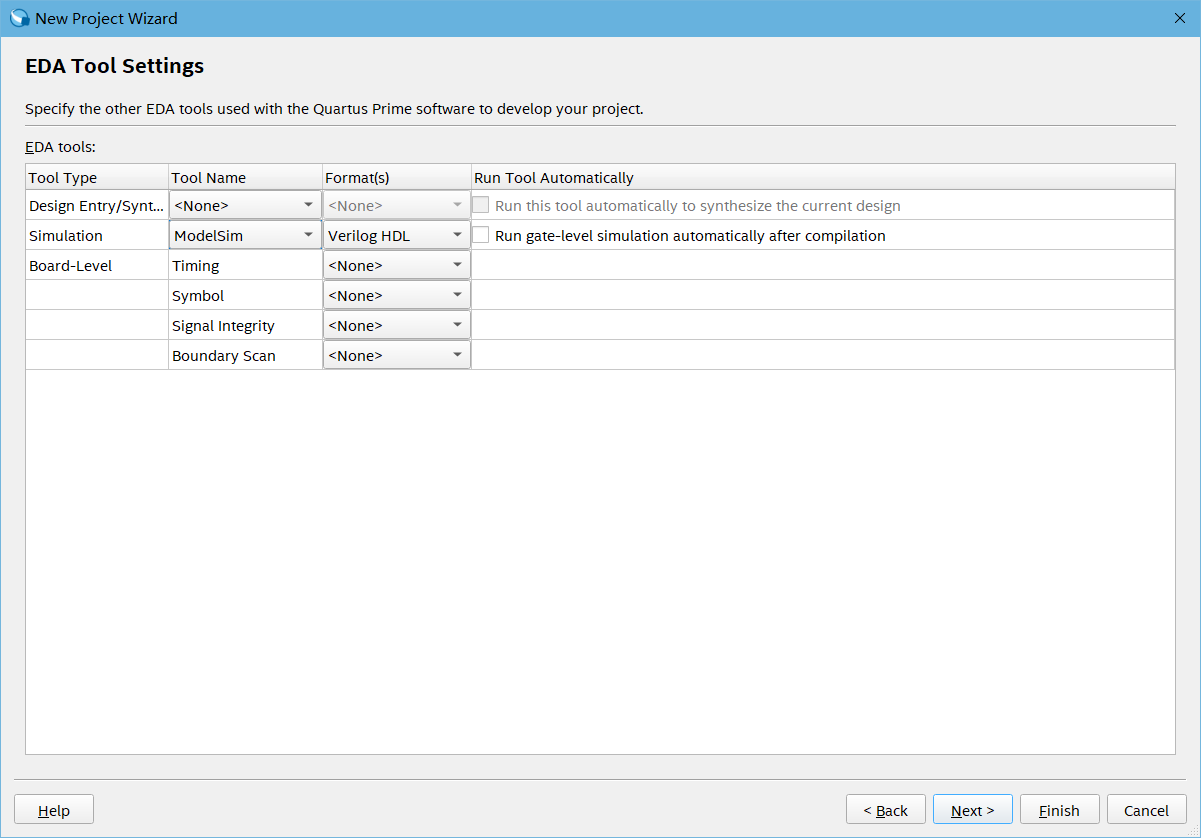

选择语言和仿真

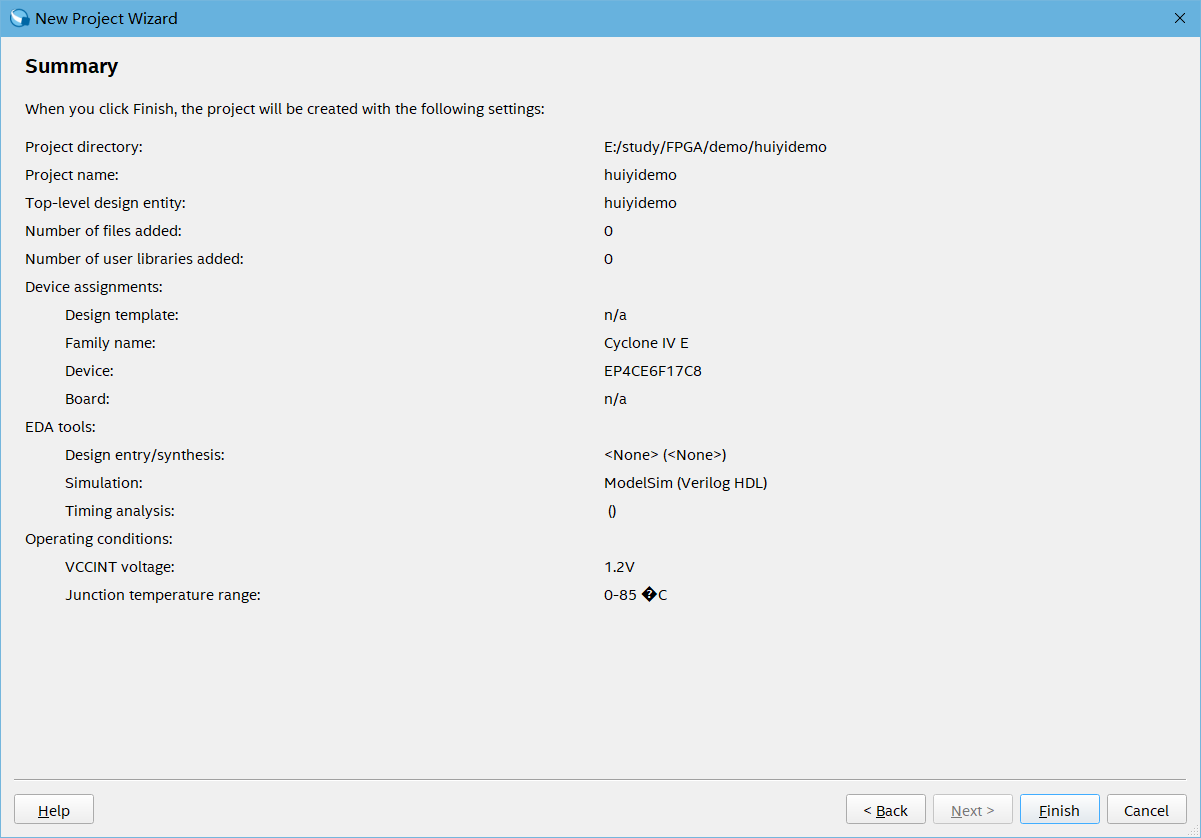

接下来就是详情面板了

这就是创建的文档了

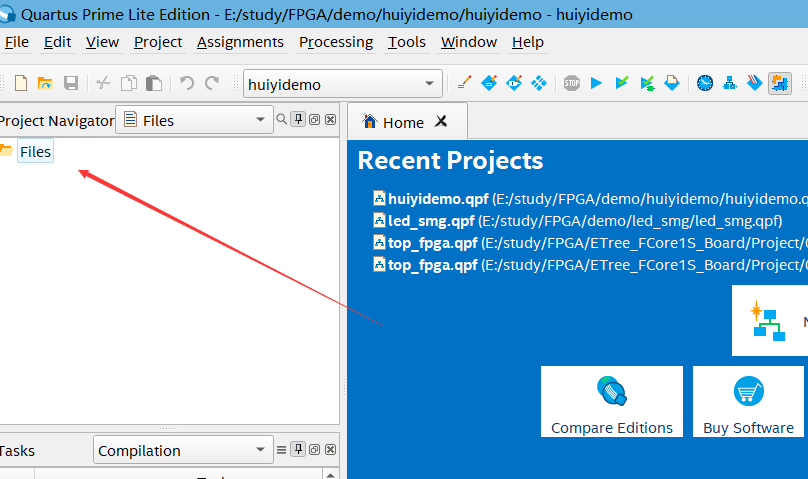

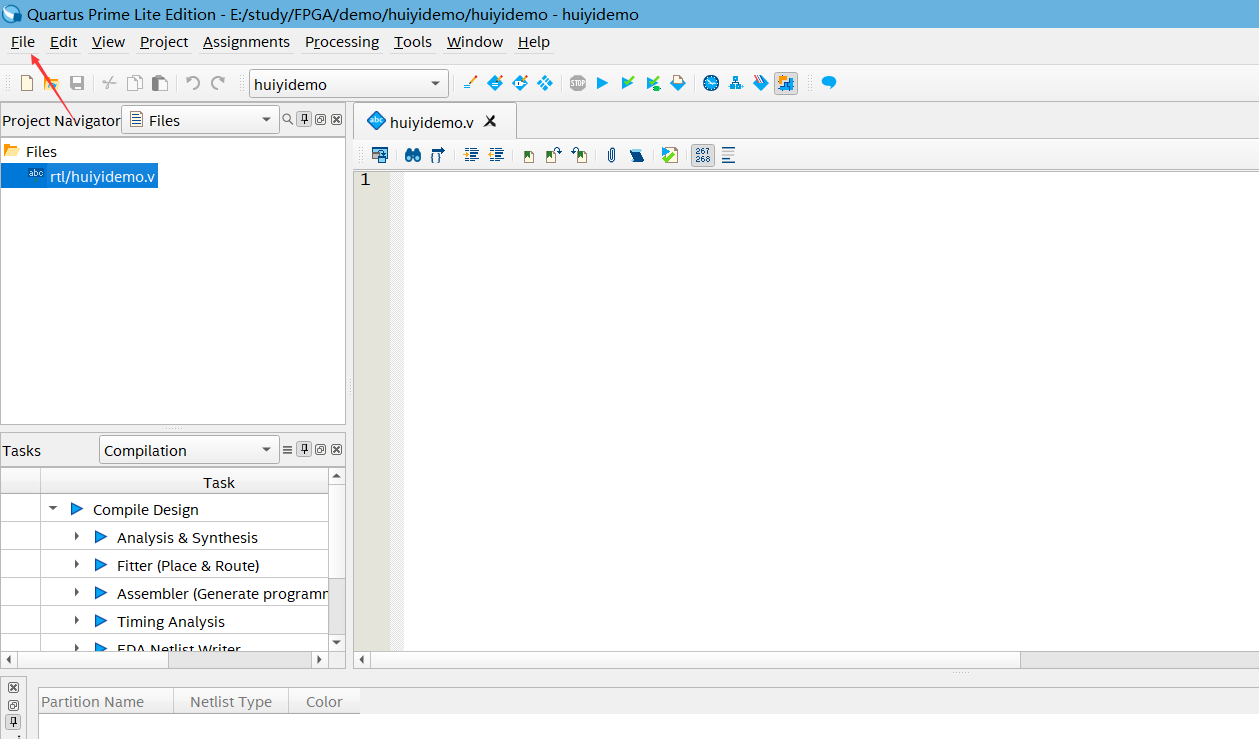

创建verilog代码文件

点击新建文件然后简历verilog文件,此时不能保存,要继续选择file中的另存为,保存到我们当前项目的路径里面并设置名字就可以得到.v文件

这样我们就得到了一个简单的fpga文件

quatus的使用

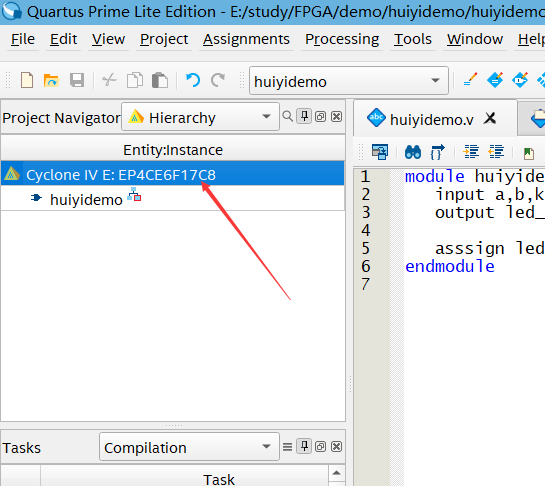

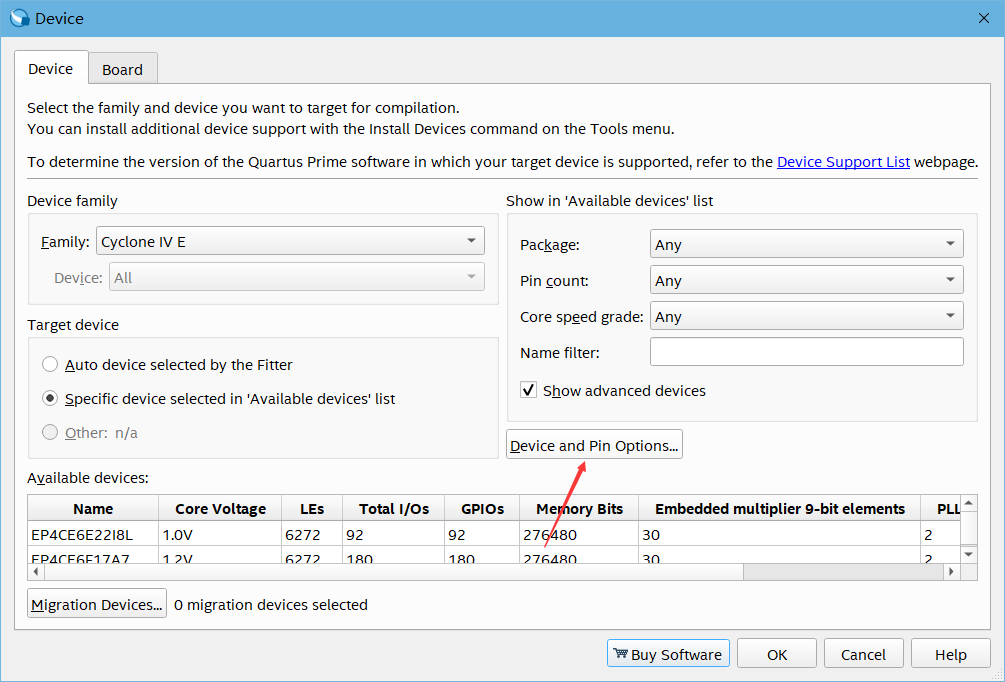

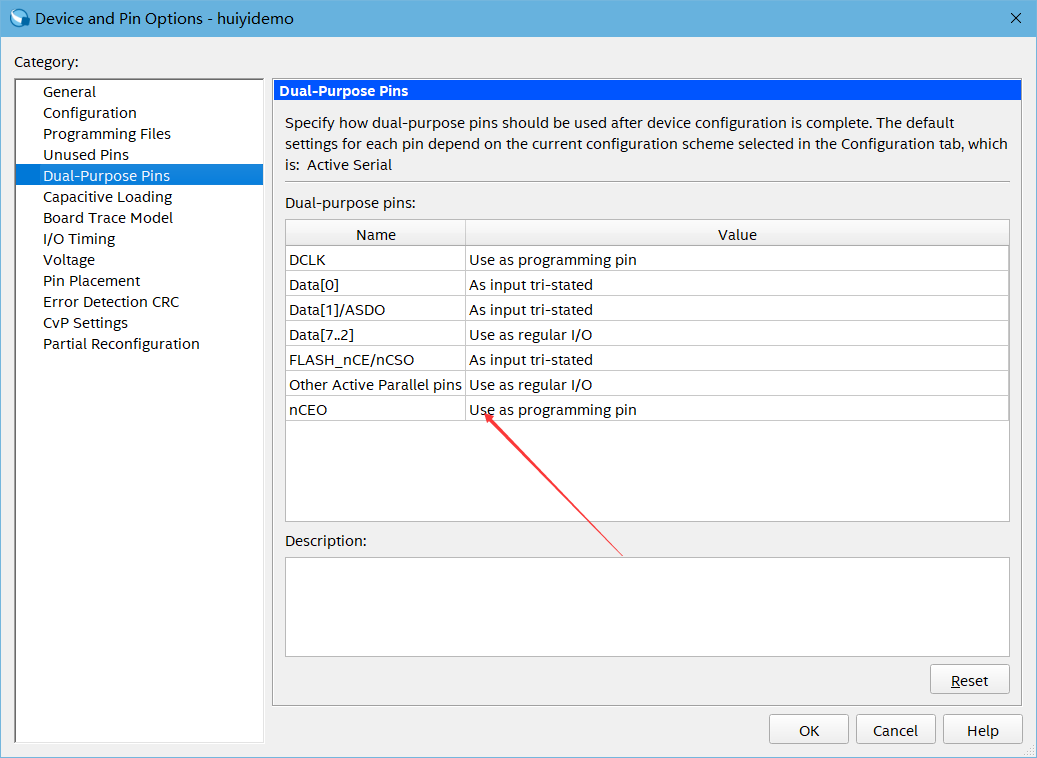

当我们所使用的芯片用到下载脚(特殊脚)的时候需要对项目进行设置:

双击这个名字

点击options

在这个位置就看也设置引脚的作用

时序约束文件

什么是时序约束?

时钟频率高的时候或者占用逻辑资源多的时候需要时序约束,主要是对延时时间进行调整达到时序的要求,输入输出等。

输入时钟的约束就是设置开发工具所输入的时钟是多少,开发工具根据这个来优化pcb布局。

查看时序约束文件

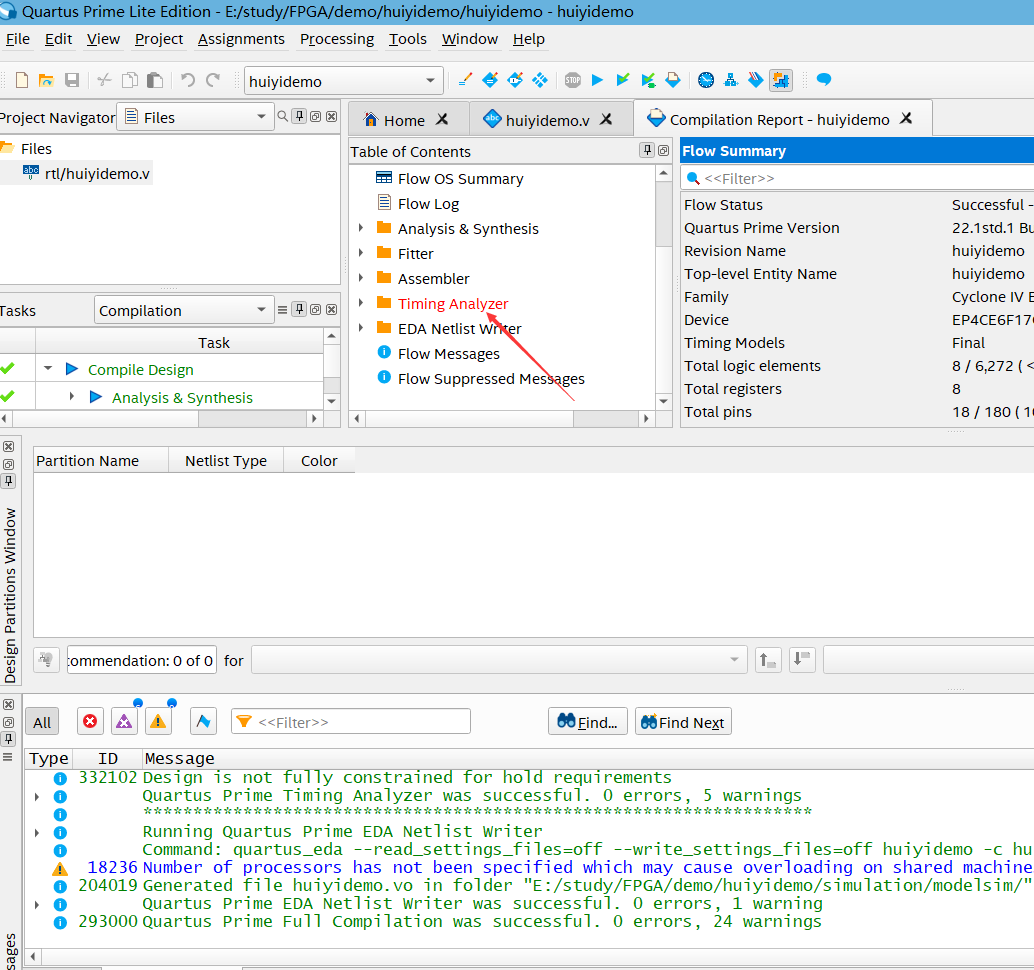

创建时序约束之前需要对项目进行一次编译:

编译完之后虽然提示编译成功但是这个timing还是提示红色,其实就是提示这个项目没有添加时序约束

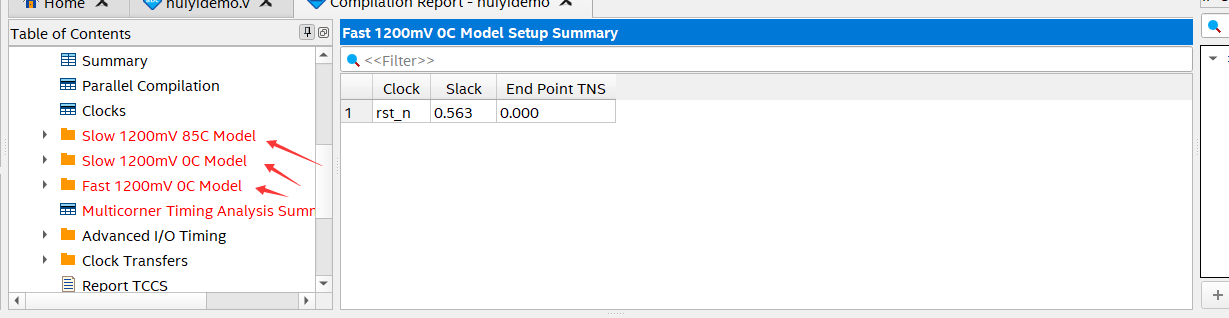

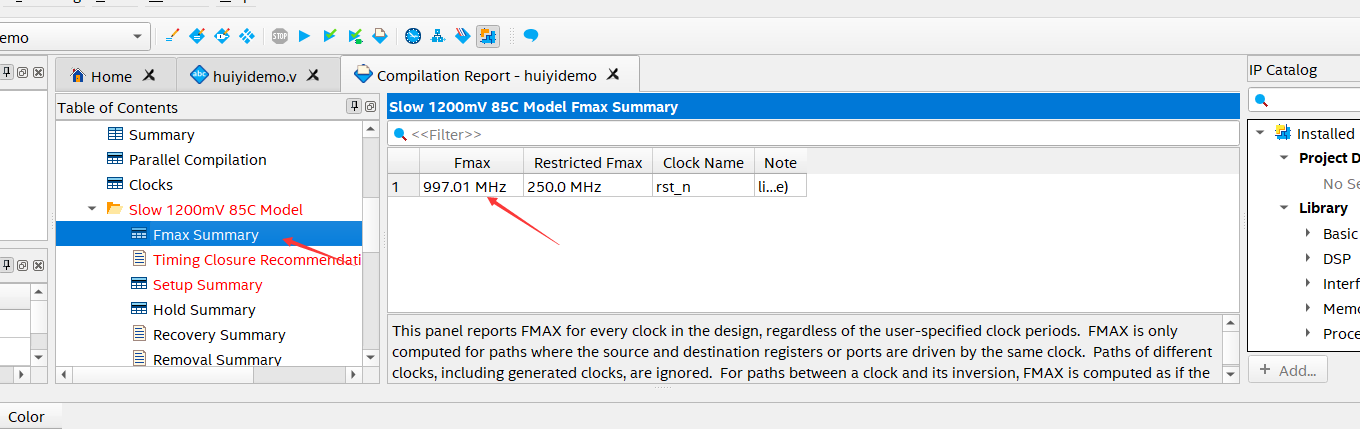

分别是85°、0°的时候的最低和最高速度

打开一个文件可以看到最高的频率

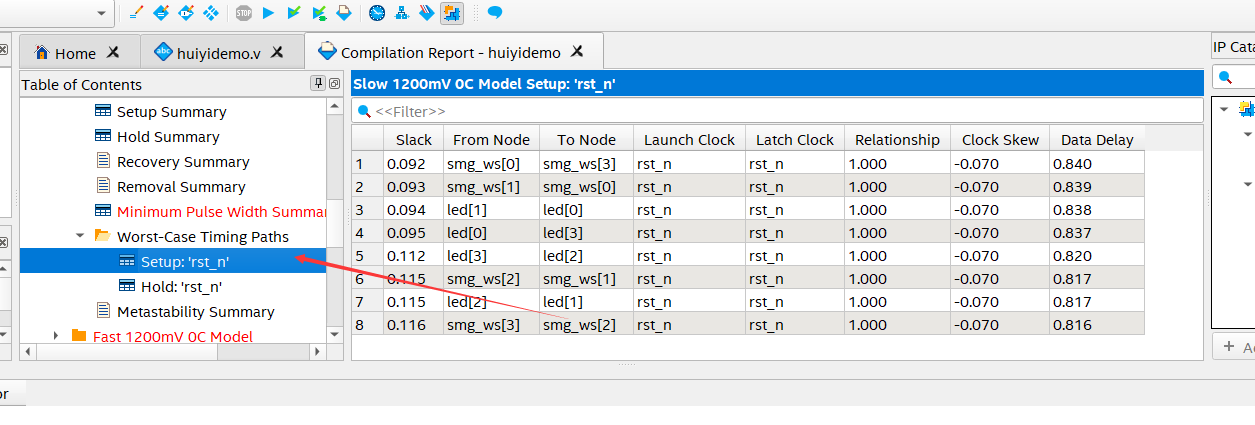

在这块可以看见建立电路的时候最坏的路径,如果建立了时序约束仍然不行可以查看这个文件

那么就是创建时序文件了(sdc)

创建时序文件

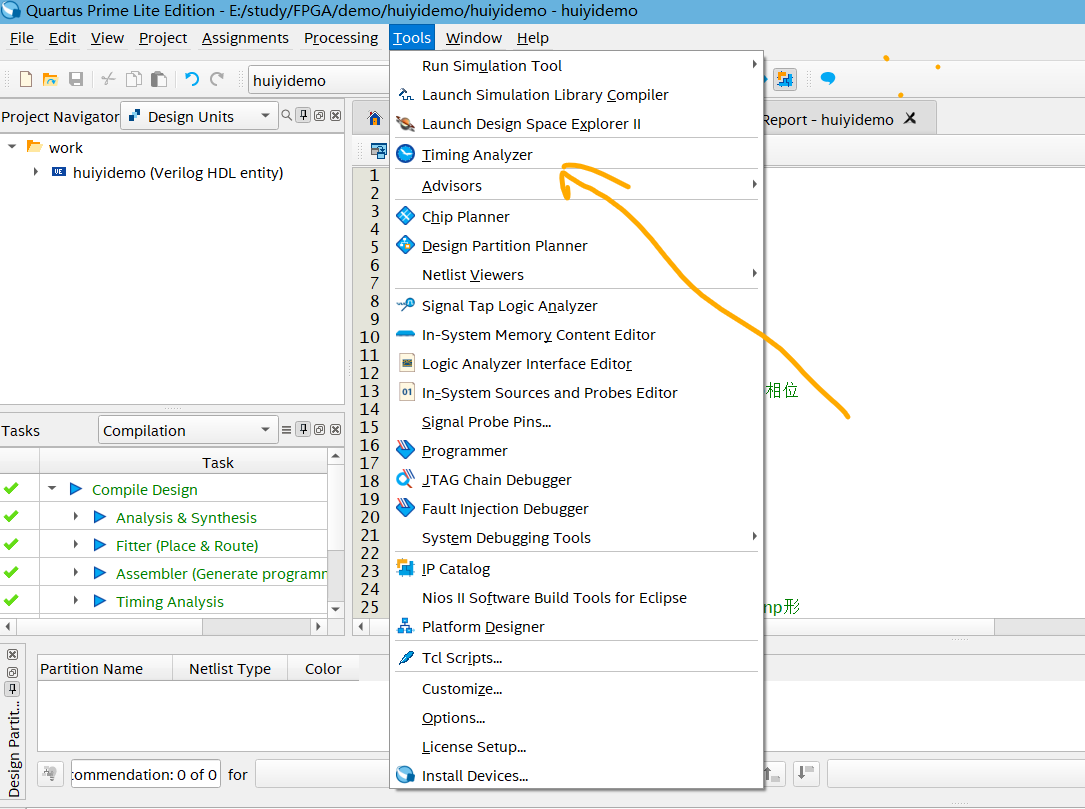

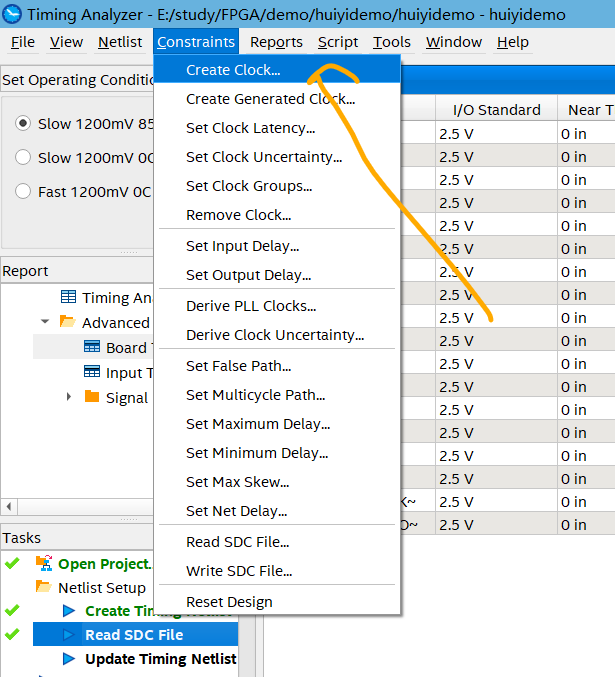

选择这个时序分析工具

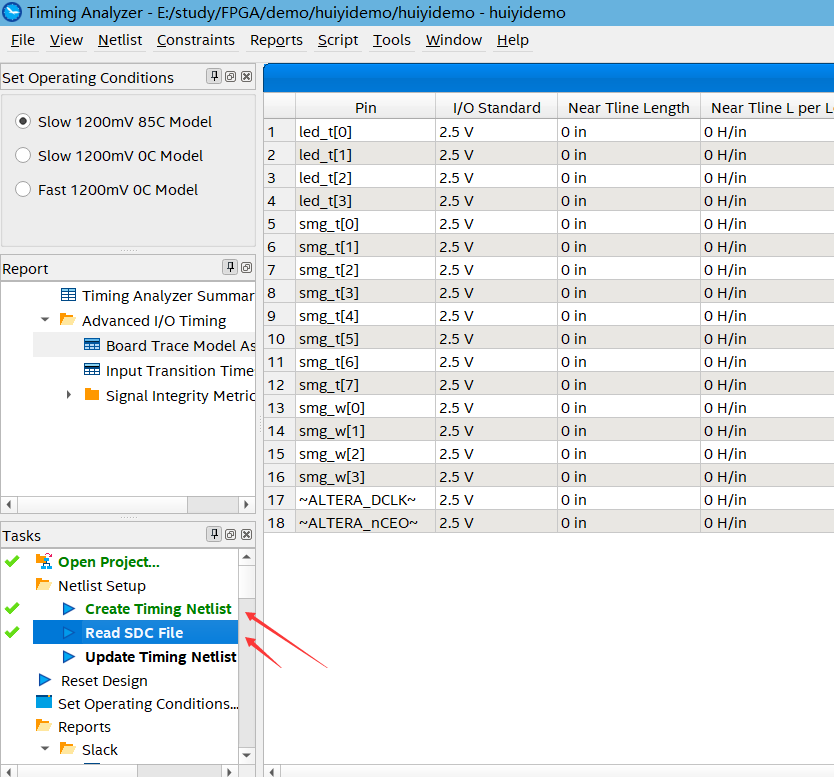

吧前俩个点了,一个是分析时序列表的一个是阅读时序文件的

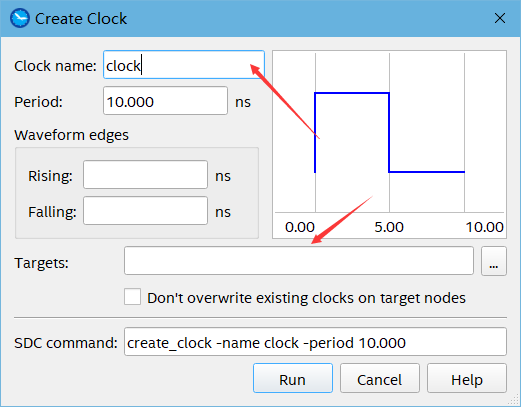

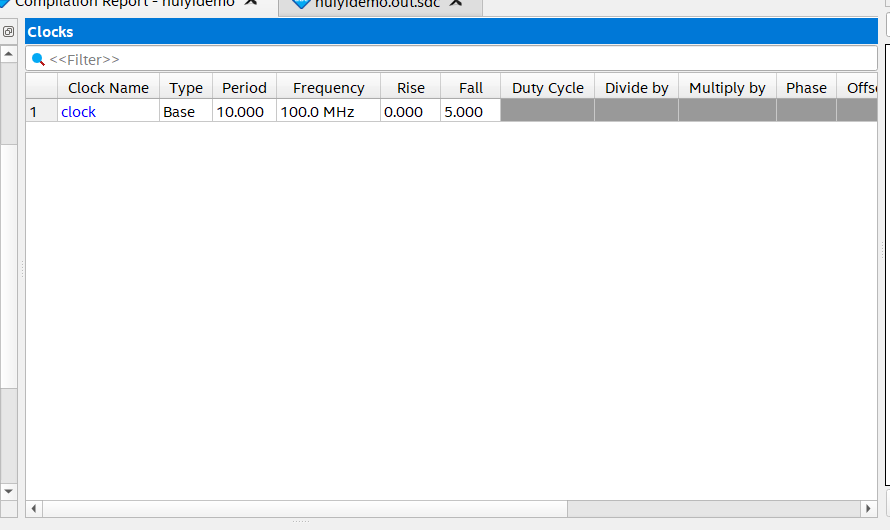

最后创建clock

名字其实是指时钟的代号,可以不一样

上升下降沿不填默认占空比百分之五十

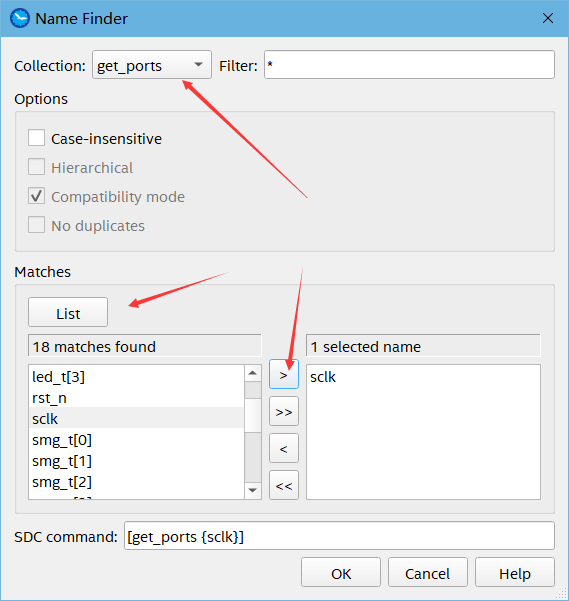

target选择所要修改的时钟,如果是外部端口则选择port不然可以试试其他的,然后list、最后选择

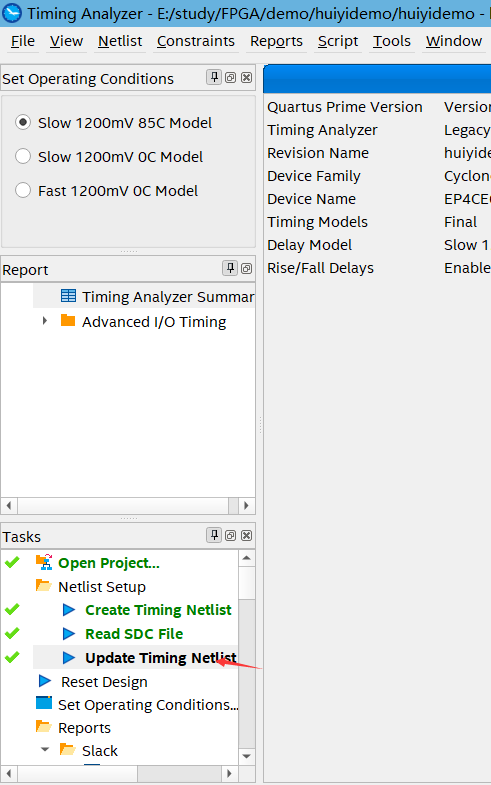

最后将剩下的那个更新

最后拉到最下面点击写入就行了。最后再次编译:

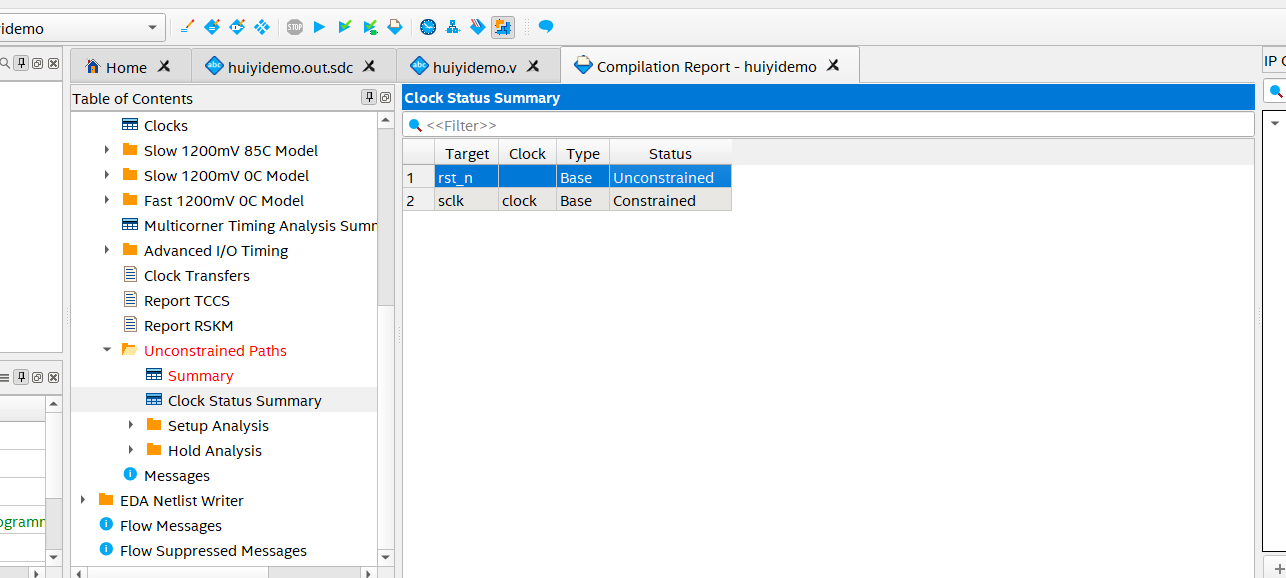

可以看到成功设置了

这个由于rst_n是用来输入引脚的所以不需要时序约束

浙公网安备 33010602011771号

浙公网安备 33010602011771号