《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新《FPGA全程进阶---实战演练》内容,此电子书是笔者三年所做过的一些项目总结,又有擅长记录的习惯,于是整理成博客。

过些天会更新的内容有C++学习初步,友晶科技 DE1-Soc板卡学习笔记,Altium Designer画板技巧,在去下一家之前尽量更新完毕。

今天讲一下Signal Tap II的使用。

1 基础知识讲解

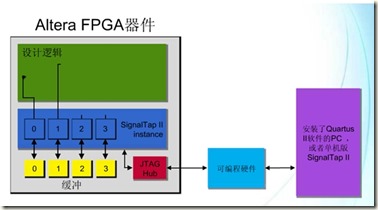

本章主要是讲解signal tap II的使用,signal tap II是quartus II 软件内部自带的一个逻辑分析仪,对于多通道数字信号的使用,一般都采用逻辑分析仪来操作。

Quartus II软件可以选择要捕获的信号,开始捕获的时间,以及要捕获多少的数据样本,还可以选择直接从器件的存储器块通过JTAG端口传送至STP II,并且有单次采样或者连续采样模式,捕获实时数据,方便工程的调试与开发。

对于signal tap II而言,是在工程中引入宏功能,以预先设定的时钟采样实时数据,并存储于FPGA中的RAM中,所以可见,使用STP II也要使用一定的代价,那就是占用FPGA内部资源,如果工程资源余量充足,况且可以使用,紧张的时候不建议采用STP II ,可以改用外部的逻辑分析仪操作。

还有一点注意的是,在全编译工程时,尽量不要把STP的文件也加载进来,因为STP本身占用一定的存储空间,这样会使编译速度减慢,而且还会消耗内部资源。

图32.1 signal tap II 采集原理

2 操作实例

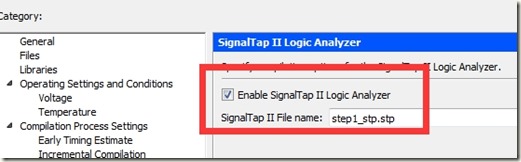

在使用STP II之前,先把工程中的各引脚及其他设置设置好,然后全编译,编译完之后,再执行下述操作。

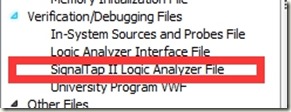

1. 新建stp文件。

2. 点击file---save as,然后输入你想设定的名字,然后点击yes。

这里需要注意一下,就是如果你不想使用stp文件,或者使用其他的stp文件,可以在assignments---signaltap ii logic analyzer中设置。

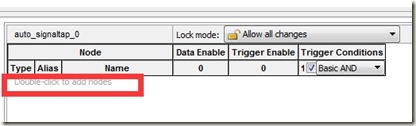

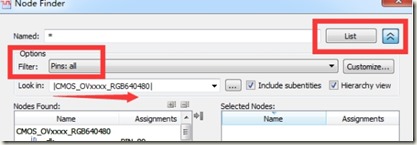

3. 接下来,我们要双击如下图所示的位置,调出节点发现器。

然后现在filter中选择pins:all,再点击list按钮,实现把所有的节点列出来。

对于上图中的filter选项中,当然还有其他的模式选择,比如前适配和后适配等,对于输入或输出信号,我们选择pins:all,这个选项,捕获模块接口(两个模块之间的沟通)信号则选择signal tap ii:pre-synthesis 选项,这是前适配,没有经过综合和适配的,其他模式一般不常用。

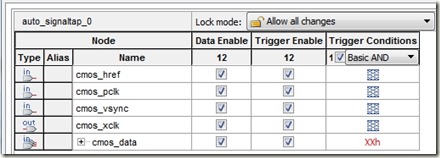

添加完之后的信号。

4. 设置采样时钟和采样深度

采样时钟决定了显示信号波形的分辨率,它的频率要大于被测信号的最高频率,否则无法正确反映被测信号波形的变化。采样时钟必须为采样信号的2倍及以上。SignalTap II在时钟的上升沿采样,可以使用设计系统中的任何信号作为采样时钟,根据Altera公司的建议最好使用同步系统全局时钟作为采样时钟。但是在实际应用中,多数使用独立的采样时钟,这样能采样到被测系统中的慢速信号,故需将系统时钟进行分频。

指定采样深度,在“Sample depth”处选择采样深度,即信号能看多长,它是根据设计中剩余的RAM块容量和待测信号的个数决定的。该值受FPGA芯片内置存储器大小的限制,设的过长,编译会通不过。

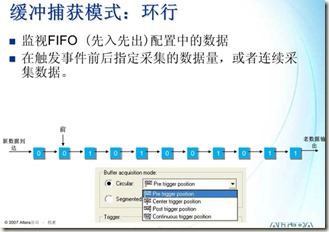

触发位置的设定,有前,后,中间,连续触发方式。

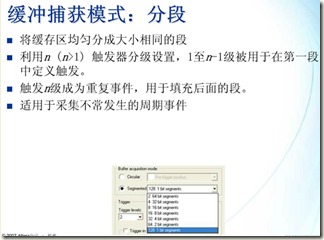

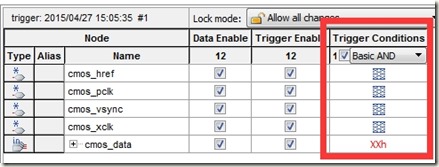

对于上图中的trigger conditions中可以设置多段式,如下图所示。

这种包括前触发方式(采样的数据12%为触发前,88%为触发后),中心触发方式(采样的数据50%为触发前,50%为触发后),后触发方式(采样的数据88%为触发前,12%为触发后),以及连续触发方式,前触发方式是来自于触发后的数据,中心触发来自于前触发和后触发,后触发来自于前触发的数据。连续触发方式将保存新数据,与触发器的位置无关,直到signal tap ii 停止工作。

上图中是设置触发的方式,有高电平,低电平,任意电平,不关心等等选项,可以根据所选用的信号进行设置触发方式。

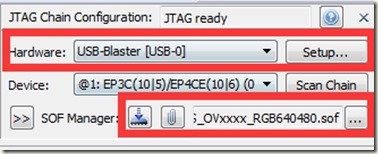

设置好上处的各个参数后,开始重新编译整个工程,然后将整个程序下载到FPGA开发板上面。当然也可以不用去下载到开发板上面,可以利用如下图的形式。

指定JTAG接口,然后将JTAG chain 加载进来,然后再把SOF文件也加载进来,再点击下载按钮。

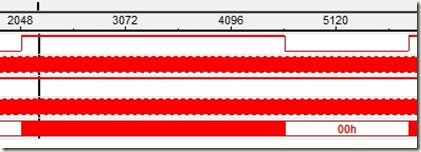

采集回来的数据如下图所示。

可以看出href的宽度为2560,但是由于我们的输入时钟为24MHz,采样时钟为48MHz,所以一个数据被采样了两次。那么每行输出的数据个数应该是2560/2 = 1280。由于输出的格式是RGB565格式,所以每个时钟输出两个数据,所以一行要输出640X2 = 1280个数据,可见和预期是一致的。

注意:xclk和pclk没有直接的关系,每次复位都会有不同的效果。

注意:对于帧频的输出,OV7725手册中规定是输出30Hz,可能有时候检测到25Hz,这个是因为若设置成50Hz的自动避免时,帧率只能输出到25Hz,但若设置成60Hz的自动避免时,帧率能输出到30Hz;

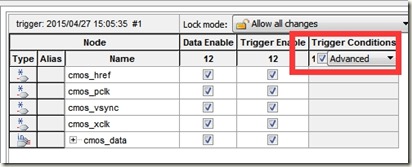

STP II 中的高级设置

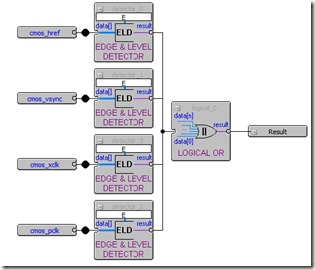

高级设置利用友好的GUI界面,可以方便地进行拖拽到指定的界面,然后设置相关的触发方式,如下图所示是一个简单的例子,还是针对上述的模块。

如上图所示,这个图形化的设置方式,是通过把触发方式设置成高级触发方式来设定的,其中E表示一旦有边沿变化,就会有高电平输出,然后经过组合逻辑或运算,输出结果。大家可自行尝试。

/****************************************************************

//===============================================================

上述内容如果有侵犯到您的权利,请及时与本作者联系,会在第一时间处理联系方式:

Email :tiegen123@126.com

QQ :770811496

QQ交流群:298095983(FPGA&硬件学习交流群)

个人博客:http://www.raymontec.com/

其他博客:http://www.cnblogs.com/raymon-tec由于作者水平有限,文中难免有疏漏或常识性错误,劳烦各位尽情指出。

欢迎大家一同讨论技术,交流设计过程中的经验,共同进步,共同学习。

//===============================================================

****************************************************************/

浙公网安备 33010602011771号

浙公网安备 33010602011771号