USB2.0学习笔记连载(六):USB2.0硬件设计需要注意事项

笔者在设计USB2.0时找到了一个官方给的硬件设计正确设计指南,其中有些内容还挺nice的。不单单只是USB的设计,其中有些思想可以应用到其他的场合中。

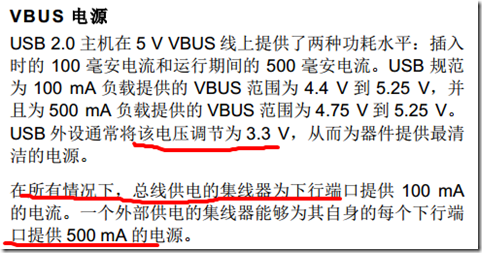

对于USB2.0而言,全速状态下可以达到480Mbps,带宽相比USB1.0提高了不少。USB2.0的供电大功率供电可以达到500mA,实际上加上USB自身消耗,也就是在450~480mA左右。

1.USB供电

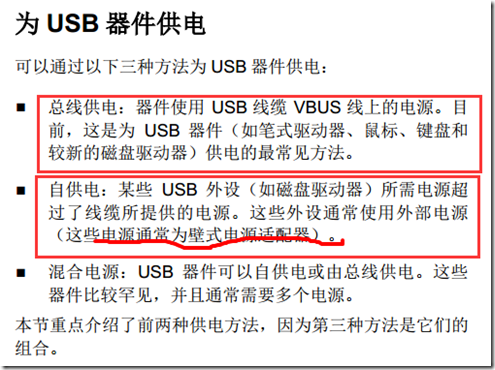

对于外部器件的供电选择,可以使用USB进行供电,也可以自供电。关于USB集线器的介绍参看另外一篇关于USB集线器的介绍。

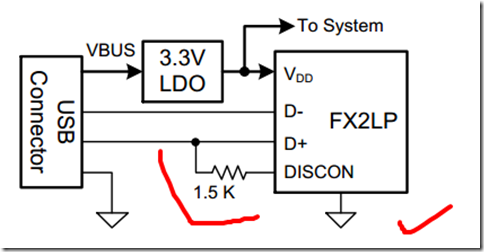

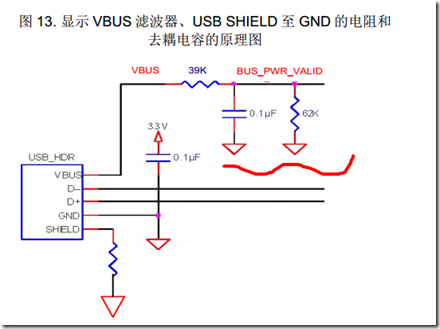

USB进行供电系统架构如下图所示:

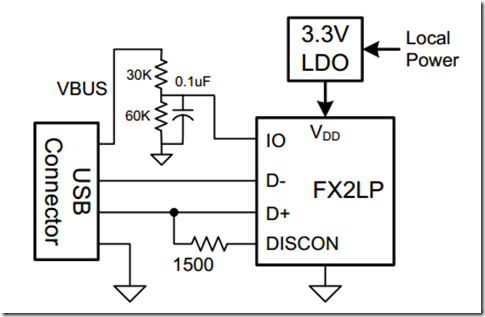

外部器件自行供电USB系统架构如下图所示:

上面两个图是关于VBUS供电的典型应用图,根据手册中的介绍,如果使用了wakeup功能,那么需要使用USB control寄存器来检测VBUS的状态。

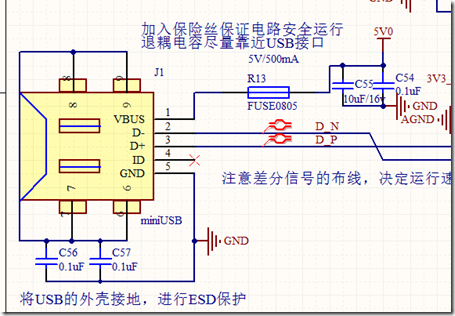

笔者设计的时候,并未采用图上接入1.5K电阻形式,只是让USB提供5V/500mA的电源,电源配置需要在USB固件时进行配置,硬件电路如下图所示:

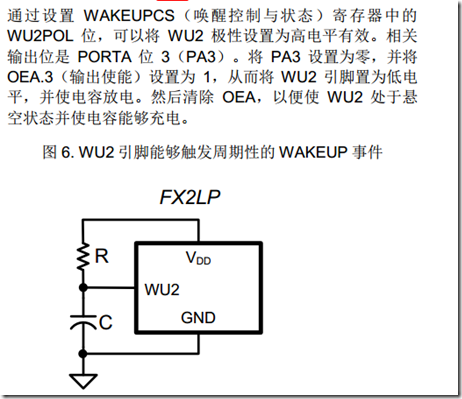

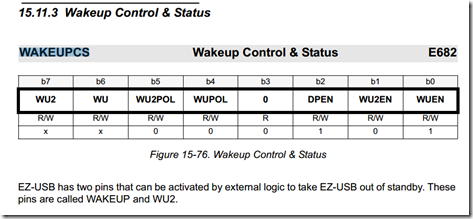

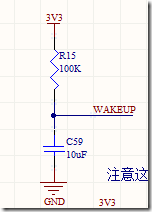

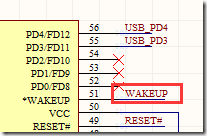

2.WAKEUP引脚设置

笔者设计的电路中,并未提供在无数据传输时进行睡眠,有数据传输时进行唤醒功能,而是一直在唤醒状态。

笔者设计的电路中,并未提供在无数据传输时进行睡眠,有数据传输时进行唤醒功能,而是一直在唤醒状态。

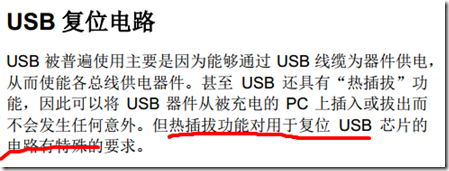

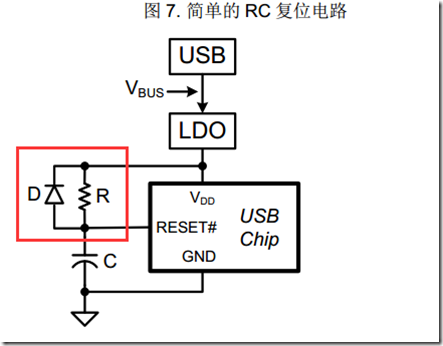

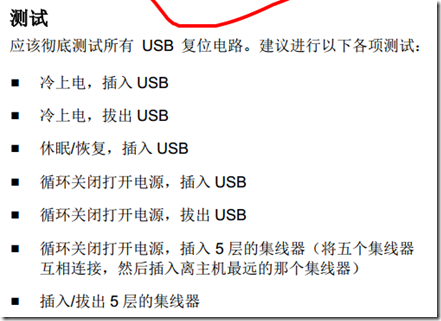

3.USB复位电路

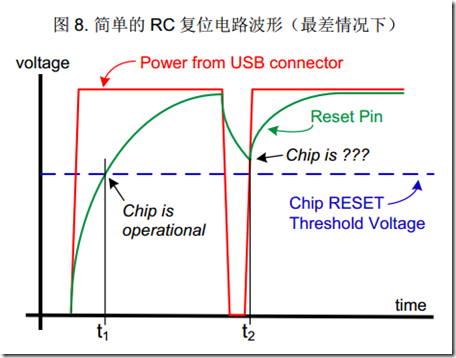

上面几张图手册中提及到对于简单的RC电路进行复位的不足之处。当 USB 器件断开时,芯片被断电,但电容仍持续被充电到芯片的电源电压,然后它通过电阻缓慢放电。如果立即重新插入 USB 器件,会怎么样呢?如果电容放电,但其电压尚未低于复位阈值,那么复位引脚将为芯片供电,但该引脚的电压过高,所以无法在 t2 时复位芯片。暂时可以通过在图 7中添加二极管来解决该问题,从而可以加快掉电时电容电压的放电速度,但只能缩短从断开到重新连接的重要时间。RC 放电方法取决于当 LDO 输入被断连时它的输出电压是否降低到 0 V,而这种情况又取决于特定 LDO 及其外部组件(如大容量电容)。最重要的问题是该电路无法保证芯片

在任何情况下都能可靠地复位,尤其是在 USB 快速断连/连接情况下。

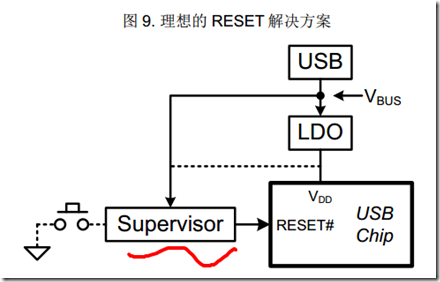

手册中给出了下面理想的复位解决方案,这样当然是最后的结果。

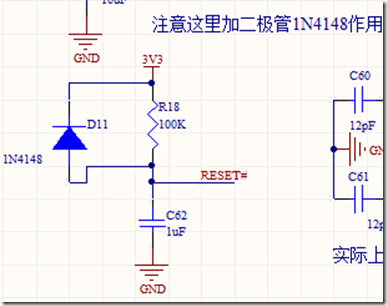

在实际中,笔者测试的情况对于常用的RC电路可以满足本设计的要求,如下图所示:

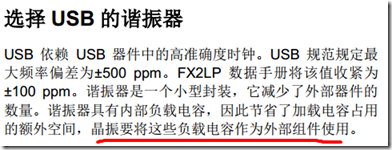

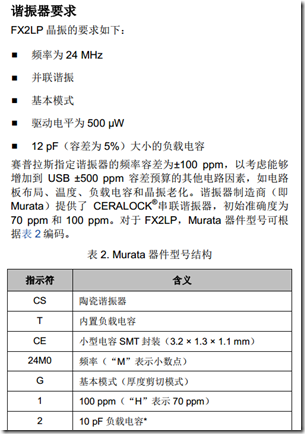

4.晶振要求

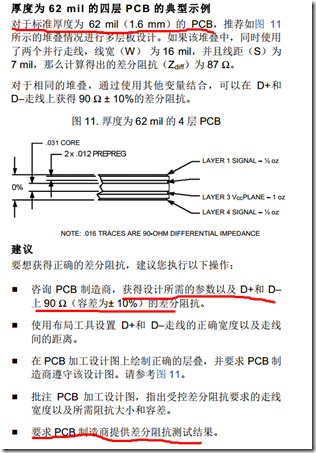

5.USB差分阻抗控制

关于差分阻抗的控制,笔者之前的博客已经说明,可以去查看相关内容,这里简要提及一下。

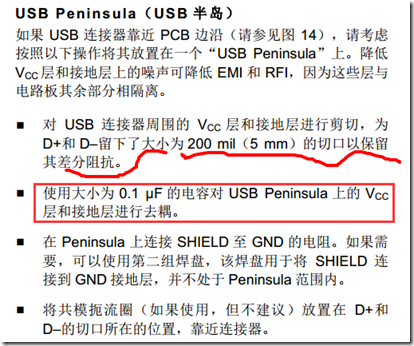

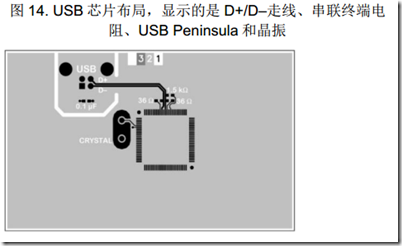

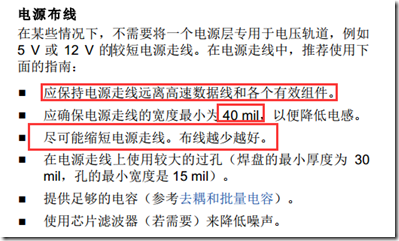

6.PCB设计注意事项

浙公网安备 33010602011771号

浙公网安备 33010602011771号