《FPGA全程进阶---实战演练》之搞定阻抗匹配

笔者最近几天在做视频采集板卡时,视频显示端打算采用 USB2.0接口+上位机 显示,其中USB需要做阻抗匹配。通常情况下USB的阻抗值需要做到90Ω±10%。下面就讲解一下关于阻抗匹配的知识,哪里说得不对的,还望大家批评指正。

在高速电路中,如USB、HDMI、DDR、LVDS设计中往往要注意阻抗匹配问题,高频信号在传输线中传播时所遇到的阻力称为特性阻抗,包括容抗,感抗,阻抗。为了保证信号在传输过程中不发生反射现象,信号尽量保持完整,降低传输损耗,要对印刷电路板进行阻抗匹配。阻抗匹配的目的主要在于传输线上所有高频微波信号都能达到负载点,不会有信号反射回源头。其中通常情况下,USB/DDR的阻抗值保持在90Ω±10%。HDMI/LVDS保持在100Ω±10%。

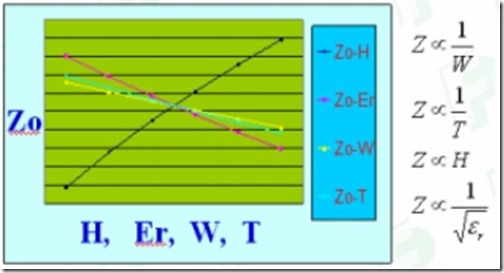

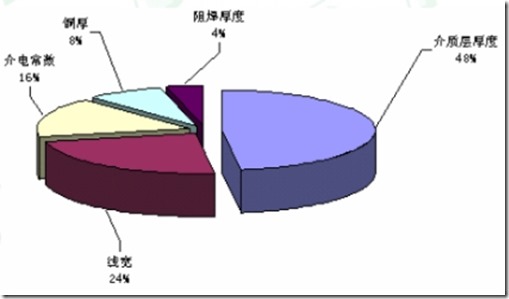

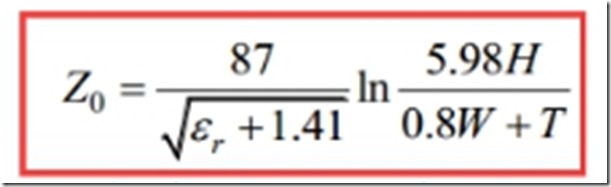

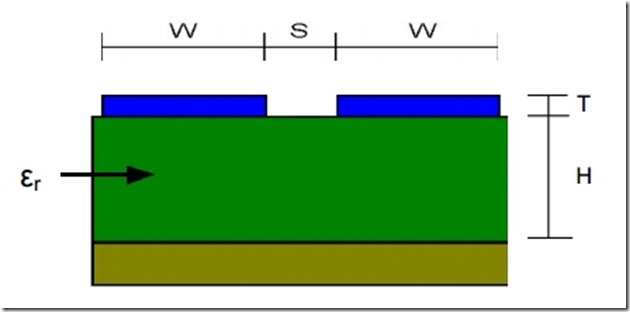

影响阻抗的关键因素如图25.1所示,主要有:线宽(W),线距(S),线厚(T),介质常数(Dk/Er),介质厚度(H),那么阻抗和线宽(W),线距(S),线厚(T),介质常数(Dk/Er)成反比,和介质厚度(H)成正比。

图25.1 阻抗影响因素

图25.2 阻抗相关因素

阻抗匹配的方法:1.凭经验值;2.交给PCB厂商;3.结合SI9000进行系统的理论计算。那么本节主要是讲解关于SI9000的使用。

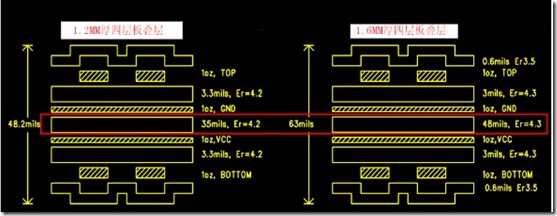

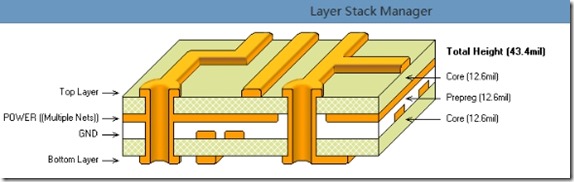

图25.3所示是不同板厚各参数的设置,此图不是标准,仅此作为讲解用,由图中可见1.2mm厚的板子和1.6mm的板子也就是绝缘层的厚度不一样而已,其他参数保持一致。若是用过Altium的朋友,应该还记得在设置层的时候,有一个core和Prepreg,如图25.4所示,core和prepreg的区别在于,虽都是绝缘材料,但core可以两面均有铜箔走线,prepreg为纯绝缘材料,不走任何铜箔线。

图25.3 四层板不同板厚各参数

图25.4 altium中四层板各参数

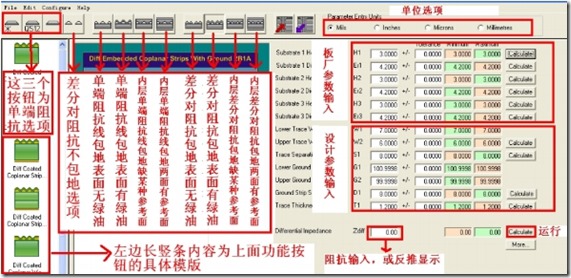

图25.5 是SI9000界面的一些介绍。

图25.5 SI9000界面

通常会将电源层和地层作为信号层电流回流路径和阻抗参考层,一般采用地层作为参考层或电流回流路径。如果必须采用电源层作为参考或信号回流的路径,注意不要让高速信号走线耦合噪声到电源平面。

那么下面就结合基于USB视频采集板卡说明一下阻抗的计算以及线宽和间距问题。

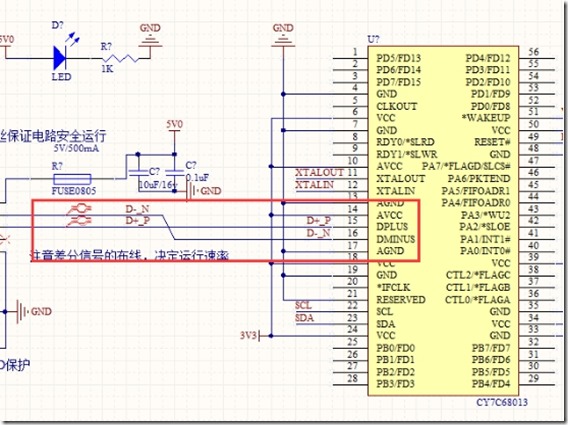

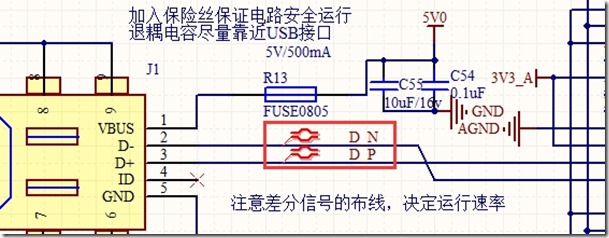

图25.6 USB2.0硬件搭建

如上图25.6所示是USB2.0硬件电路图,其中DPLUS和DMINUS布线的好坏直接决定了最终的传输速度。关于USB硬件布线以及相关的设计,读者可以参考Cypress相关文件内容。如图25.7所示。

图25.7 相关参考资料

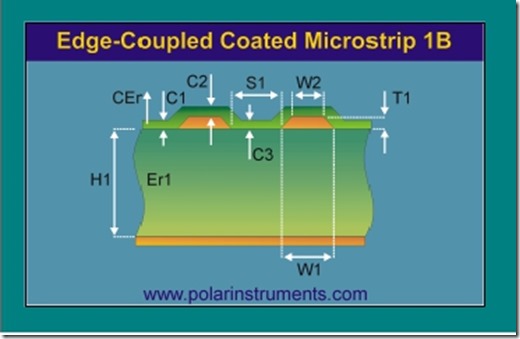

在PCB面板上,USB的D+(DPLUS)D-(DMINUS)就是两根导线,一般平行放置,影响D+(DPLUS)与D-(DMINUS)差分阻抗的因素和之前提到的一样。

借助电磁波原理中微波传输带的2D模型来计算,单根阻抗计算公式如下:

差分阻抗模型如下图25.8所示。

图25.8 差分阻抗模型

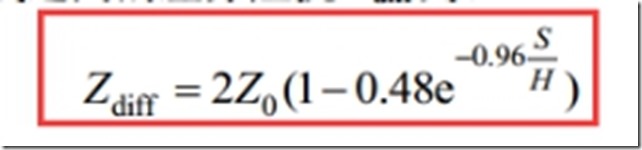

差分阻抗计算公式如下:

了解了上述的原理之后,我们可以直接采用SI9000此软件去计算,不用去记住那些繁琐公式,不过从上述公式中,也可以看出阻抗的影响因素和一开始提到的影响因素是一致的。

笔者设计的四层板的排列方式:top layer(signal layer)---power plane (inner plane)---GND layer ---bottom layer (signal layer),所以笔者在计算阻抗时,电源层和地层均可选择参考平面,上下对称,所以计算top layer(signal layer)---power plane (inner plane)即可,当然也可以计算GND layer ---bottom layer (signal layer)。

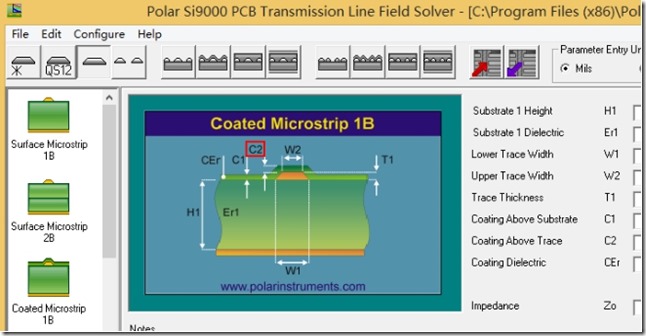

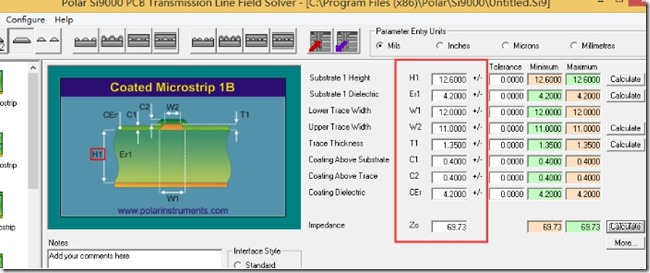

打开SI9000软件(软件可以网上下载),先计算单端阻抗,实际的模型中,厂商往往会在顶层涂一层绿油,所以实际模型如下图25.9所示:

图25.9 单端阻抗

笔者设计的单端阻抗相关参数如图25.10所示,计算出来的结果是单端阻抗值69.73,一般情况下,单端阻抗要保留一定的余量。笔者tolerance一项没有设置,这个具体应该要和PCB厂商沟通,所以此参数能够满足我们设计的要求。

图25.10 单端阻抗参数

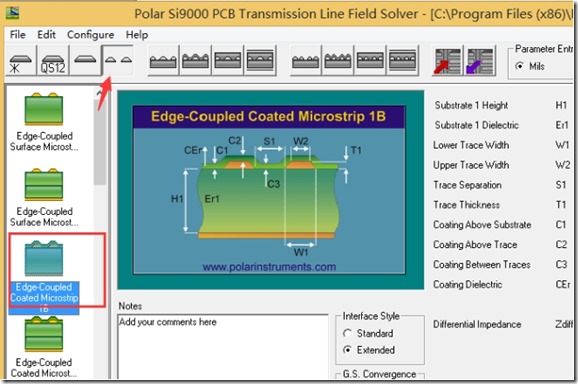

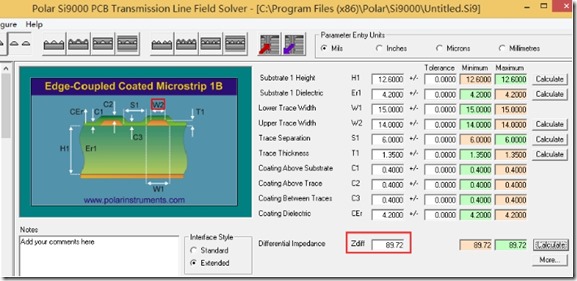

单端阻抗搞定之后,接下来需要计算差分阻抗,这个参数尽量要保持在90Ω±10%范围内。SI9000选择界面如图25.11所示。

图25.11 差分阻抗

设计好之后需要设置相关参数,如下图25.12所示:

图25.12 差分阻抗相关参数

间距为6mil,线宽为15mil,core层的厚度为12.6mil,计算出来的结果为89.72Ω,满足在90Ω±10%范围内。

计算完上述参数之后,就要开始布线,那么在原理图中需要设置差分对。如图25.13所示。定义方式为在菜单栏中选择 place ---directives ---differential pair即可,还需要注意的是,在命名时需要定义为*_N和*_P的格式,其中N和P部分大小写。

图25.13 差分对的定义

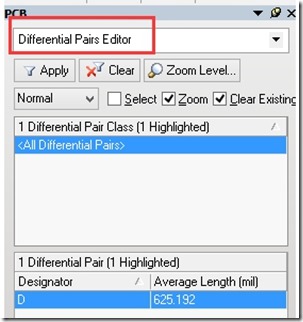

定义完参数之后,需要对差分对的规则进行设置,如图25.14所示,点击rule wizard。

图25.14 规则设置

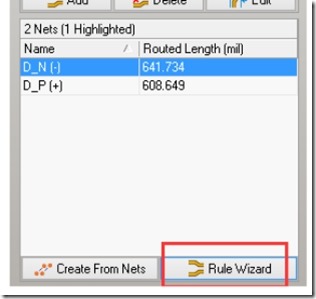

根据上面的计算,线宽为15mil最好,所以设置线宽为15mil。

图25.15 线宽设置

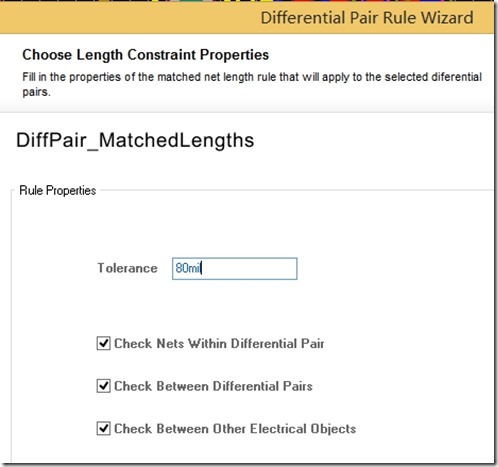

考虑到PCB布线时,D+(DPLUS)和D-(DMINUS)线的长度小于70mm,以20~30mm较宜,并且D+(DPLUS)和D-(DMINUS)线的长度差应尽量小于2mm,防止信号时滞。所以在图25.16中所示,换算成mil值为80mil。

图25.16 允许长度差范围

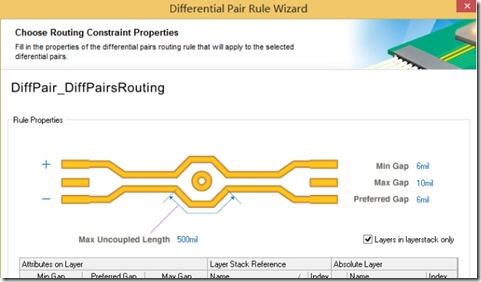

图25.17为间距设置,优选6mil间距。

图25.17 间距设置

接下来利用差分对布线功能布线即可。

浙公网安备 33010602011771号

浙公网安备 33010602011771号