GT高速收发器 杂谈

深入解析GTX收发器的时钟架构与数据位宽关系(高速收发器四)

DDR速率如何计算?

常见的DDR4-3200,其中DDR4代表第四代双倍速率同步动态随机存取存储器(Double Data Rate 4 Synchronous Dynamic Random Access Memory)。3200表示其数据传输速率为3200 MT/s(百万次传输每秒)。需要注意的是,有效数据传输频率为3200 MT/s,并不等同于内存的实际工作频率。实际内存频率为3200 MT/s ÷ 2(因为DDR在时钟的上升沿和下降沿均传输数据),即1600 MHz。

(1) 核心频率:真实运行频率。

(2) 倍增系数:DDR通过数据预取技术放大速率,每代ddr倍率是固定的,ddr2=4, ddr3=8, ddr4=8, ddr5=16

(3) 有效频率;厂商标注的频率,可以理解为数据传输速率。厂商也想逐步淡化其它频率的概念,只让我们记住有效频率。其实有效频率就是核心频率*倍增系数得来的,在理想情况下能代表我们内存数据传输频率。

(4) IO频率:又叫时钟频率,它是有效频率的一半。

根据DDR频率计算带宽

传输带宽 = 2 * DDR频率 * 通道位宽 / 8 //乘以2是因为上升沿和下降沿都传输数据

常见的DDR4-3200,其中DDR4代表倍增系数为2^4,有效数据传输频率即3200MHz

传输带宽

传输带宽 = 有效频率 * 通道位宽 / 8 //8是因为bit到byte的转换

DDR5-6400双通道LPDDR5的传输带宽 6400 * 4*32 / 8 = 96GB/s

其中,位宽(bit width)指的是内存总线的位宽,如64位、128位、16位、32位等。主频指的是DDR内存的实际主频(即有效数据传输频率÷2),而不是DDR内存的标称传输速率。因此,在计算理论带宽时,需要将实际主频和位宽相乘并除以8,以转换为字节。例如,以1600 MHz主频,64位位宽为例,计算公式为:

带宽 = (1600 MHz × 64 bit) / 8 = 12800 MB/s = 12.8 GB/s

这里的MB/s指的是兆字节每秒,GB/s指的是千兆字节每秒。

另外,如果使用双通道内存,因为位宽翻倍,所以带宽也会相应翻倍。例如,若上述内存为双通道,则带宽为:

带宽 = 12800 MB/s × 2 = 25600 MB/s = 25.6 GB/s

另外说一下,DDR是Double Data Rate的缩写,它在时钟上升沿和下降沿分别采集数据,DDR4内存的全称是DDR4 SDRAM。

可能会有人好奇,我们见过DDR2、DDR3、DDR4,是否有DDR1呢?其实有的,这就要提到DDR的上一代,SDR(Single Data Rate),它只在时钟信号上升沿采集数据,这就是SDR SDRAM,也就是DDR的前身。我们有些开发板上面所带的就是SDRAM。

所以总结来说,各代内存如下:

- SDR SDRAM

- DDR SDRAM

- DDR2 SDRAM

- DDR3 SDRAM

- DDR4 SDRAM

- DDR5 SDRAM

什么是GT收发器

GT(Gigabit Transceiver)收发器是一种高速串行通信接口,是硬核资源的一部分。

GTX、GTH、GTZ、GTY是不同类型的GT收发器,主要区别在于支持的速率和特性:

- GTX:适用于中速率应用,通常支持速率从几百Mbps到10Gbps。

- GTH:适用于更高速率的应用,支持速率从几Gbps到16Gbps。

- GTZ:针对超高速应用,支持速率高达28Gbps。

- GTY:支持最高速率,通常可达32Gbps或更高,适用于最苛刻的高速通信需求。

在低速通信场合,通常使用GPIO(通用输入输出)进行通信。这些接口可以直接使用I/O引脚,不需要特殊的编码(什么是编码,我发1,收到就是1,发0,收到的就是0,这就是无编码)。常见的低速通信协议I2C、SPI(同步)、UART(异步),通常采用CMOS或TTL电平标准,直接通过I/O引脚集成。

高速通信

高速通信不同于低速通信的同步或者异步,需要采用更加复杂的技术来保证数据传输的完整性和可靠性,为什么呢?因为有时候时钟和数据在发送之前已经自带时钟偏斜了,会对信号传输产生限制,所以有没有方法避免时钟偏斜呢?有的,时钟恢复技术CDR(Clock Data Recovery)应运而生。通过CDR技术,可以从接收到的数据流中恢复出时钟信号,从而减少对单独时钟线的布线要求,解决时钟与数据之间的对齐以及layout问题。某些情况下时钟恢复非常方便,如01010101,可以很清晰的看到时钟周期的变化。但是如果数据是0000001,就不方便进行数据恢复,此时,就提出了编码,编码可以使得数据流不断得出现上升沿和下降沿,从而方便时钟信号的恢复。

另外高速接口电路一般采用交流耦合方式进行连接,在交流耦合电路中的信号线会接电容(隔直通交),如果传输的数据在一段时间内全是1或全是0,那么这段时间传输的信号可以等效成直流信号,会产生直流偏移,在通过电容时,有可能解码错误。

8b/10b编码把8比特的子元转换成10比特的子元。目的是以便在串行传输中达到直流平衡(DC Balance),明晰边界,并提供足够的状态改变来利于时钟恢复。目标是至少在20比特“1”的个数与“0”的个数的差距不超过2个,并且没有连续的5个“1”或“0”。因此通过8B10B编码,保证编码后的数据在一定时间内0的个数与1的个数保持相等。

8b/10b编码将一组8位资料分成两组,一组3比特,一组5比特,经过编码后形成一组4位和一组6比特,故送发时是一组10比特的资料,解码时再将10比特的资料变换得到8位资料。编码过程中低位5比特的资料会进行5B/6B编码,高位3比特的资料则进行3B/4B编码。

例如一组8位的资料是 10110101:

首先,分成两组 101 与 10101

a=10101(21) b=101(5),符号为 D21.5,在编码表中的位序为HGFEDCBA,a(EDCBA)经过5B/6B编码为abcdei,b(HGF)经过3B/4B编码为fghj。

按照k7系列为例具体可以参见以下文档

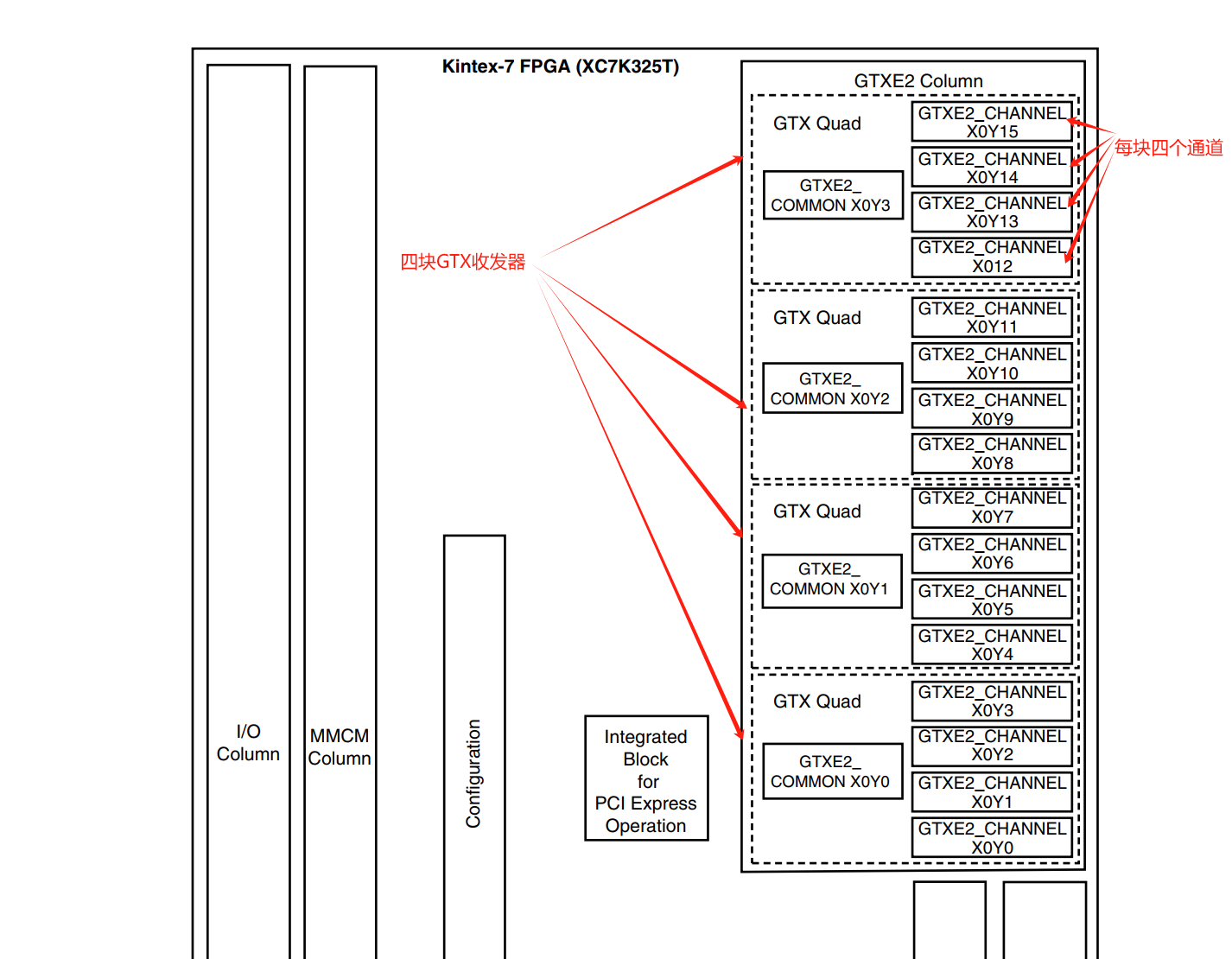

其中GTXE2_COMMON X0Y3包含了时钟资源

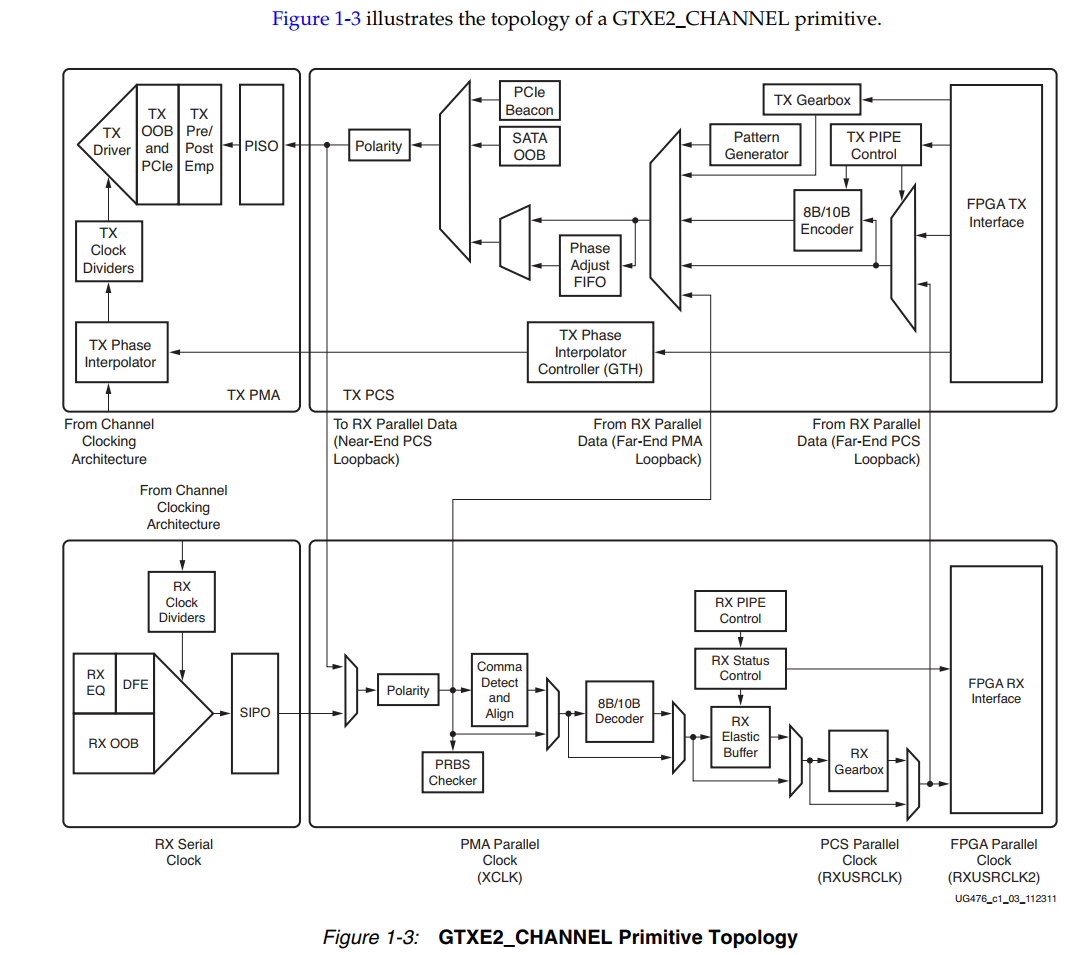

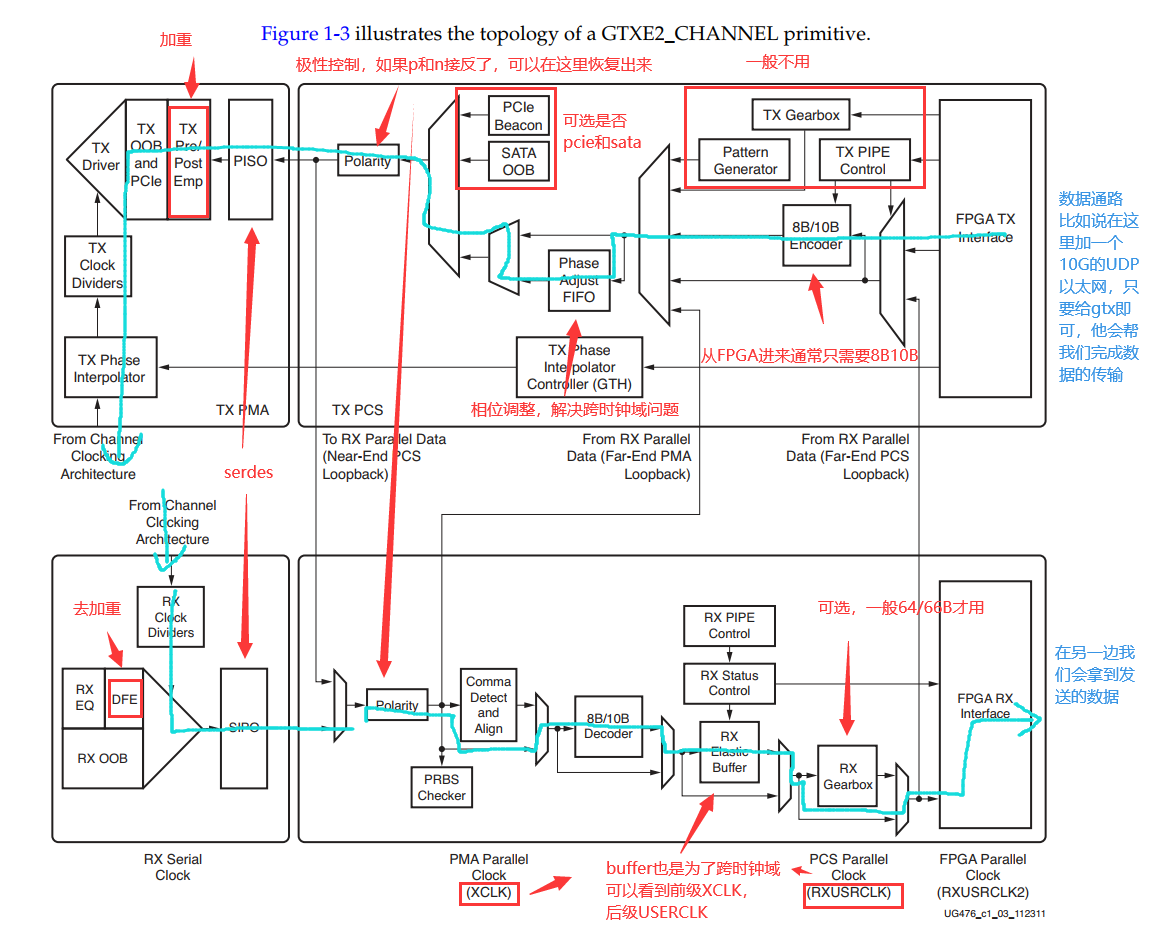

GT收发器结构

GT收发器结构大致可以分为PMA(Physical Medium Attachment)和PCS(Physical Coding Sublayer),是PHY层的一部分

PMA是指物理层中的模拟电路部分,负责物理信号的发送和接收。

- 信号调理:对传输信号进行放大、滤波等处理

- 时钟恢复:从接收到的信号中恢复出时钟信号

- 串行化/解串行化:负责将并行数据转换为串行数据并发送出去,或将接收到的串行数据转换为并行数据

PCS是指物理层中的数据逻辑电路部分,负责数据编码和解码

- 数据编码:将数据编码为适合传输的格式,8b/10b编码、64b/66b编码等

- 数据解码:将接收的数据解码回原始格式

- 误码校正:检测并纠正传输过程中的错误

PISO(Parallel Input Serial Output)是一种数据转换技术,用于将并行数据转换为串行数据,SerDes(Serializer/Deserializer)是PISO的一种实现形式,与之对应的还有SIPO

加重是一种信号处理技术,目的是在发送端对信号进行预处理,使数据跳变更加明显,从而在接收端更容易恢复出原始信号

DFE是一种均衡器,用于在接收端对信号进行处理,以去除传输过程中累积的干扰和加重

以上只是简略的框图,详细可以看以下两个推文,写的很好

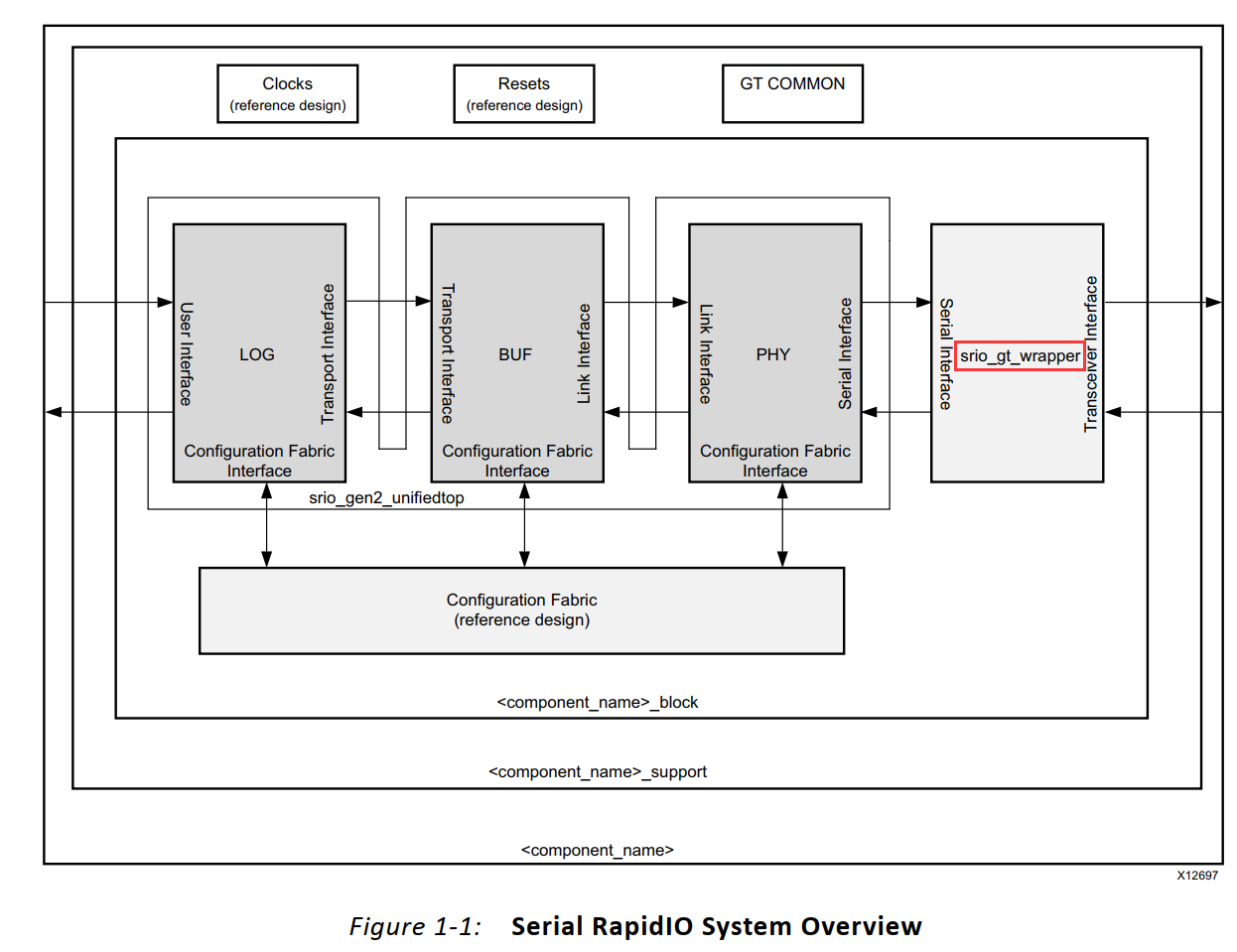

SRIO

SRIO传输需要借助高速收发器

官方文档如下

cnblogs_documents/pg007_srio_gen2.pdf at master · Radiumlrb/cnblogs_documents (github.com)

优秀推文可以阅读

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· 震惊!C++程序真的从main开始吗?99%的程序员都答错了

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

2021-05-06 如何快速设计一个FIR滤波器 Label:Research