Microsemi Libero SoC使用教程(胎教级 免费)(创建工程、引脚分配、仿真、逻辑分析仪ILA)

Libero SoC是一款集成了多种功能的FPGA开发软件,可以用来设计、仿真、综合、布局、布线、下载和调试FPGA项目。

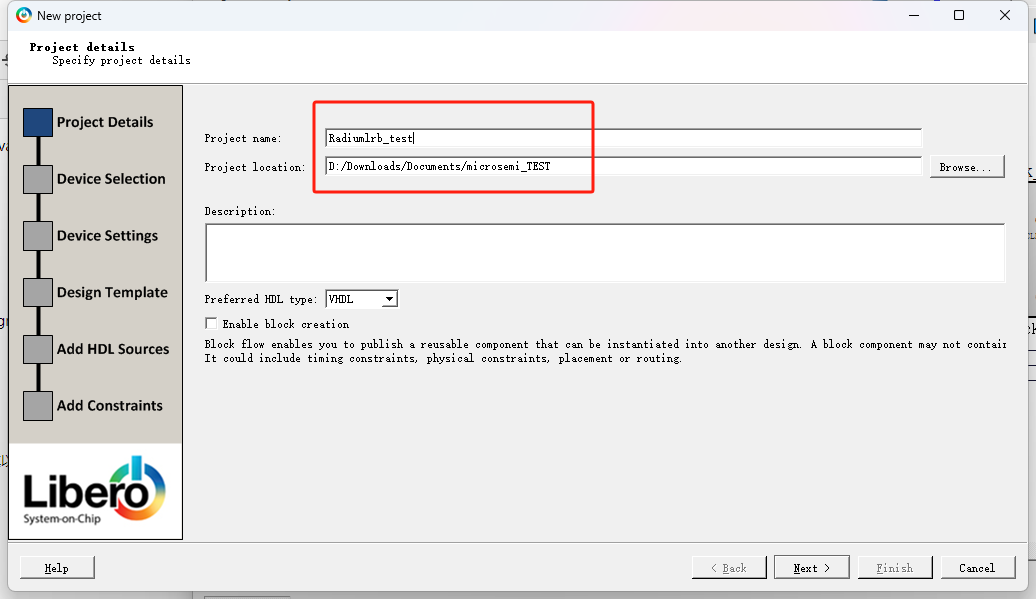

1、新建工程

首先,我们需要新建一个工程,点击File->New Project,然后给工程取一个名字,选择工程的存放路径,点击Next。

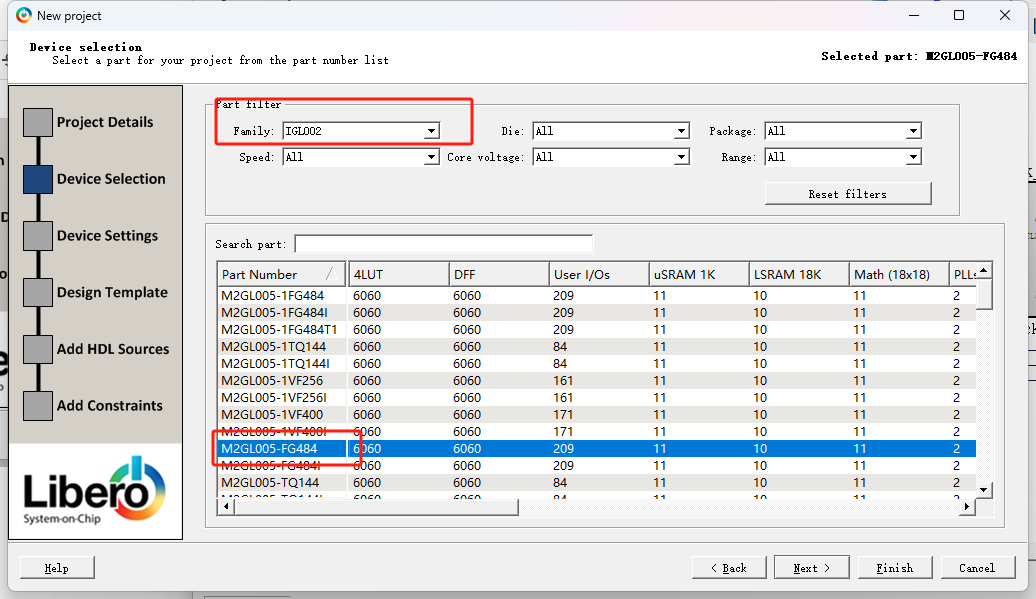

接下来,我们需要选择FPGA的family和芯片型号

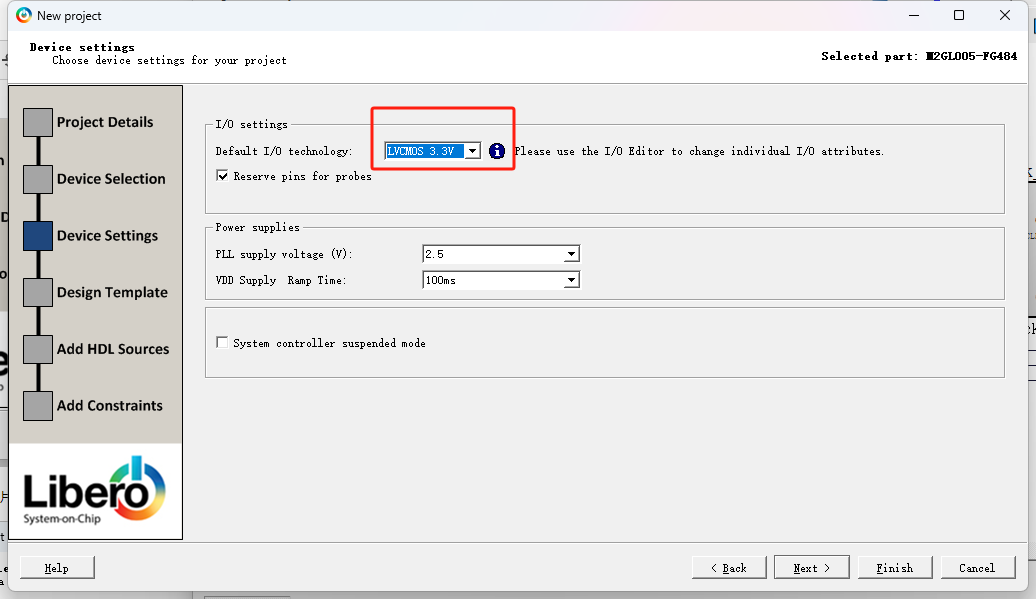

然后,我们需要更改电压,这里我选择了3.3V,点击Next。

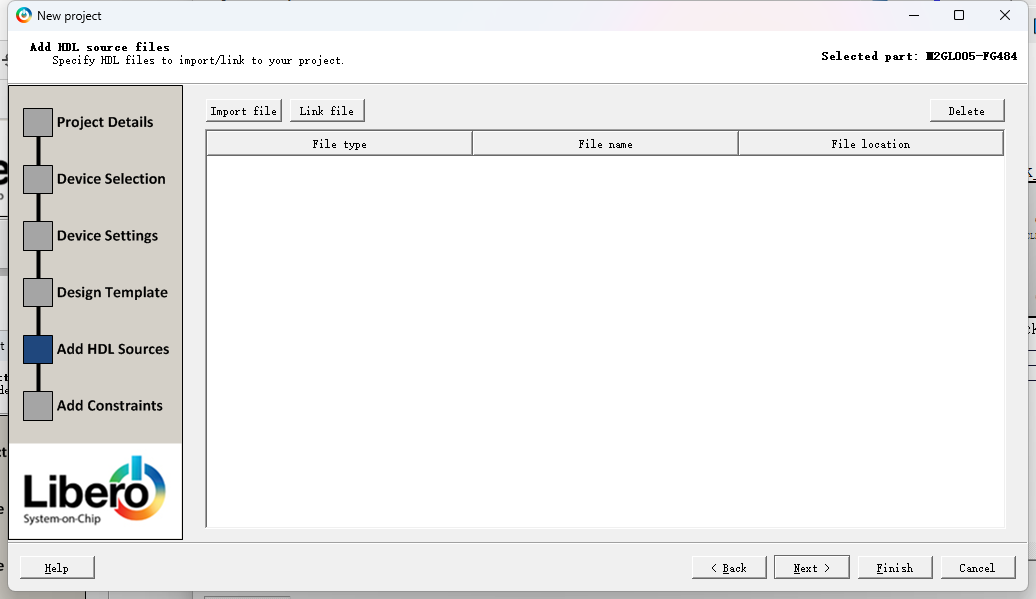

如果我们有已经编写好的HDL文件,可以在这里导入,点击Add Files,选择HDL文件,点击Next。如果没有,可以跳过这一步。

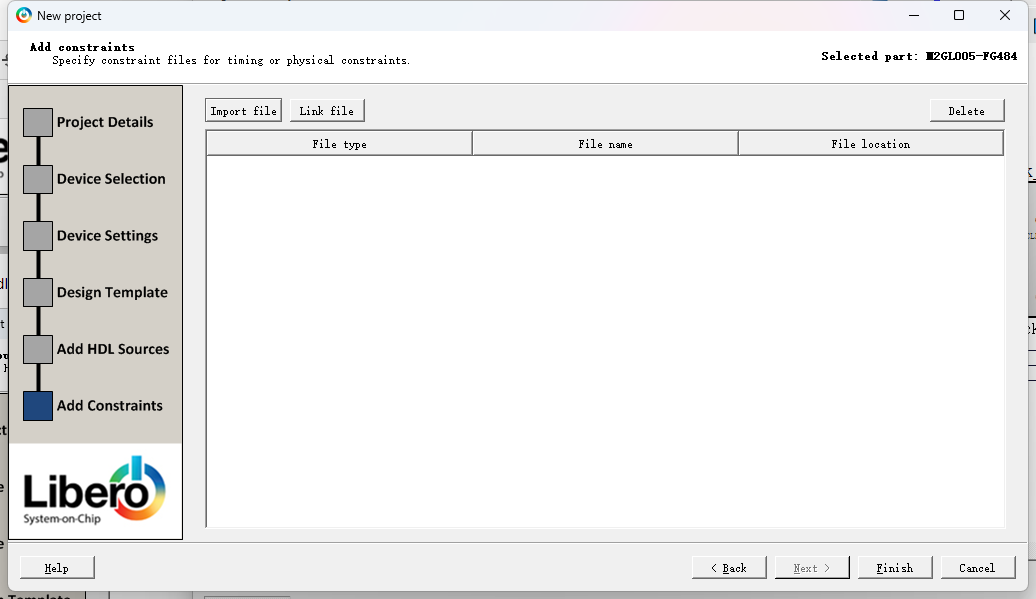

如果有编写好的PDC约束文件,可以在这里导入,点击Add Files,选择PDC文件,点击Next。如果没有,可以跳过这一步。最后,点击Finish,就完成了工程的新建

2、创建HDL文件

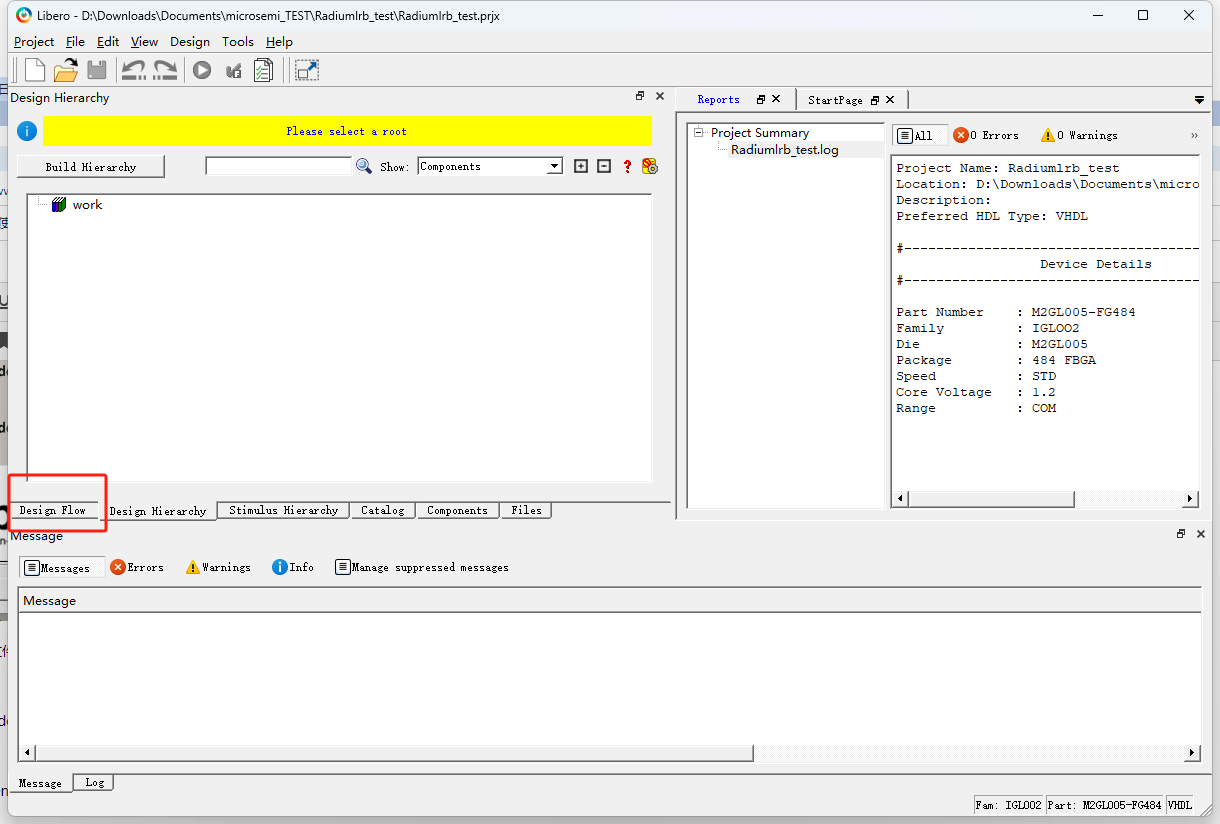

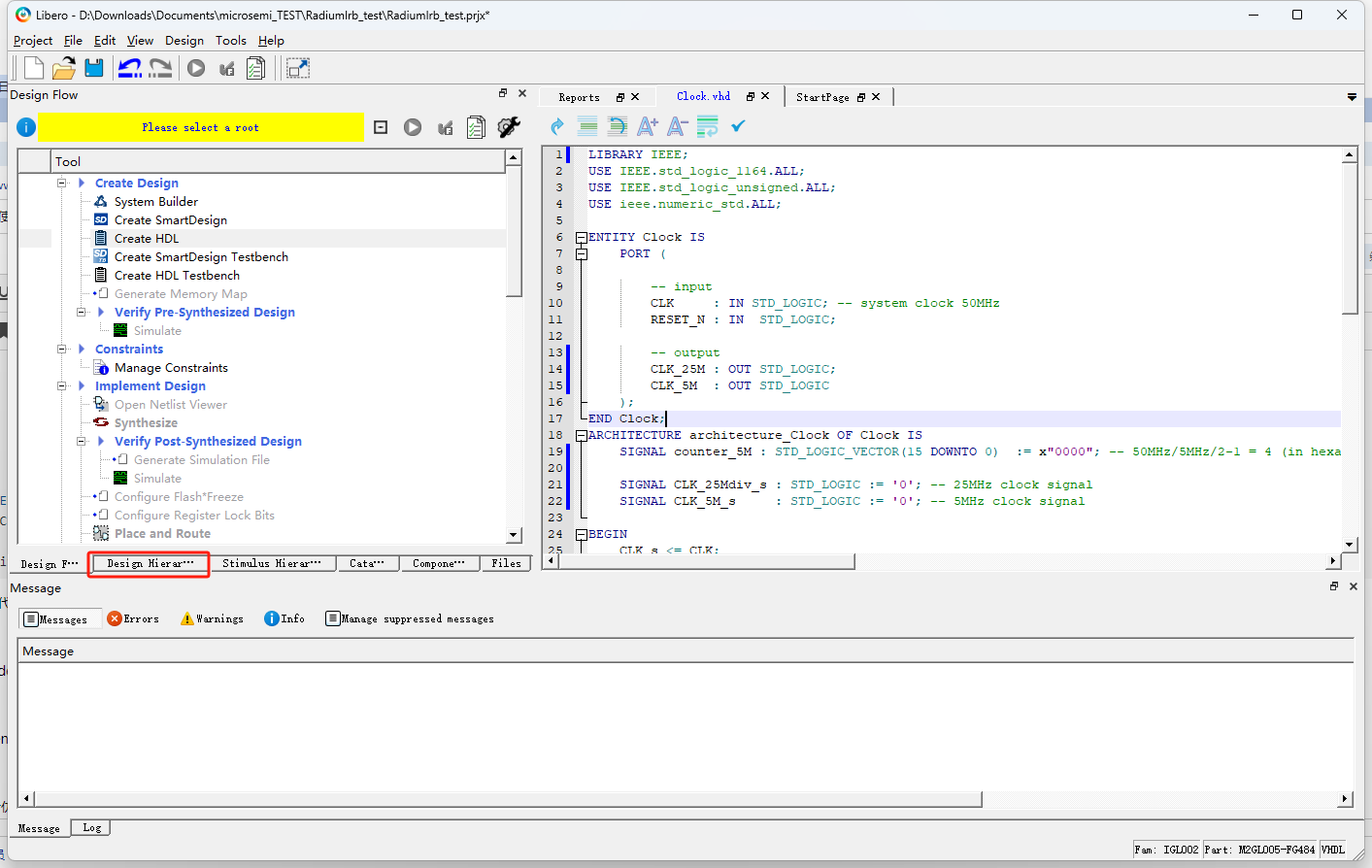

创建工程完成后,我们可以看到如下图的界面,这里我们可以看到Design Flow,这是Libero SoC的核心功能,它可以帮助我们完成从设计到下载的整个流程。

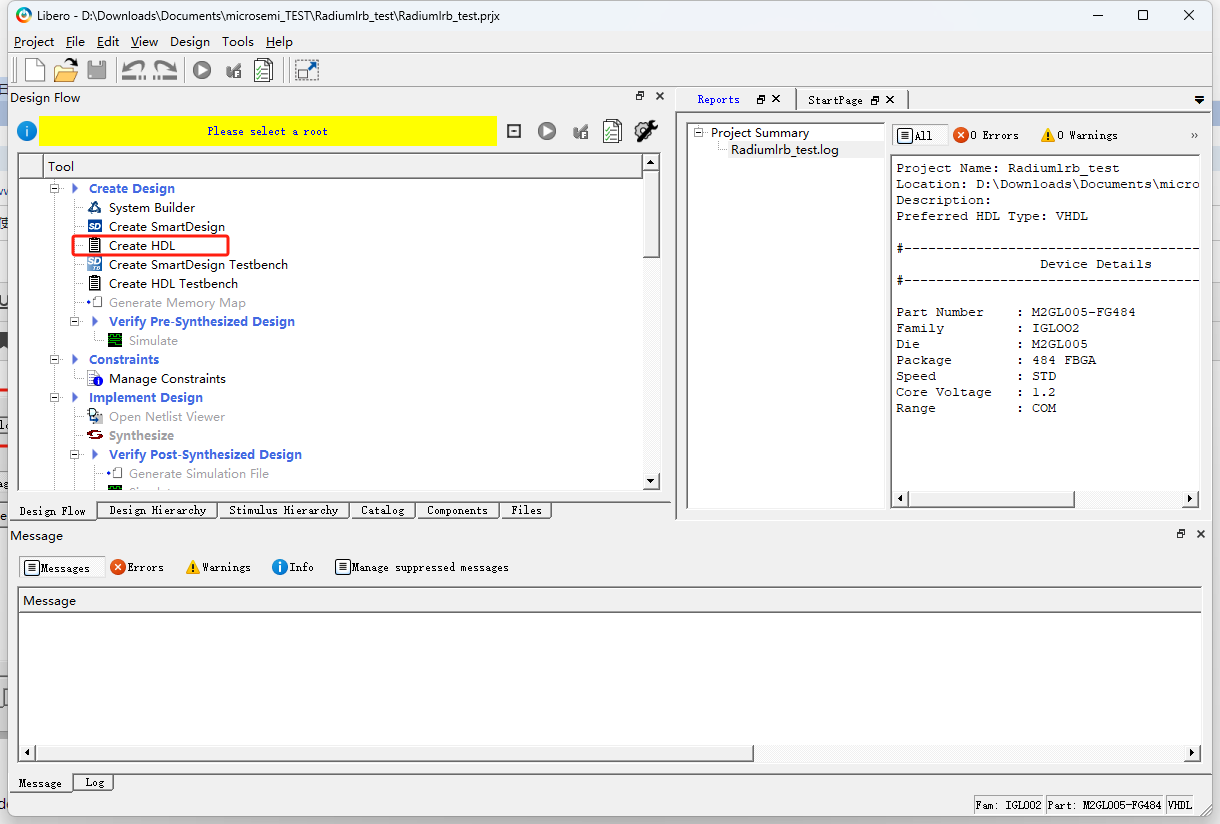

我们先来创建一个HDL文件,点击Design Flow中的Create HDL

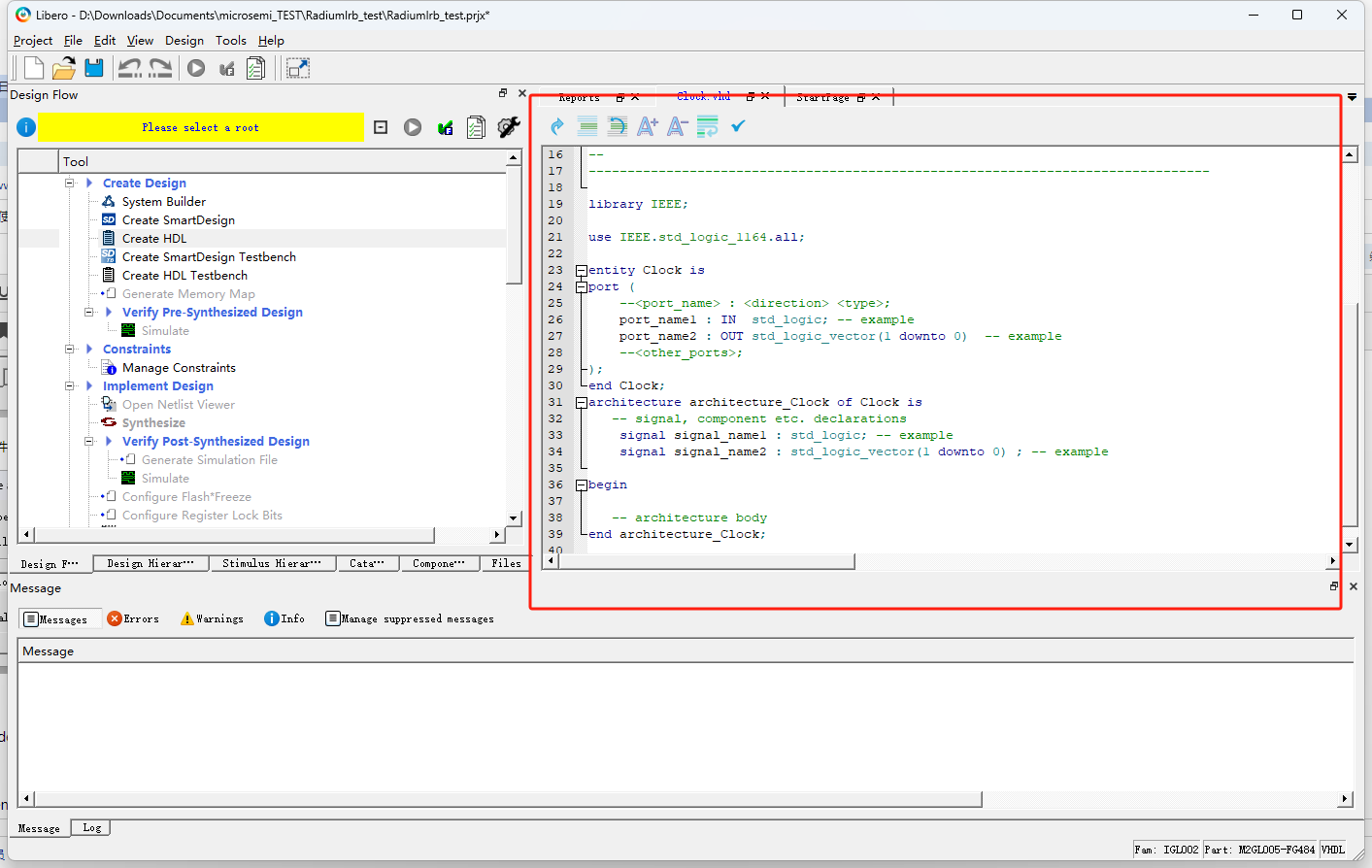

然后给HDL文件取一个名字,然后选择HDL的语言,这里我选择了VHDL,还可以选择是否使用模板创建,使用模板创建文件会给出最基础的代码结构,点击OK。

可以看到,Libero SoC自动为我们生成了一个VHD文件,最基础的代码结构已经给出,包括了模块名、端口定义、参数声明等,我们只需要在这个基础上编写我们的逻辑代码即可。

这里我编写了一个简单的时钟分频器的代码,输入50MHz的时钟,分配输出25MHz和5MHz两种时钟,代码如下:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_unsigned.ALL;

USE ieee.numeric_std.ALL;

ENTITY Clock IS

PORT (

-- input

CLK : IN STD_LOGIC; -- system clock 50MHz

RESET_N : IN STD_LOGIC;

-- output

CLK_25M : OUT STD_LOGIC;

CLK_5M : OUT STD_LOGIC

);

END Clock;

ARCHITECTURE architecture_Clock OF Clock IS

SIGNAL counter_5M : STD_LOGIC_VECTOR(15 DOWNTO 0) := x"0000"; -- 50MHz/5MHz/2-1 = 4 (in hexadecimal 0x0004)

SIGNAL CLK_25Mdiv_s : STD_LOGIC := '0'; -- 25MHz clock signal

SIGNAL CLK_5M_s : STD_LOGIC := '0'; -- 5MHz clock signal

BEGIN

------------------25MHz clock divider---------------------------

clock_25Mdivider : PROCESS (RESET_N, CLK)

BEGIN

IF (RESET_N = '0') THEN

CLK_25Mdiv_s <= '0';

ELSIF rising_edge(CLK) THEN

clk_25Mdiv_s <= NOT clk_25Mdiv_s;

END IF;

END PROCESS clock_25Mdivider;

CLK_25M <= CLK_25Mdiv_s;

------------------5MHz clock divider---------------------------

clock_5Mdivider : PROCESS (RESET_N, CLK)

BEGIN

IF (RESET_N = '0') THEN

counter_5M <= x"0000";

CLK_5M_s <= '0';

ELSIF rising_edge(CLK) THEN

IF counter_5M = x"0004" THEN

counter_5M <= x"0000";

CLK_5M_s <= NOT CLK_5M_s; -- Toggle the 5MHz clock

ELSE

counter_5M <= counter_5M + '1';

END IF;

END IF;

END PROCESS clock_5Mdivider;

CLK_5M <= CLK_5M_s;

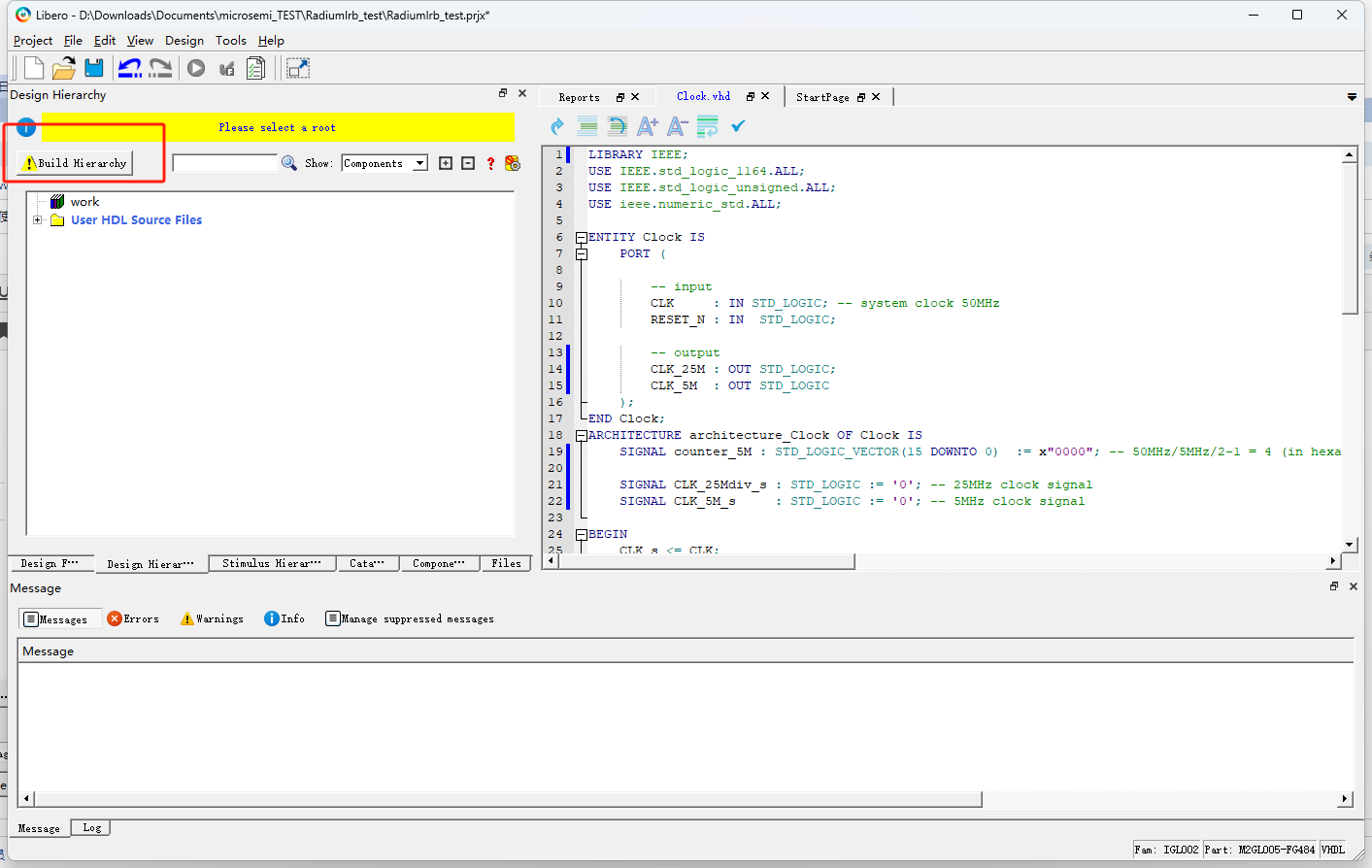

END architecture_Clock;编写完成后,我们按Ctrl+S保存代码,然后回到Design Hierarchy,这里我们可以看到我们的工程结构,包括了我们创建的HDL文件和SmartDesign文件

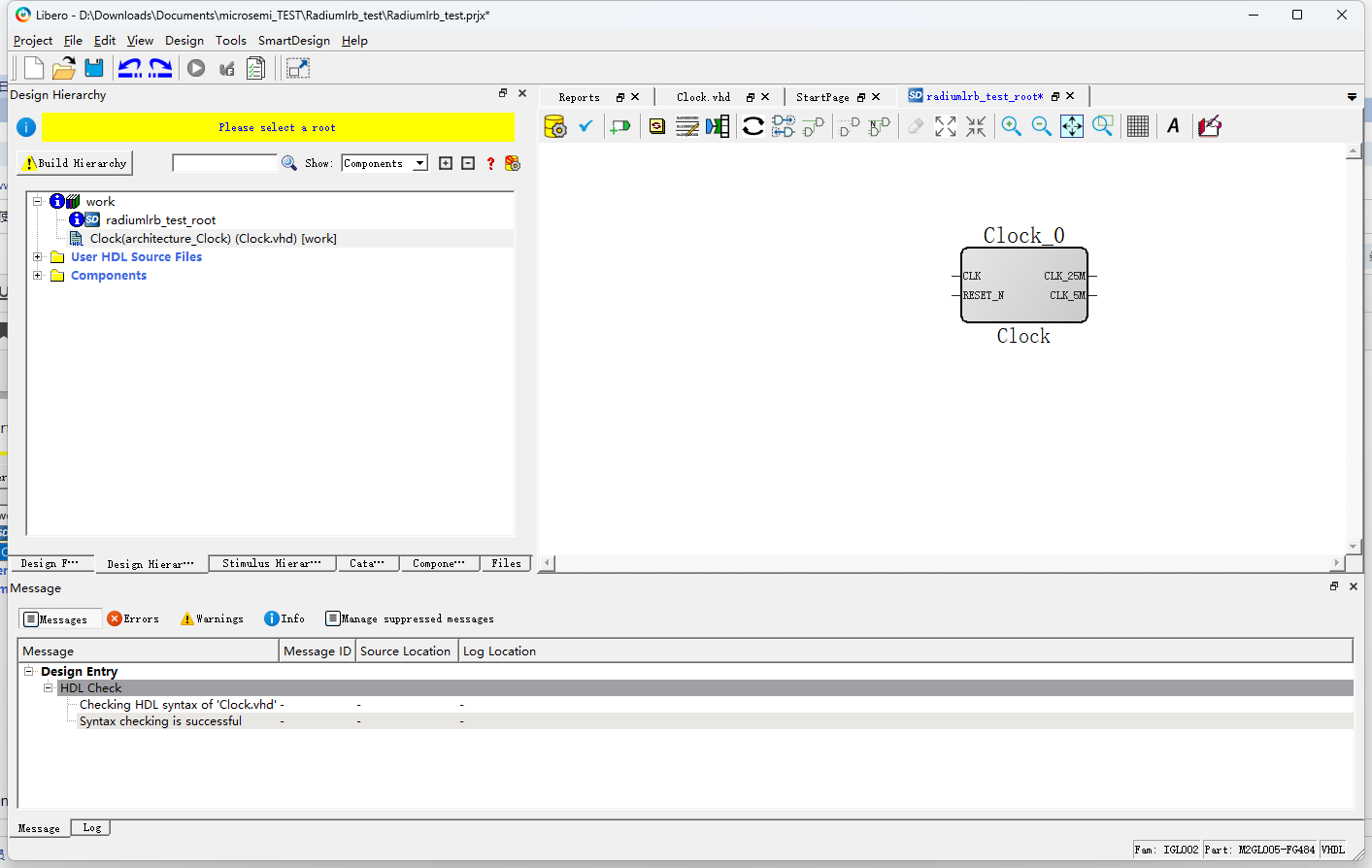

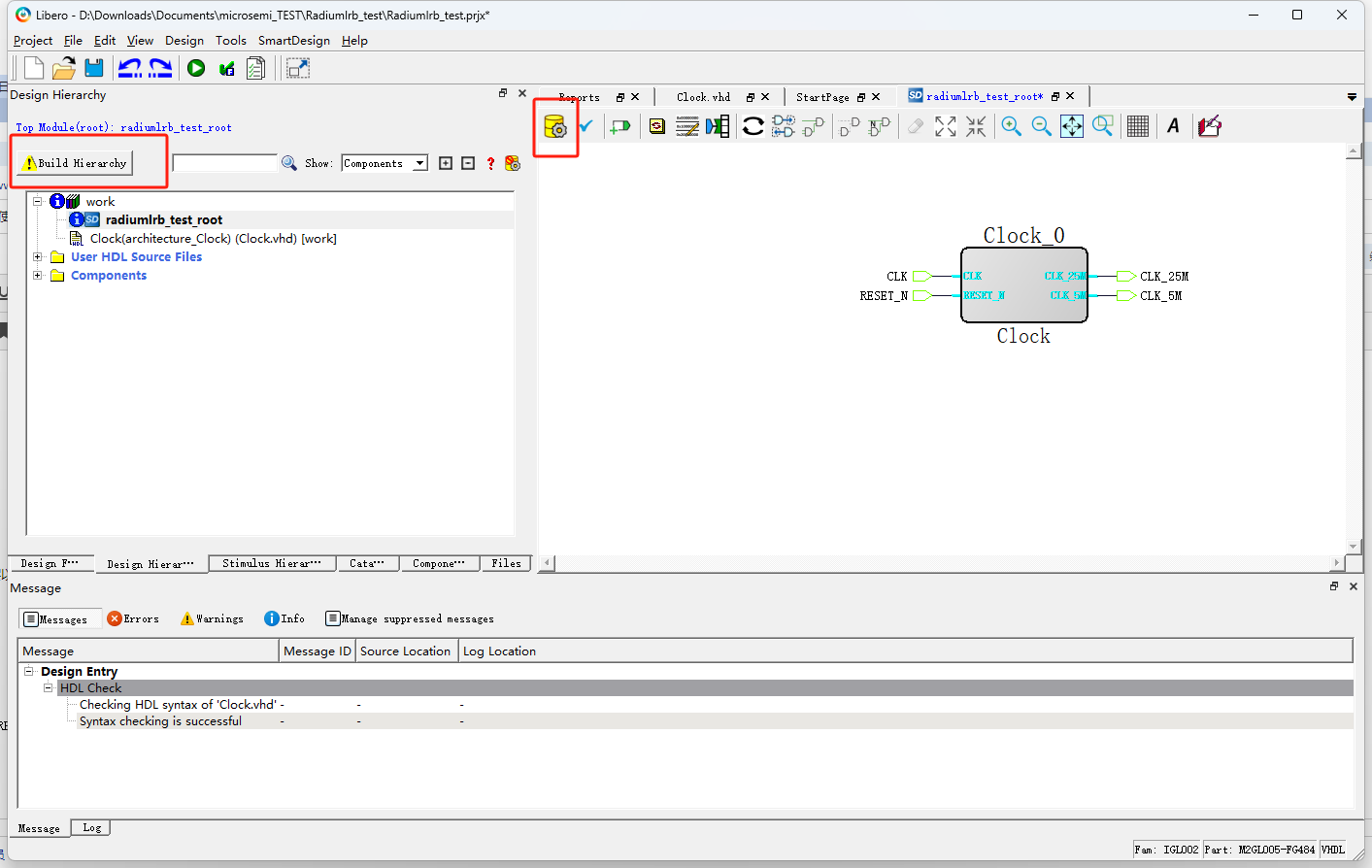

我们点击Build Hierarchy,这样就可以让Libero SoC识别我们的HDL文件,并将其显示在树级结构中,这样我们就可以对其进行进一步的操作。

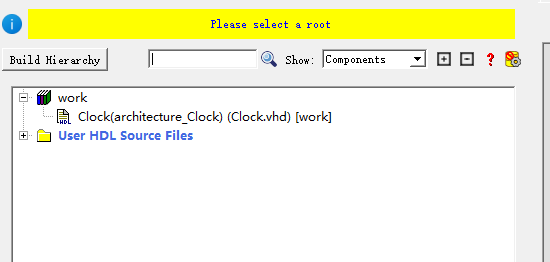

可以看到hdl文件已经成功显示在树级结构中

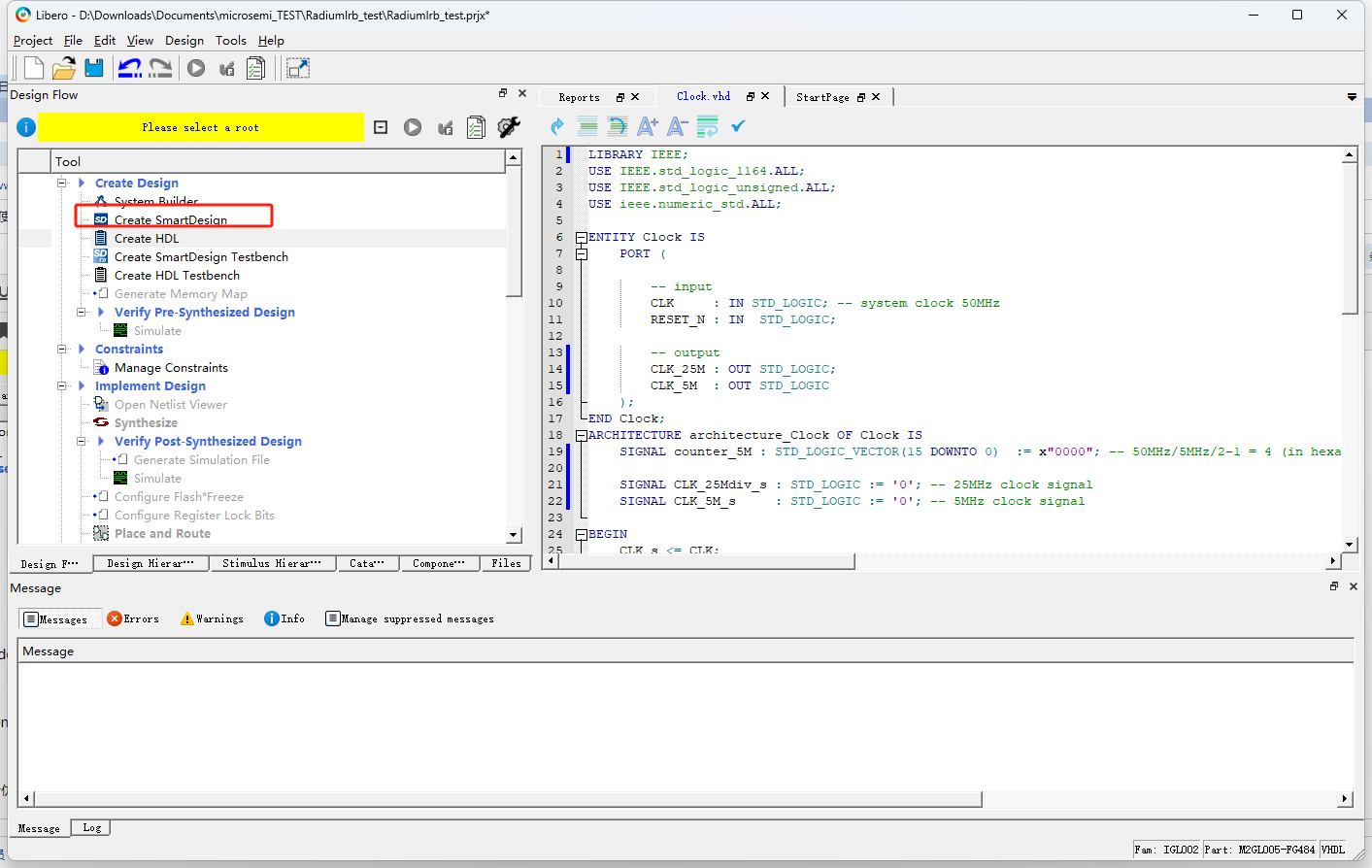

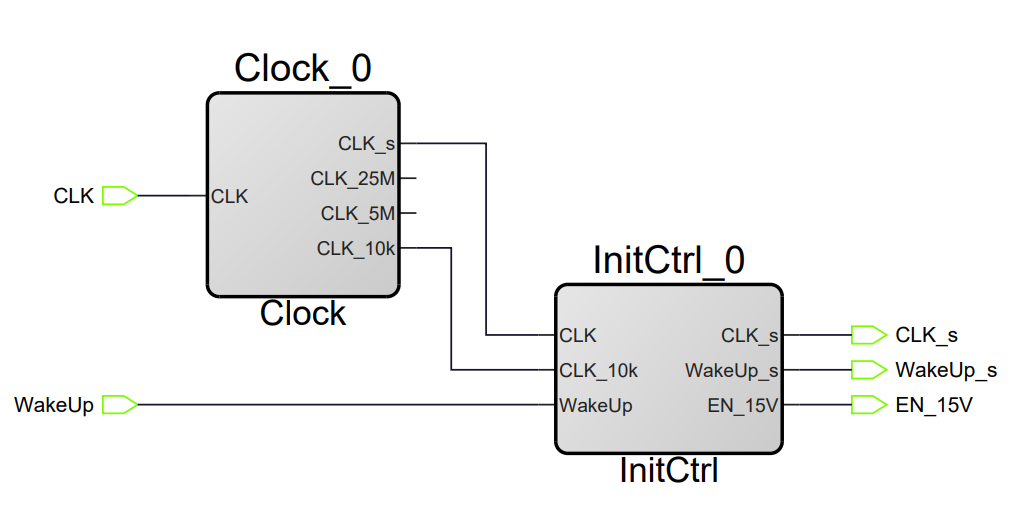

3、创建smartdesign

SmartDesign是Libero SoC的另一个核心功能,它可以让我们通过图形化的方式来设计我们的FPGA项目,我们可以在SmartDesign中添加各种block design,包括我们自己编写的HDL文件,也可以是Libero SoC提供的一些IP核,还可以是一些外部的库文件,然后通过拖动和连线的方式来实现我们的设计。

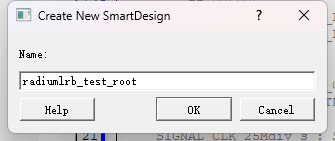

我们回到Design Flow,点击Create SmartDesign,然后给SmartDesign取一个名字,点击OK。

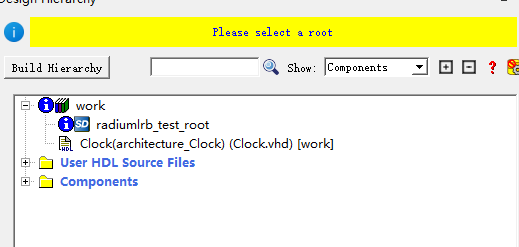

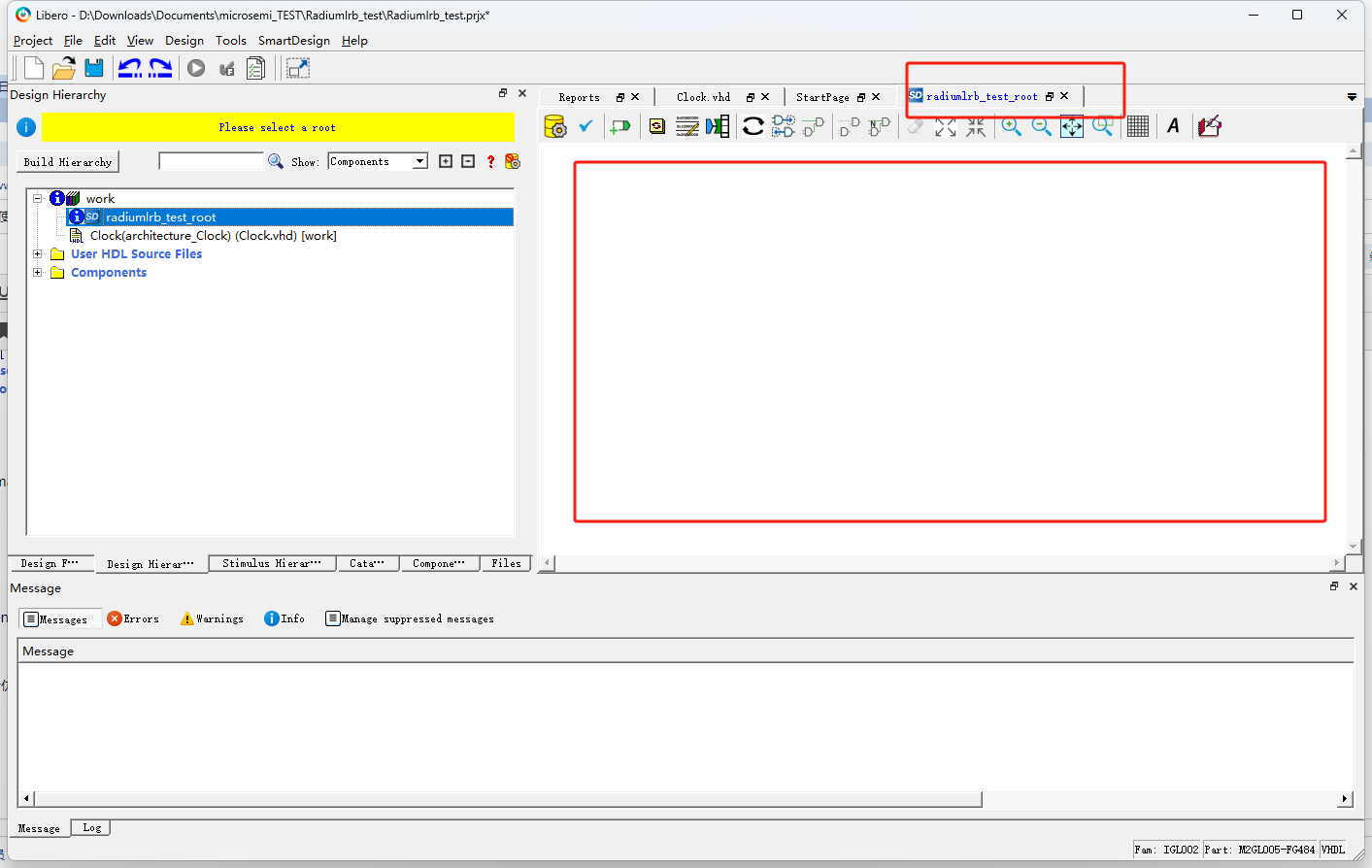

回到Design Hierarchy,并点击Build Hierarchy

双击打开SmartDesign,可以看到右边画布是空白的,因为此时没有添加任何block design,我们需要将我们的HDL文件添加到SmartDesign中,有两种方法:

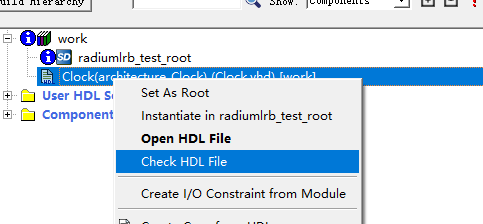

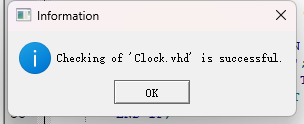

先来检查一下我们的HDL文件有没有语法错误,我们右键我们的HDL文件,点击Check HDL File

这一步是为了检查语法错误

方法一:在打开SmartDesign的情况下,我们可以直接拖动我们的HDL文件到SmartDesign中

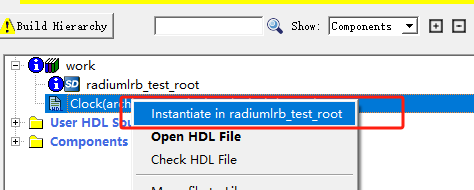

方法二:我们可以右键我们的HDL文件,点击Instantiate,然后选择我们要添加到的SmartDesign文件

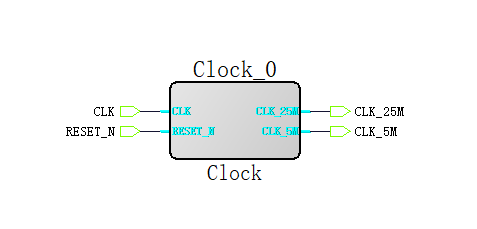

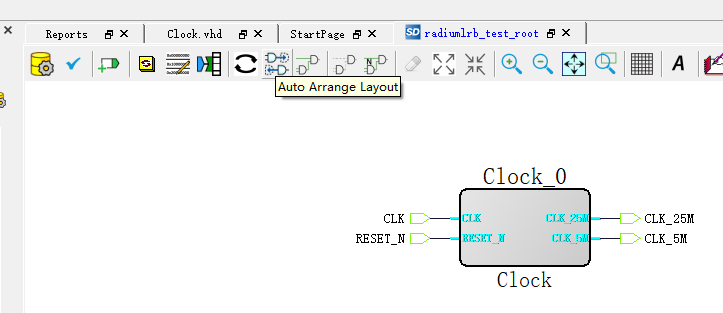

可以看到clock模块已经出现在画布中

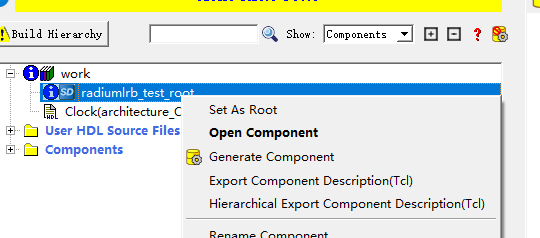

我们还需要将我们的SmartDesign设置为顶层文件,这样才能让Libero SoC知道我们的设计的入口在哪里,我们右击我们的SmartDesign,点击Set as Root,然后我们可以看到我们的SmartDesign的名字变成了粗体,表示它已经是顶层文件了。

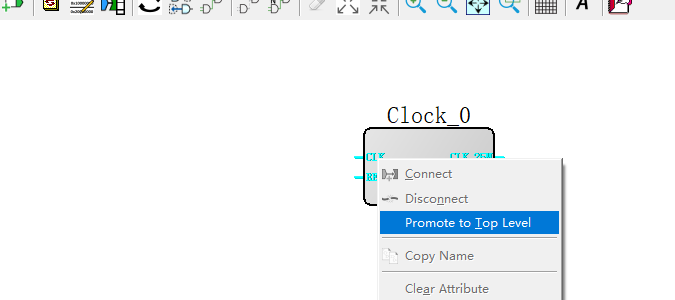

我们还需要将我们的HDL文件的端口与外部的信号连接起来,比如我们的输入时钟信号和输出时钟信号,我们需要将它们放置到顶层,作为我们的IO引脚,这样才能与外部的晶振和IO口映射起来,我们选择想要放置到顶层的端口,右键,点击Promote to Top Level

放置到顶层以后,这些顶层io可以添加约束并与外部晶振和io映射

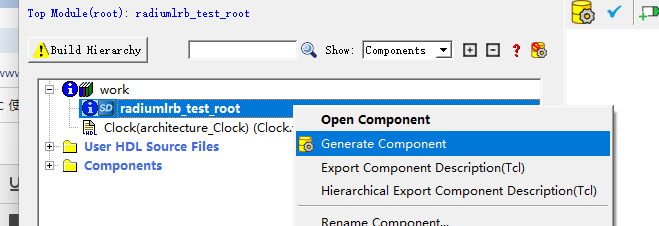

完成画布链接后,我们点击Generate Component,这样就可以让Libero SoC生成一个组件文件,用来保存我们的SmartDesign的信息,然后我们点击Build Hierarchy,这样就可以让Libero SoC更新我们的工程结构,这样我们就完成了SmartDesign的创建和配置。

方法一

方法二

如果我们的模块过多,连线很乱,我们可以使用自动布局的功能,让Libero SoC帮助我们优化我们的画布,我们点击Layout,然后选择Auto Layout,然后Libero SoC就会自动调整我们的模块的位置和大小

如果我们有多个HDL文件,我们还可以将它们之间的端口连接起来,形成一个完整的设计,我们可以通过鼠标拖动的方式来链接各个模块的IO来实现连接。

4、功能仿真(RTL行为仿真)、综合后门级功能仿真(前仿真)与时序仿真(后仿真)

4.1、仿真前的准备

烧录之前,我们需要对代码进行仿真。Libero SoC自带了三种仿真方式,它们都调用ModelSim 2022。在安装Libero SoC时,ModelSim会自动安装,并且证书与Libero SoC的证书对齐,因此无需额外激活操作

4.2、创建仿真

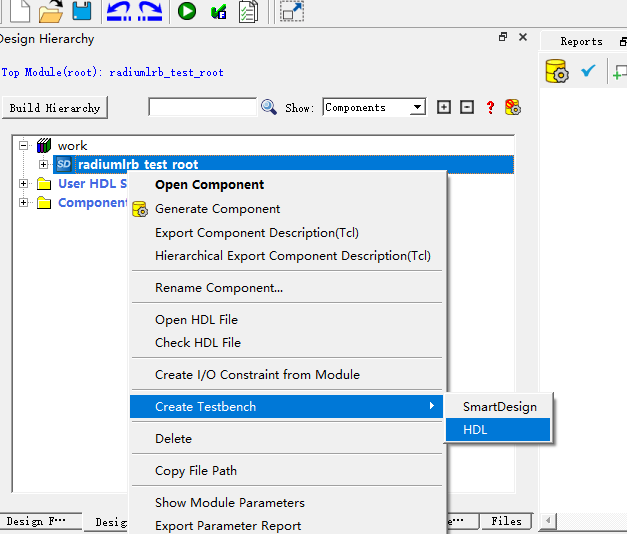

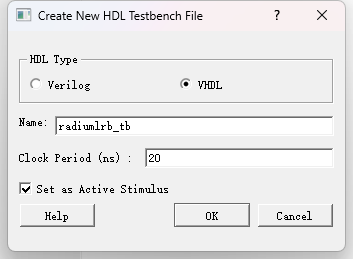

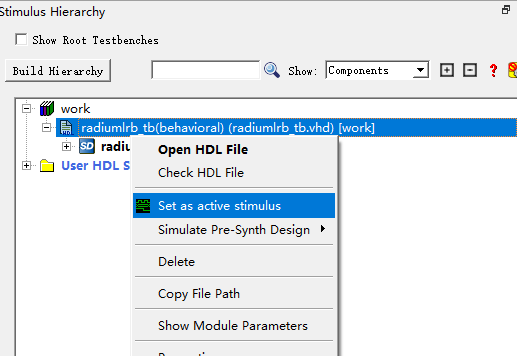

选择要仿真的SmartDesign,右键创建仿真。

为仿真命名并设置仿真周期。

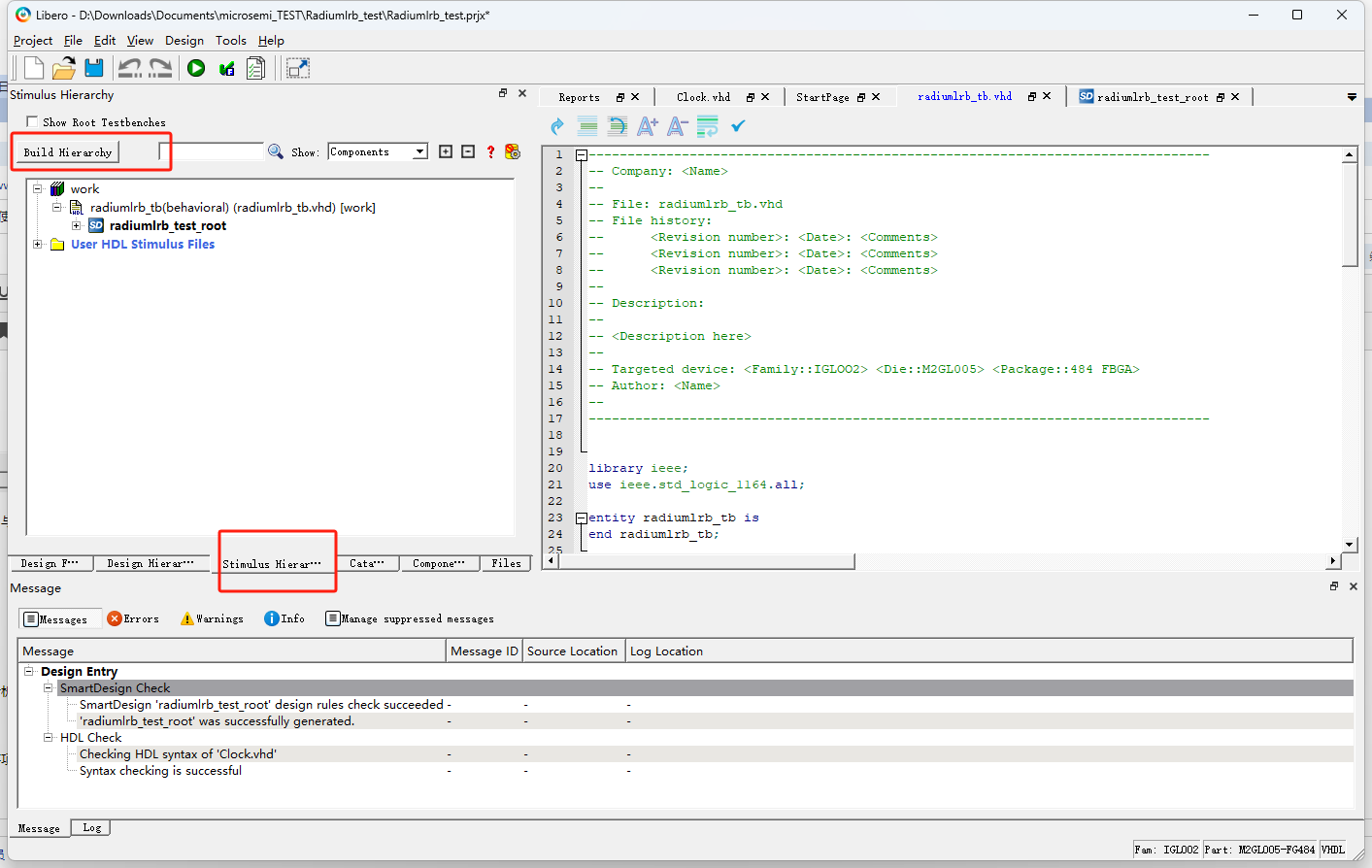

在Stimulate Hierarchy中,点击Build Hierarchy即可看到刚刚创建的仿真文件。

右键激活仿真

4.3、编辑仿真内容

双击打开仿真文件,可以查看代码内容。这是自动生成的仿真文件,包含基本的初始化和时钟连线。软件会自动识别reset信号和clk信号并连线。

--------------------------------------------------------------------------------

-- Company: <Name>

--

-- File: radiumlrb_tb.vhd

-- File history:

-- <Revision number>: <Date>: <Comments>

-- <Revision number>: <Date>: <Comments>

-- <Revision number>: <Date>: <Comments>

--

-- Description:

--

-- <Description here>

--

-- Targeted device: <Family::IGLOO2> <Die::M2GL005> <Package::484 FBGA>

-- Author: <Name>

--

--------------------------------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY radiumlrb_tb IS

END radiumlrb_tb;

ARCHITECTURE behavioral OF radiumlrb_tb IS

CONSTANT SYSCLK_PERIOD : TIME := 20 ns; -- 50MHZ

SIGNAL SYSCLK : STD_LOGIC := '0';

SIGNAL NSYSRESET : STD_LOGIC := '0';

COMPONENT radiumlrb_test_root

-- ports

PORT (

-- Inputs

CLK : IN STD_LOGIC;

RESET_N : IN STD_LOGIC;

-- Outputs

CLK_25M : OUT STD_LOGIC;

CLK_5M : OUT STD_LOGIC

-- Inouts

);

END COMPONENT;

BEGIN

PROCESS

VARIABLE vhdl_initial : BOOLEAN := TRUE;

BEGIN

IF (vhdl_initial) THEN

-- Assert Reset

NSYSRESET <= '0';

WAIT FOR (SYSCLK_PERIOD * 10);

NSYSRESET <= '1';

WAIT;

END IF;

END PROCESS;

-- Clock Driver

SYSCLK <= NOT SYSCLK AFTER (SYSCLK_PERIOD / 2.0);

-- Instantiate Unit Under Test: radiumlrb_test_root

radiumlrb_test_root_0 : radiumlrb_test_root

-- port map

PORT MAP(

-- Inputs

CLK => SYSCLK,

RESET_N => NSYSRESET,

-- Outputs

CLK_25M => OPEN,

CLK_5M => OPEN

-- Inouts

);

END behavioral;4.3、开始仿真

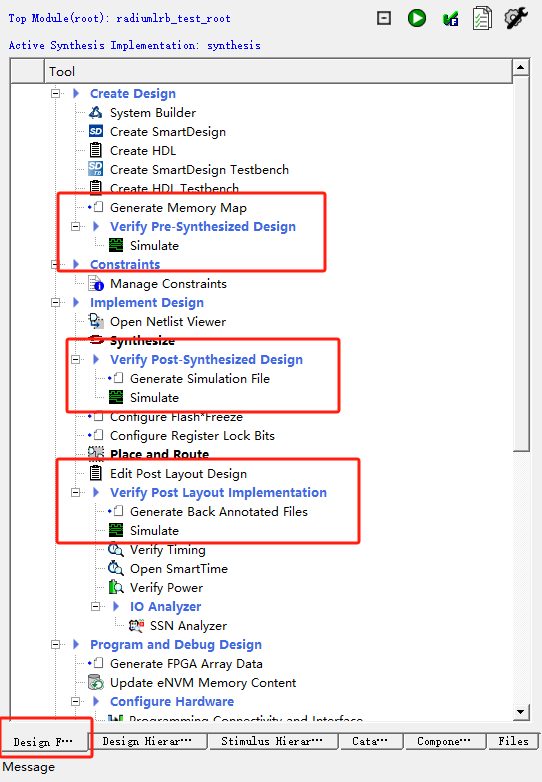

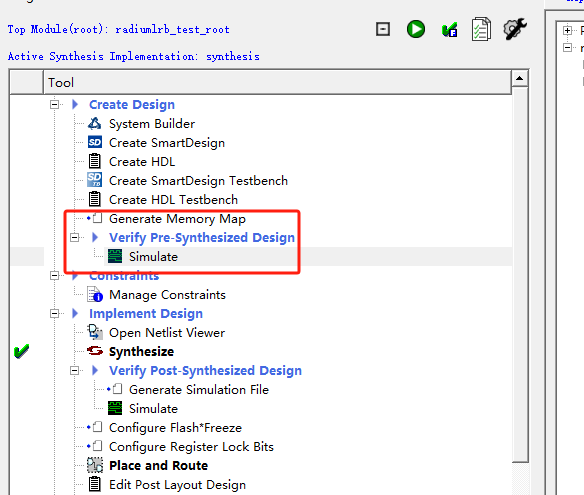

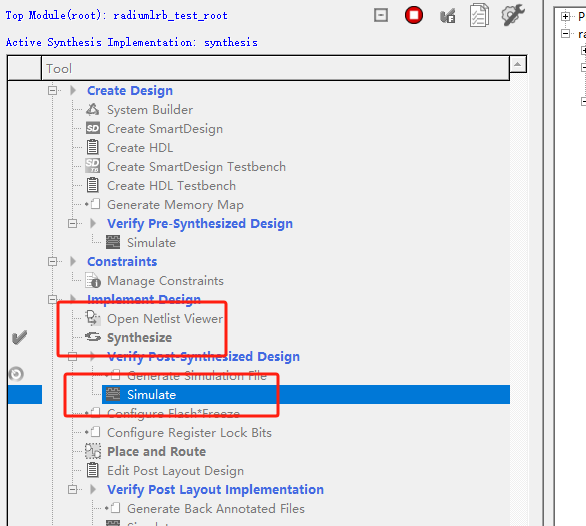

回到Design Flow,可以看到三种仿真路径:前仿真、后仿真以及布线后仿真。

- RTL行为仿真(功能仿真):

- 前仿真用于检测逻辑。

- 在这个阶段,我们验证设计的功能是否按预期工作,检查逻辑错误、时序问题等。

- 这是一个快速的仿真,通常不涉及综合。

- 综合后功能仿真(前仿真):

- 在综合完成后,我们使用后仿真来验证综合后的设计。

- 这个仿真更接近实际硬件,可以检查时序、资源利用率等。

- 时序仿真(后仿真):

- 布线后仿真是在布线完成后进行的仿真。

- 布线后仿真考虑了实际布线的影响,如信号延迟、时钟抖动等。

- 这是最接近实际硬件的仿真,用于验证布线后的设计。

一般来说,后仿真和布线后仿真结果是一致的,所以在重复实验的时候,可以只执行前仿真和后仿真。

点击综合前仿真

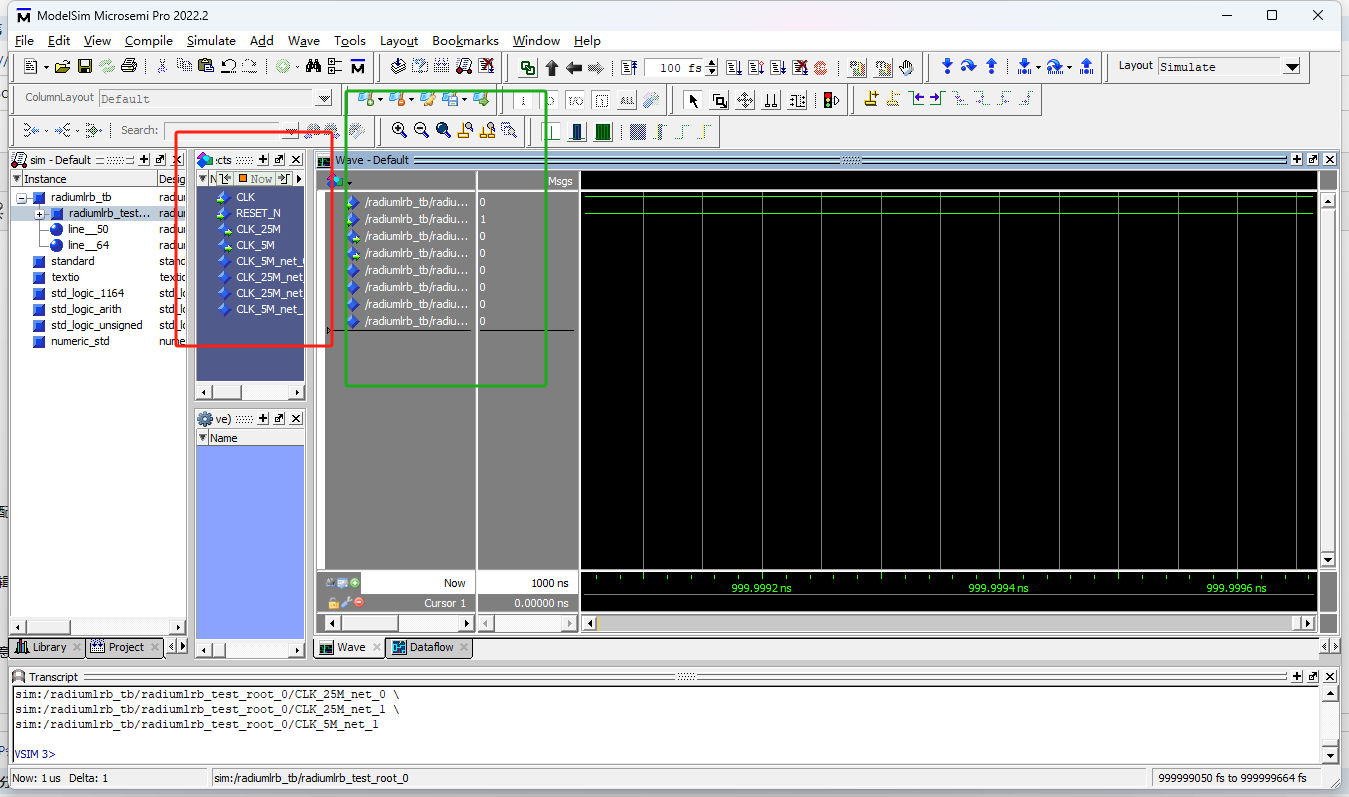

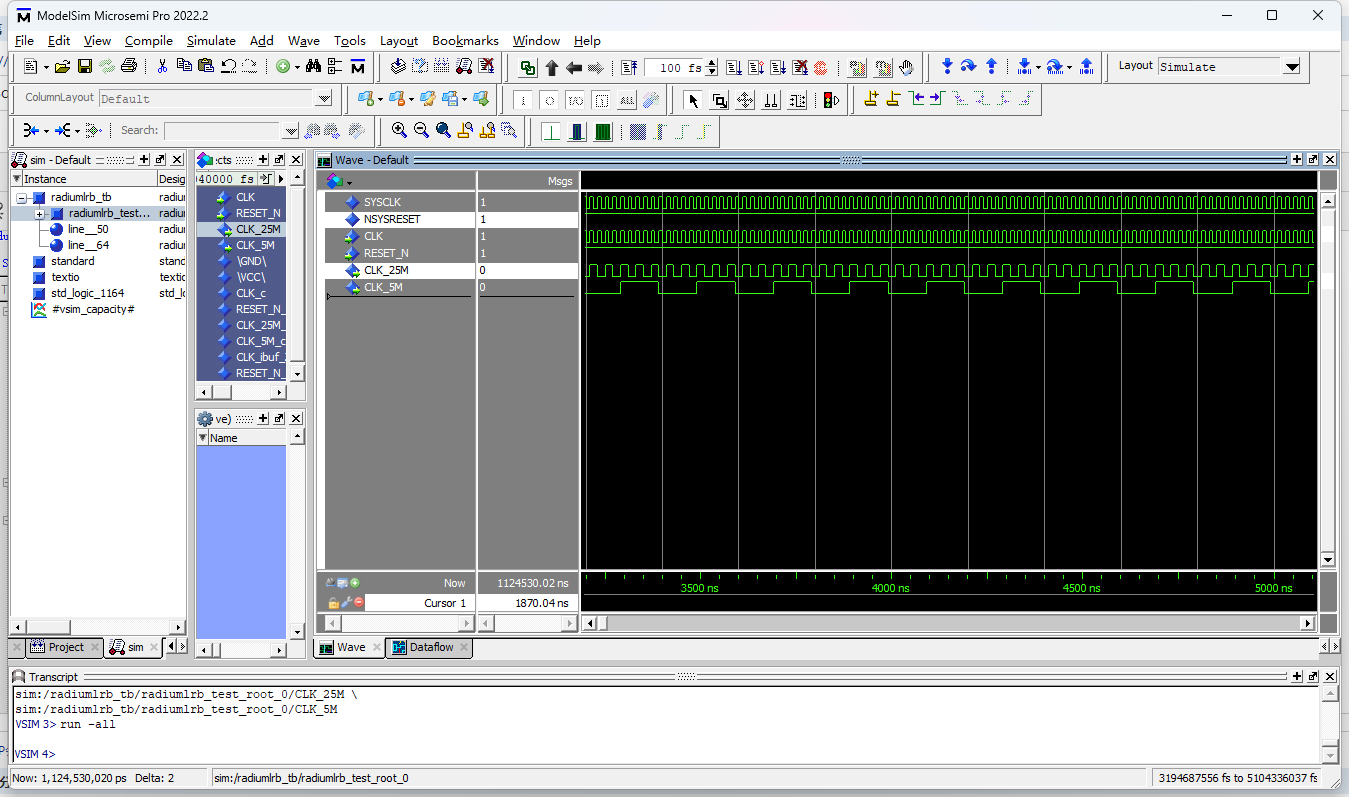

在ModelSim中,选择信号并添加到示波器中,全选(ctrl+a)之后ctrl+w可以添加到右侧的示波器中,在右侧按H(关闭中文输入法)可以不显示变量路径,方便阅读

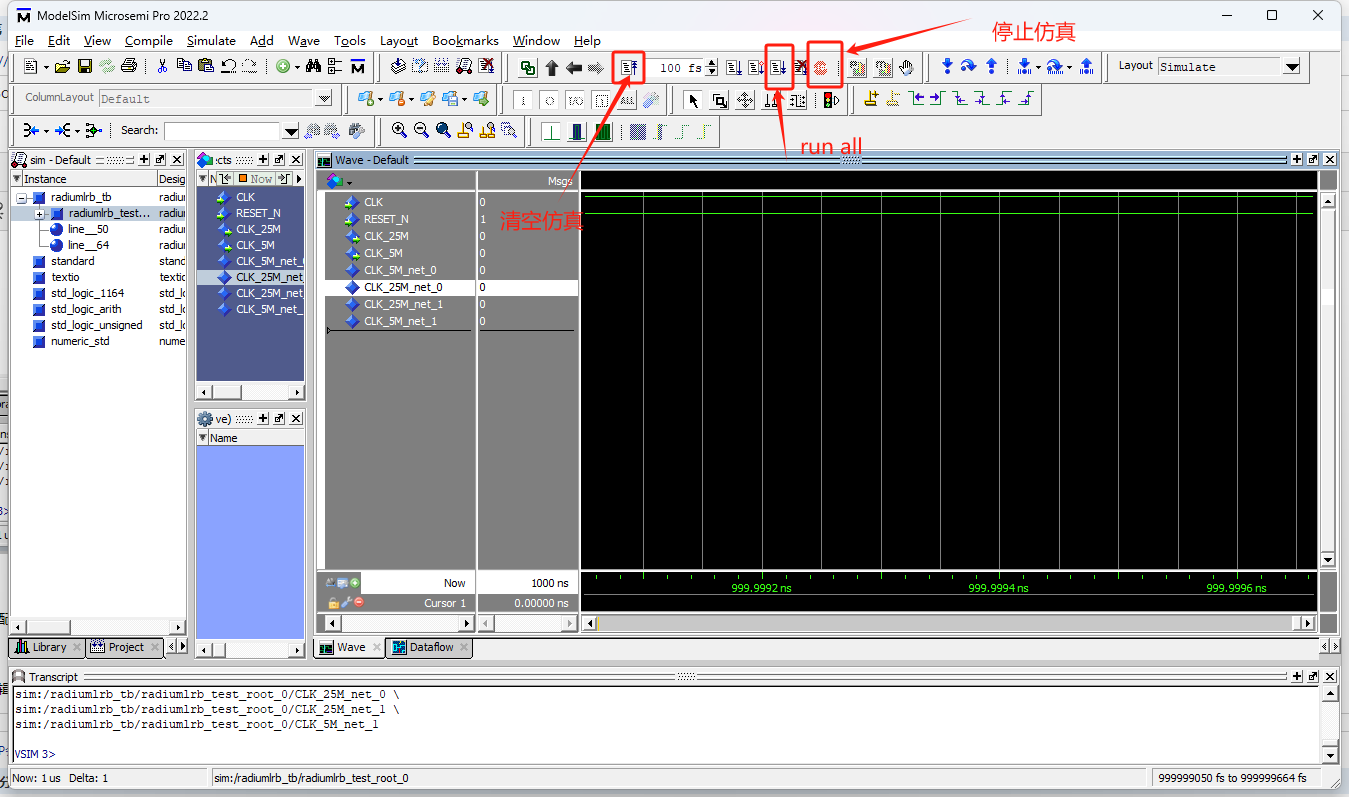

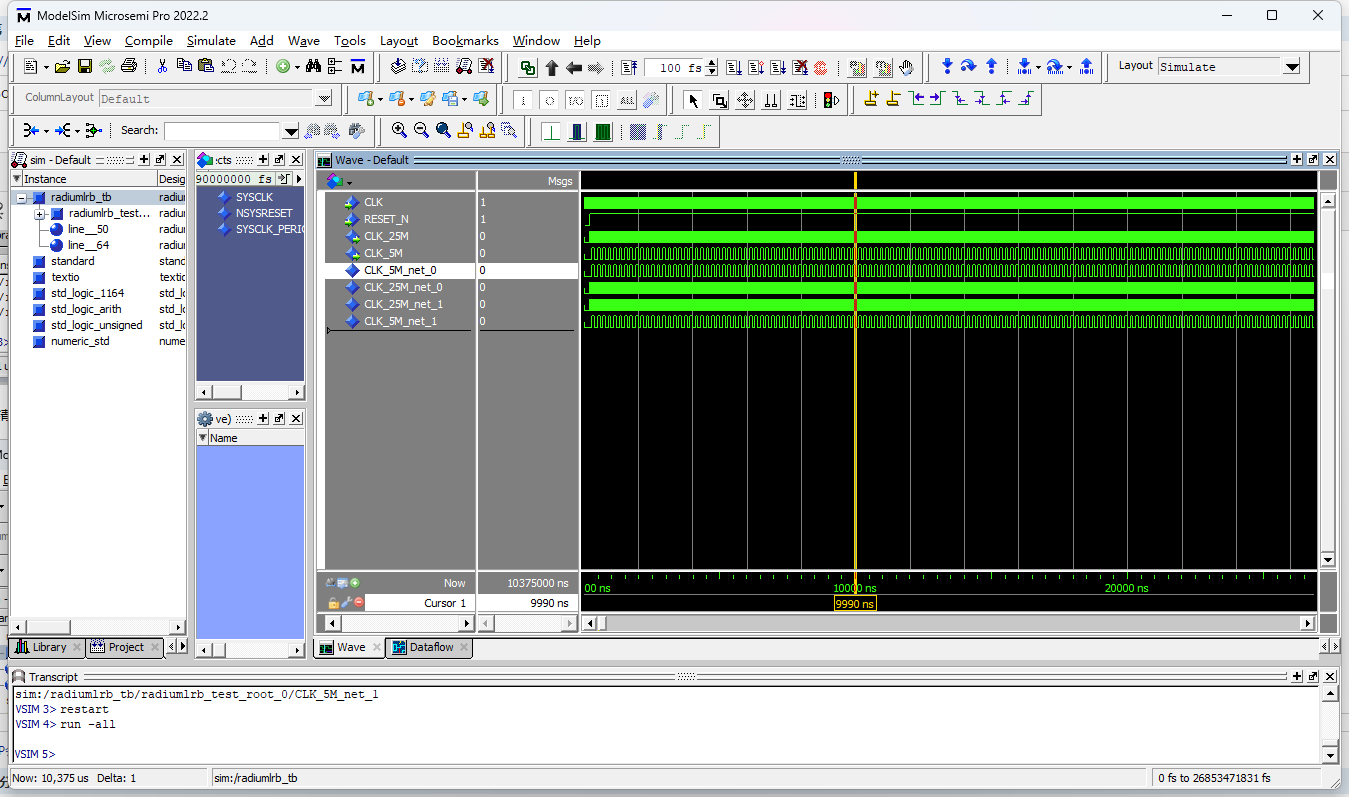

先点击清空仿真,然后点击run -all,等待一两秒点击停止仿真

按f可以缩放波形图

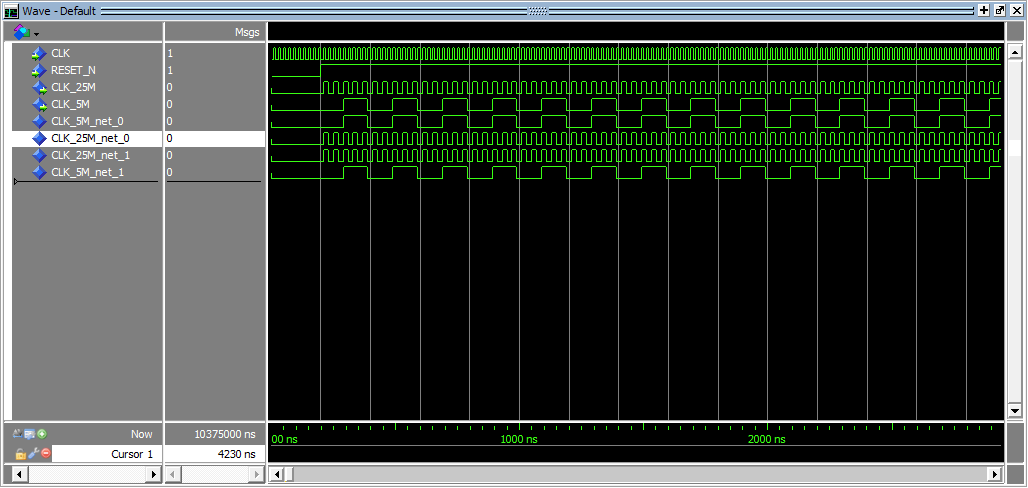

可以看到分频已经完成

先综合然后再点击综合后仿真

仿真正确

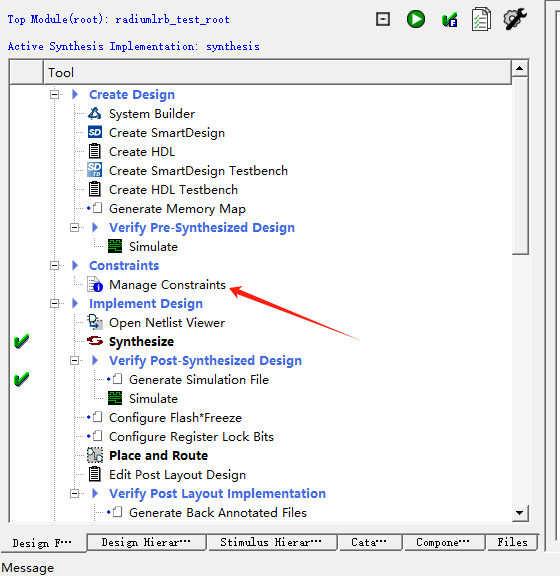

5、引脚分配

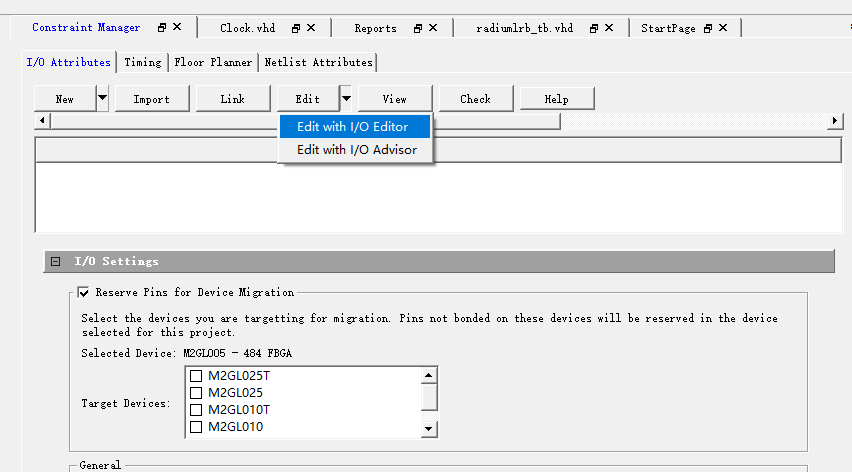

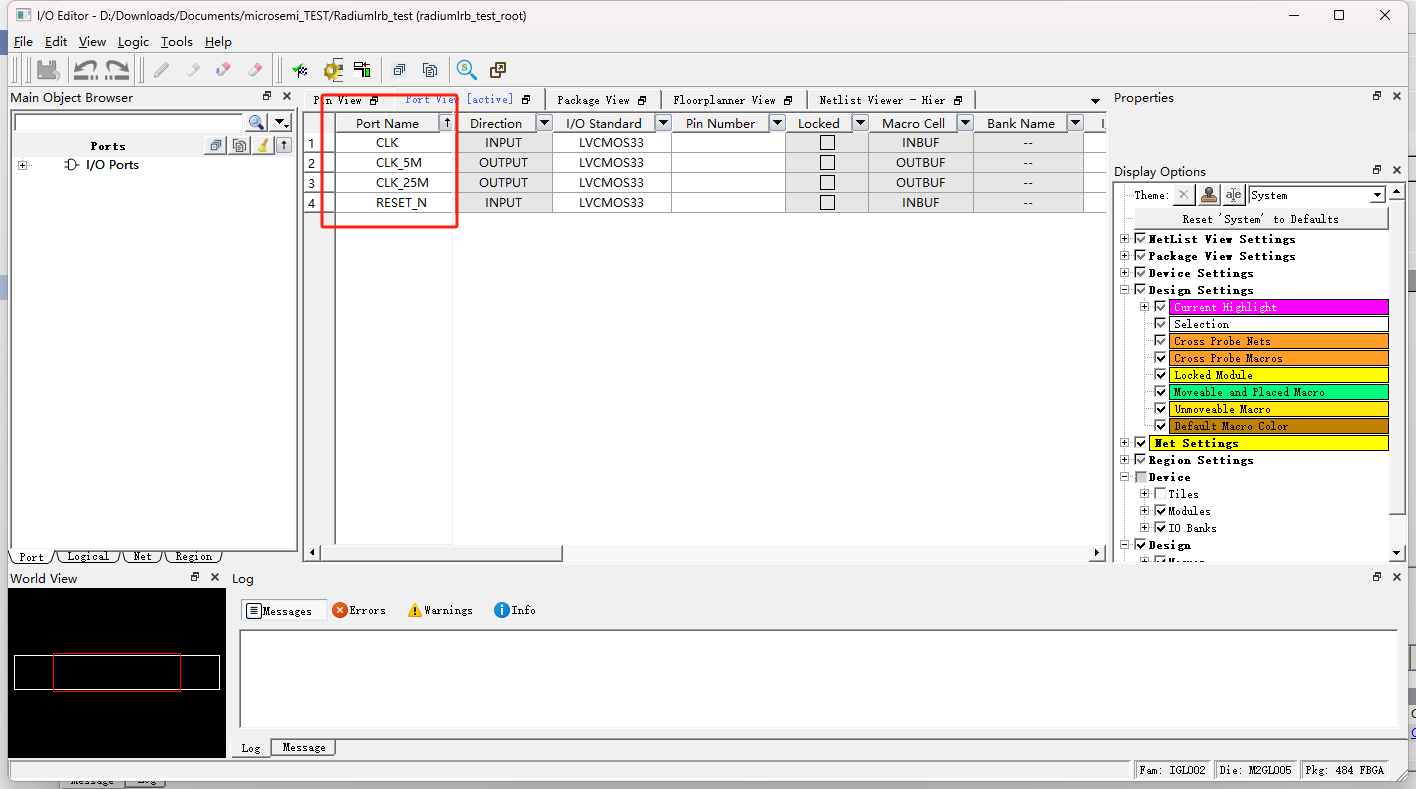

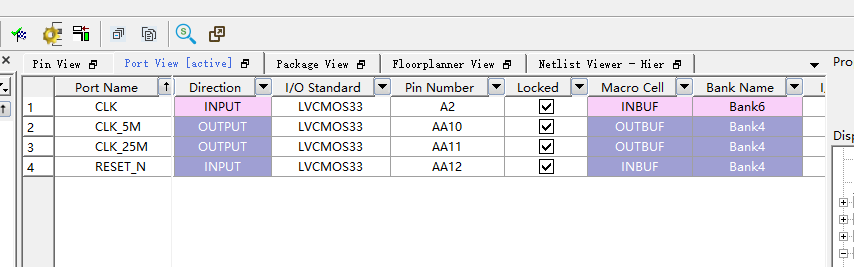

选择Edit with IO Editor来使用图形界面

如果逻辑正确并且信号没有被综合舍弃的话,就会出现在下图,如果信号已经到了顶层但是没有在下图中出现,说明程序并没有有效的利用信号

分配管脚以后关闭窗口

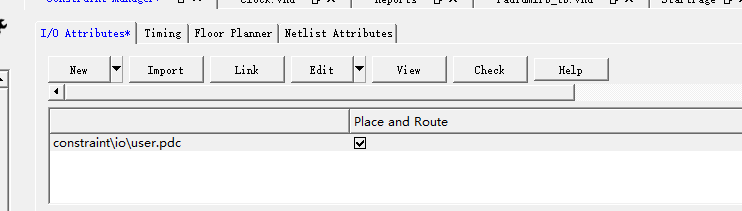

勾选place and route

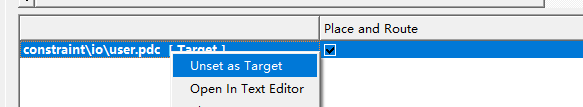

如果不是target的话要设置为target

至此管脚分配完成了

6、使用逻辑分析仪debug

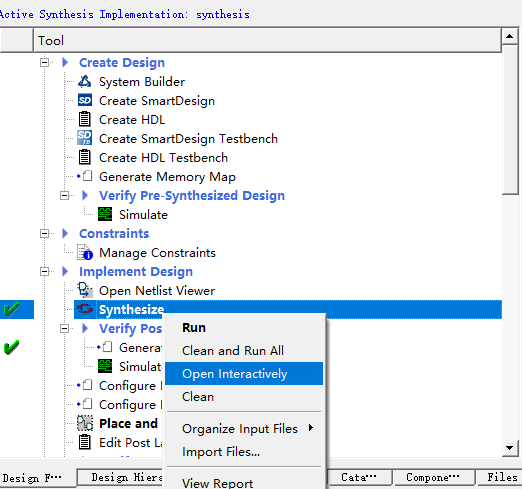

右键synthesize,打开Synplify Pro

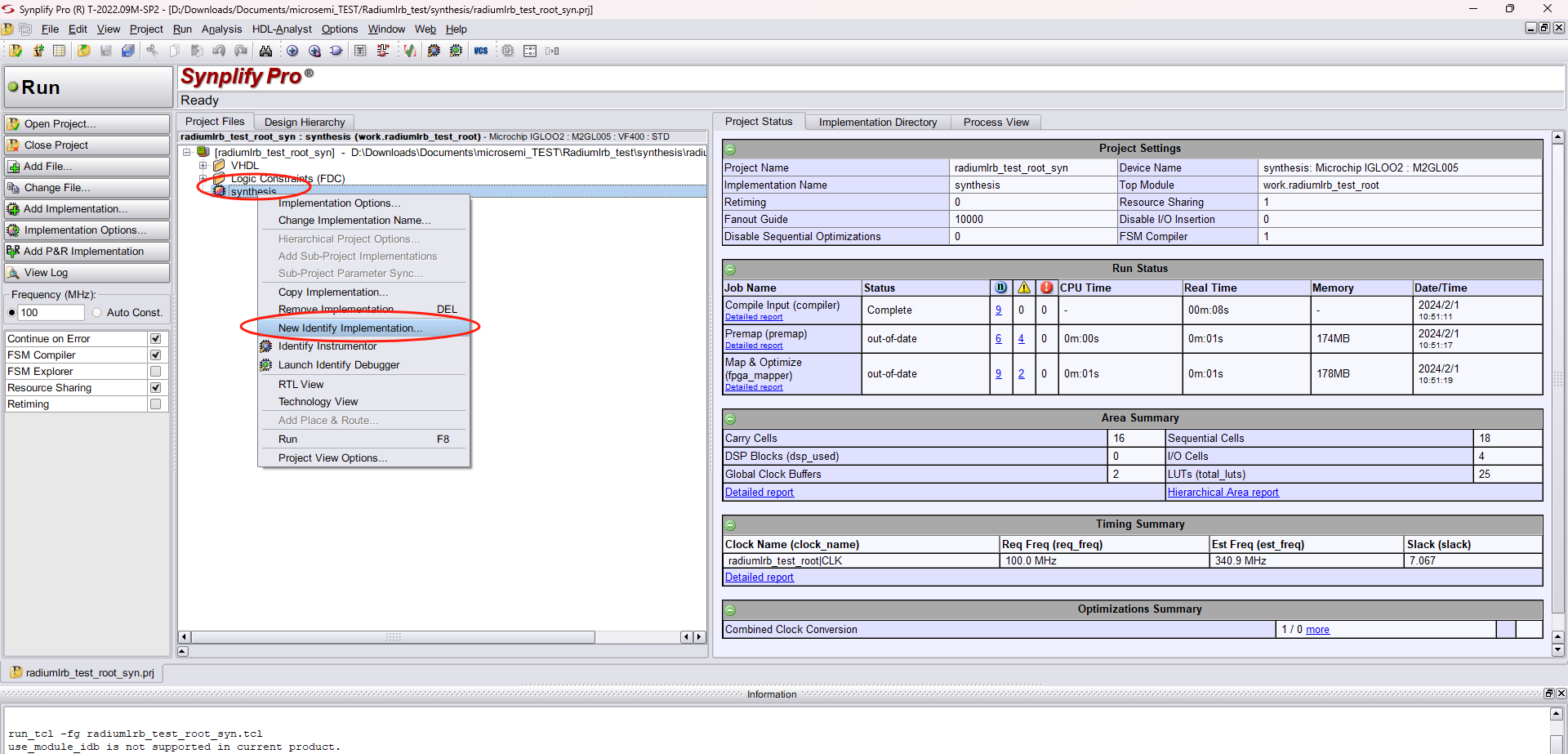

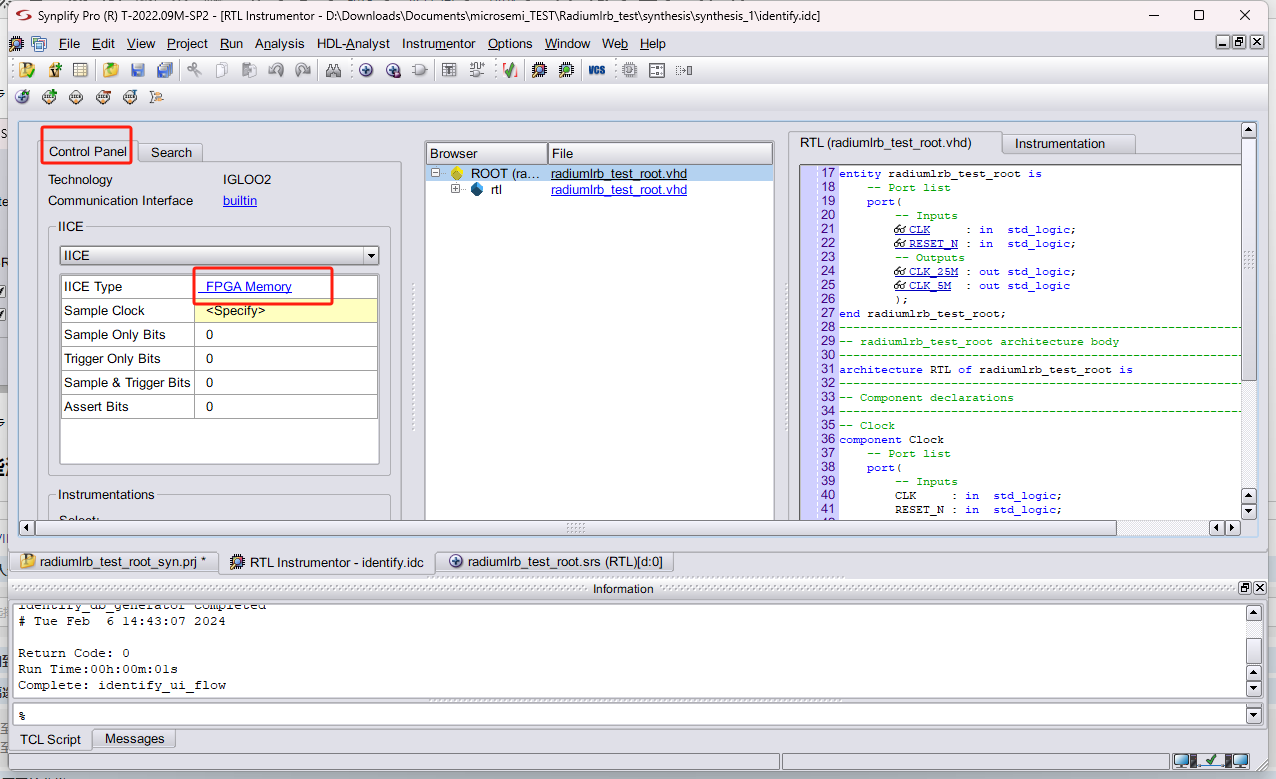

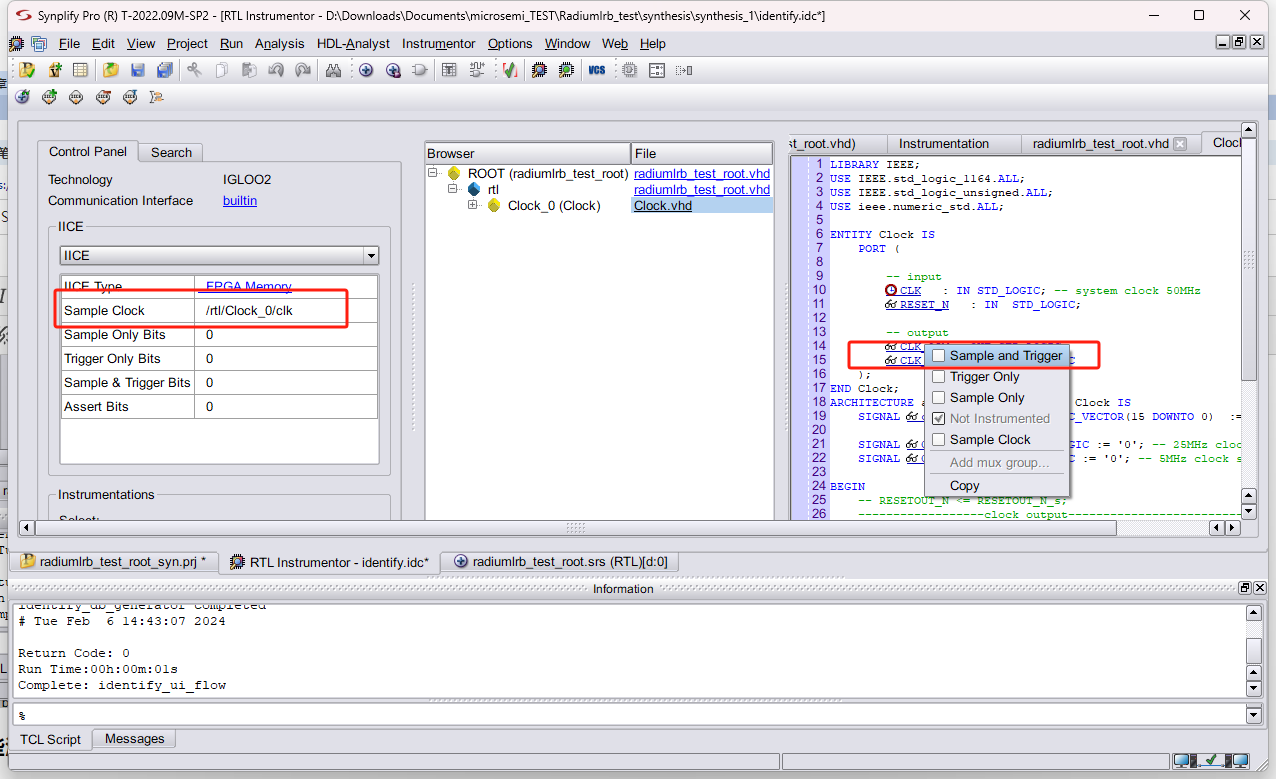

下图是Synplify Pro界面

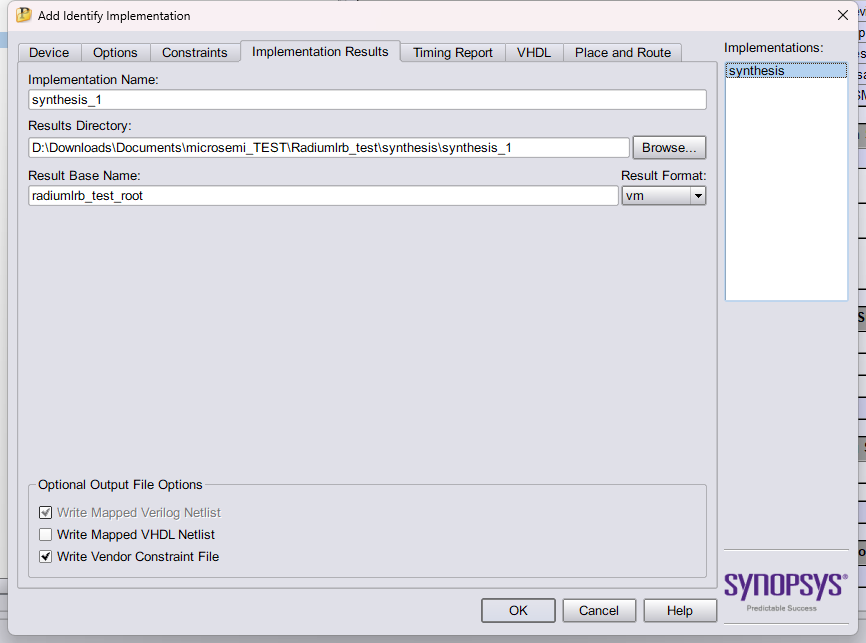

无需修改任何配置,下一步

再打开刚刚创建的综合文件

下一步

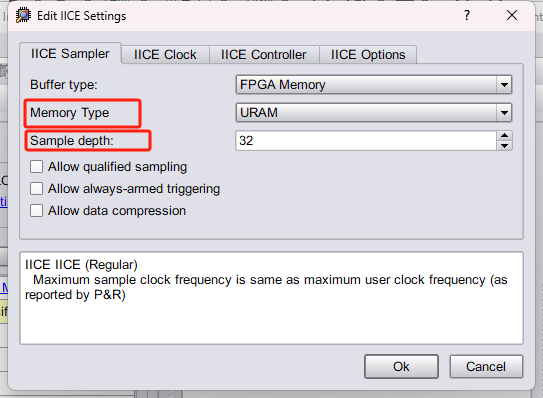

首先配置内存

改这两个即可,这里深度不能设置的太大,否则可能内存不足

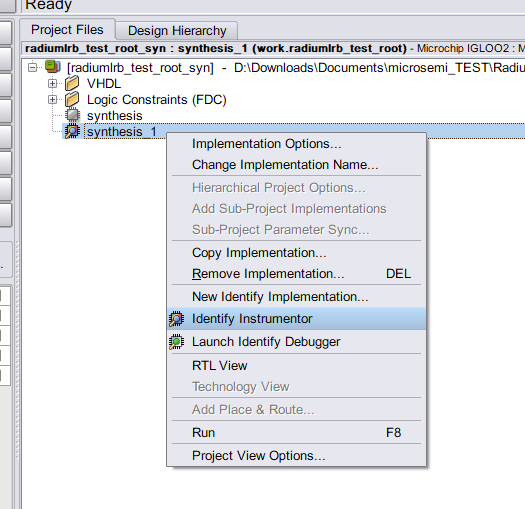

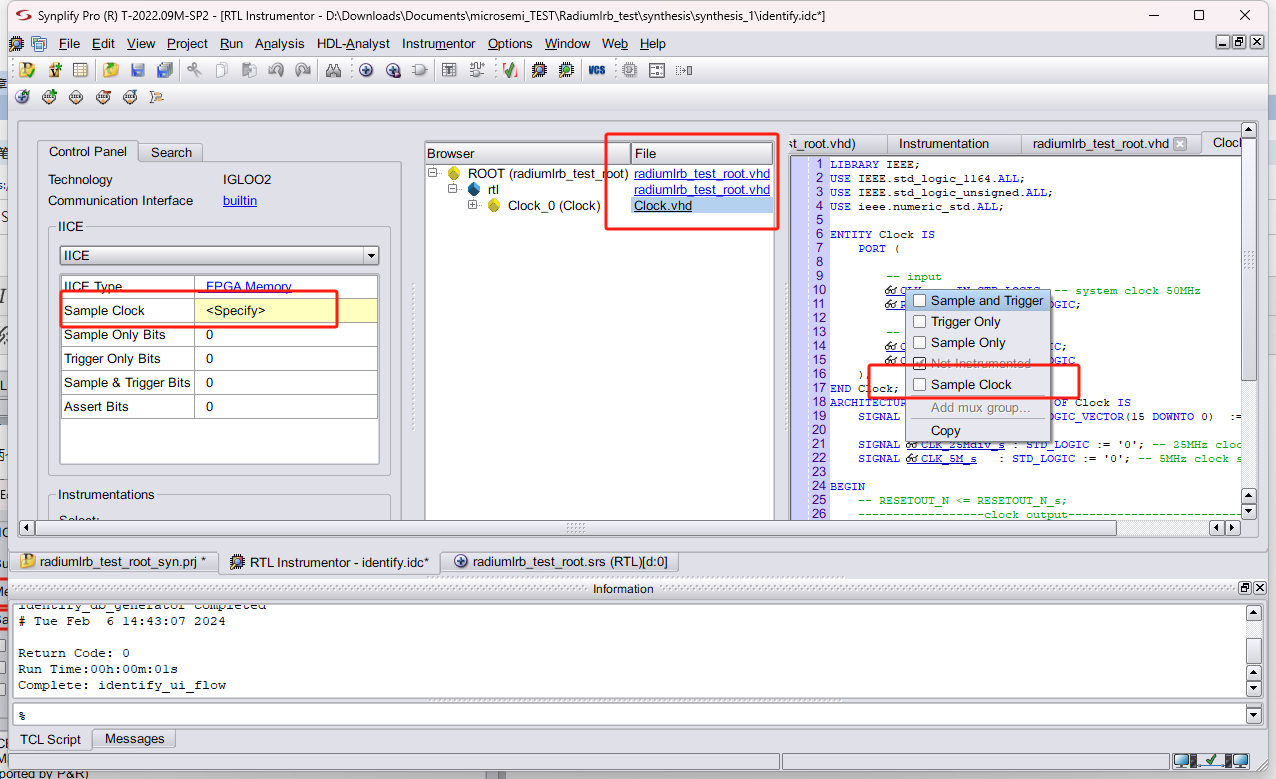

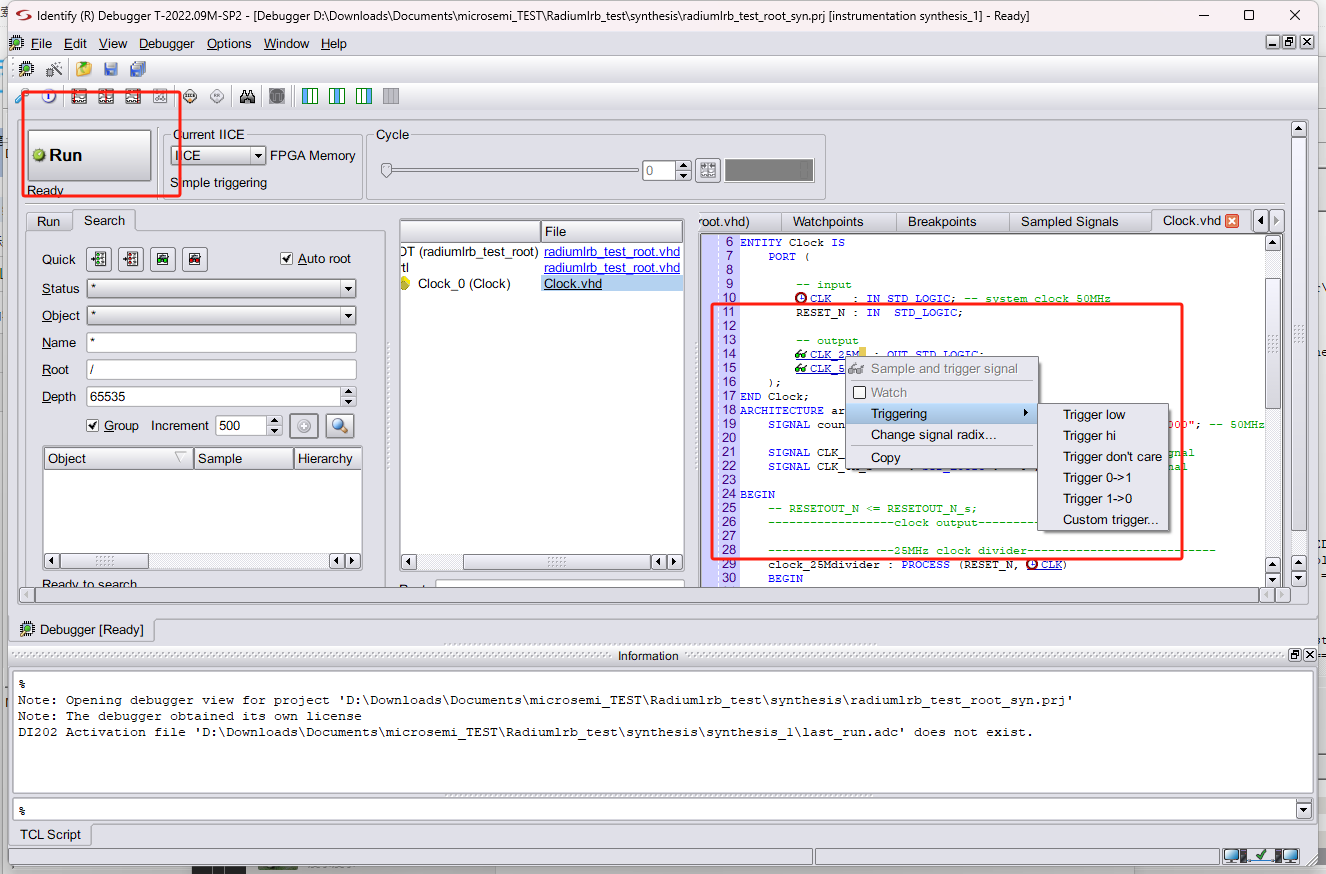

接下来选择观测时钟,首先选择模块,可以点击rtl展开然后选择子文件(点击右侧的.vhd文件即可),右击采样时钟,选择采样,好处是如果信号比较慢,可以用慢速时钟来延长时间以弥补少的可怜的采样深度

选择完时钟后左侧不再有警告,此时可以选择想要观察的对象,可以选择sample only或者sample and trigger

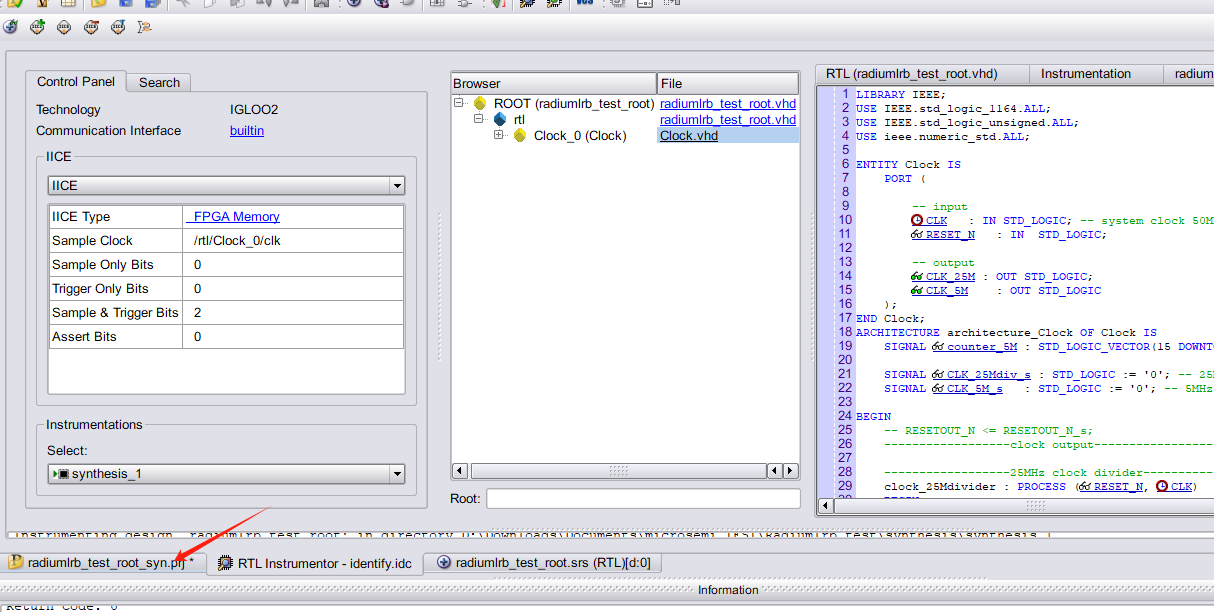

完成后ctrl+s保存,回到综合管理

点击run,一路ok

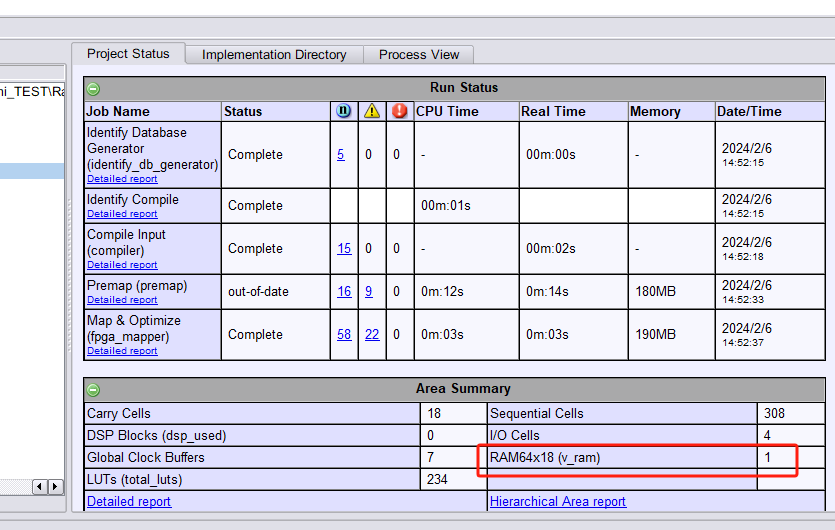

如果采样深度设置过大或者观测变量过多这里v_ram可能超过限制,省着点玩儿,完成以后直接关闭Synplify Pro

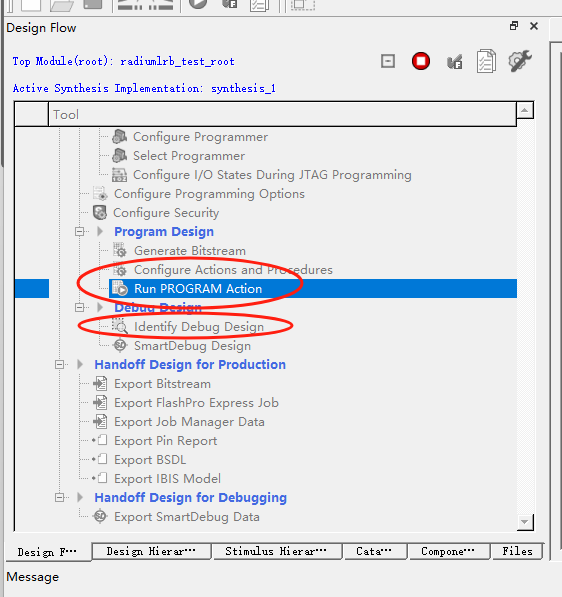

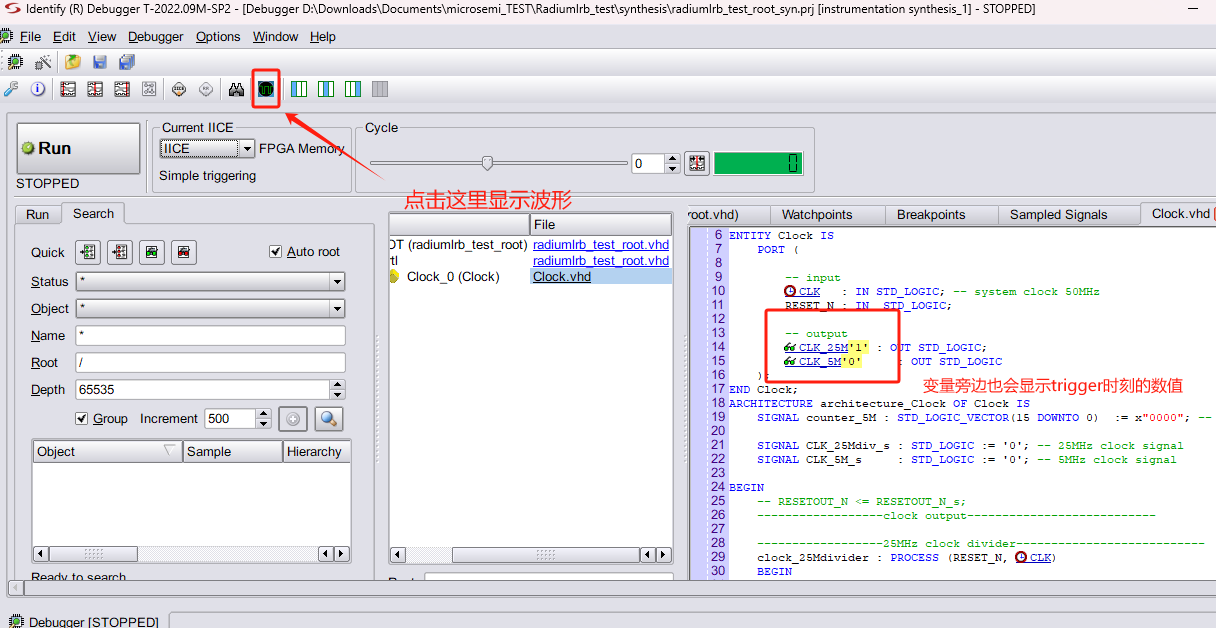

点击Identify Debug Design

添加完敏感信号,直接点击run,或者不添加也可以,会自动trigger

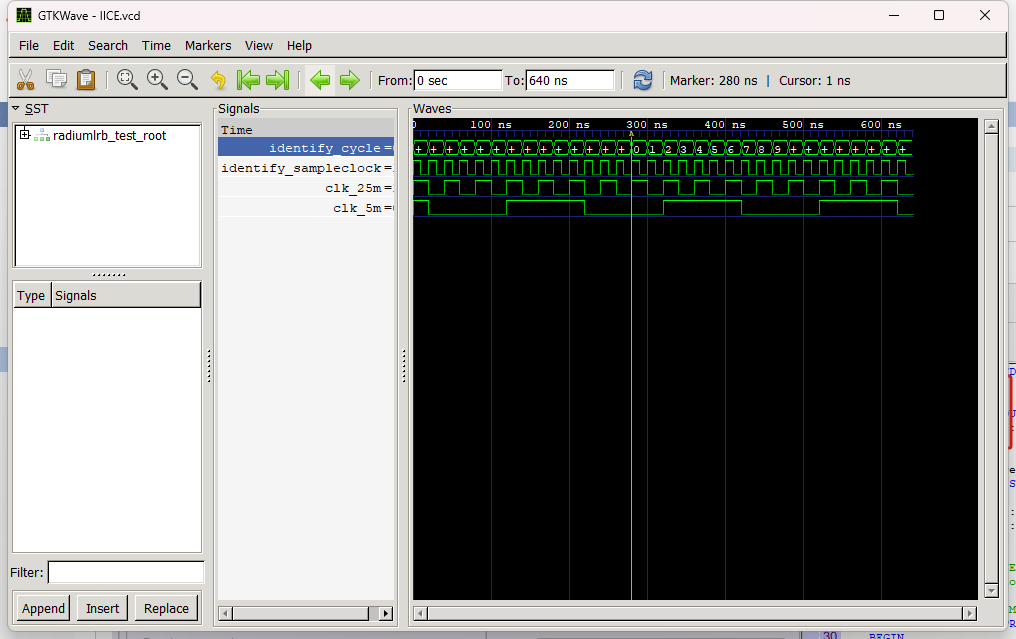

波形正确

至此,ila教学完成

7、一些注意事项

- 有时候在工程创建的过程中,约束文件会突然丢失,导致信号没有在正确的管脚输出,这个时候不要慌,先点开约束文件看看,有时候约束文件会抽风导致引脚分配紊乱

- microsemi的设备逻辑分析仪深度没办法设置的很高,一般最大256,不像xilinx可以设置65535,而且能容纳观测的变量也比较少,不知道是不是使用免费版license导致的

- 某些情况下添加逻辑分析仪后会多几个约束io口,接下来仿真再也不能用了,如果要强行仿真可以把ila删除再仿真,需要debug的时候再添加(如果有更好的解决方法后面会补充)

- 在异步reset_n中一定要把所有变量初始化,在定义变量时候赋初值似乎是无效的,如果后仿真信号出现无定义,大概率就是在resetn中没有初始化导致的。如果烧录以后每次上电程序都运行一段时间后停止,也有可能是因为某些变量没有初始化导致的。所以在添加新的变量的时候,一定要记得在reset_n中初始化

- 工程路径中一定不要有特殊符号、空格、中文,笔者的路径有一个空格,工程、烧录都是正常的,但逻辑分析仪一直报错而且没有错误信息,后面思考是不是路径有问题

浙公网安备 33010602011771号

浙公网安备 33010602011771号