从零开始的SystemVerilog之modelsim的仿真教程 Label: Research

1.keep_hierarchy约束在三模冗余中的应用2.Libero SoC 如何导入模块Module3.FPGA直方图均衡化4.Microsemi Libero SoC使用教程(胎教级 免费)(创建工程、引脚分配、仿真、逻辑分析仪ILA)5.从零开始的zynq之petalinux胎教级安装教程

6.从零开始的SystemVerilog之modelsim的仿真教程 Label: Research

7.FPGA原语及IDDR仿真8.常用时序收敛方法9.FPGA时序约束步骤(vivado)10.信号加扰与FPGA实现11.AXI总线掩码(WSTRB)操作12.FPGA DFT/FFT13.DDR浅析首先激活modelsim然后打开modelsim

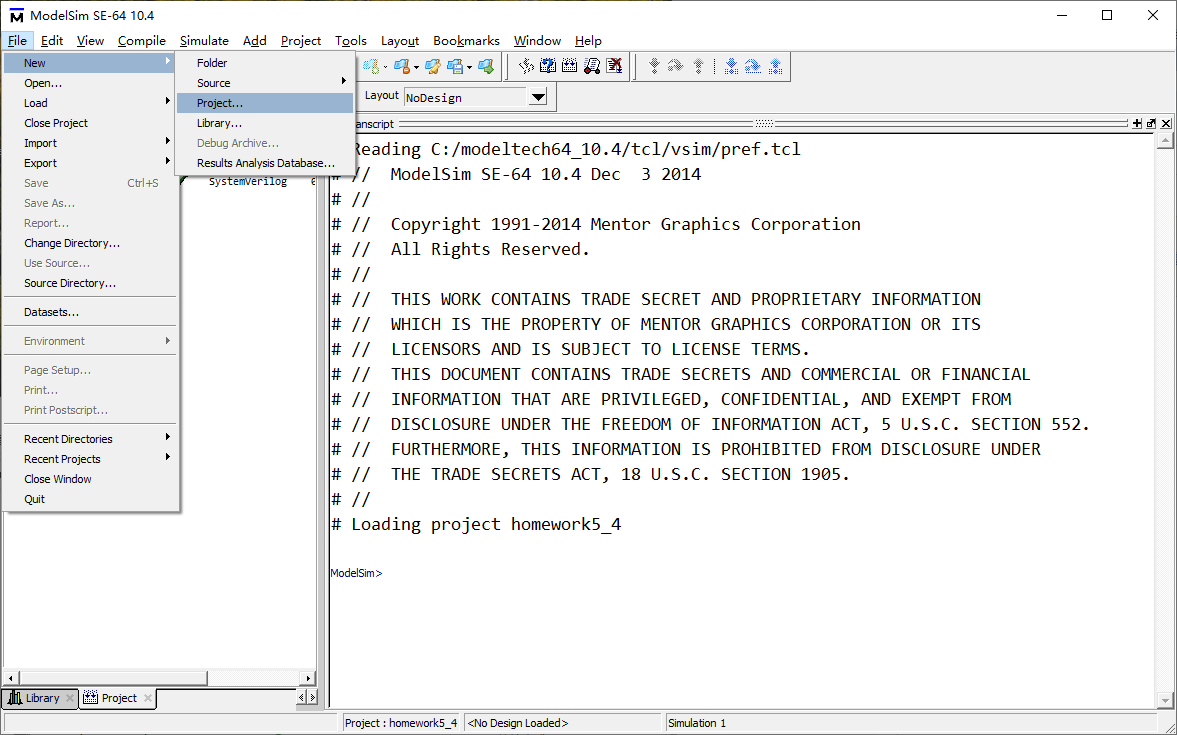

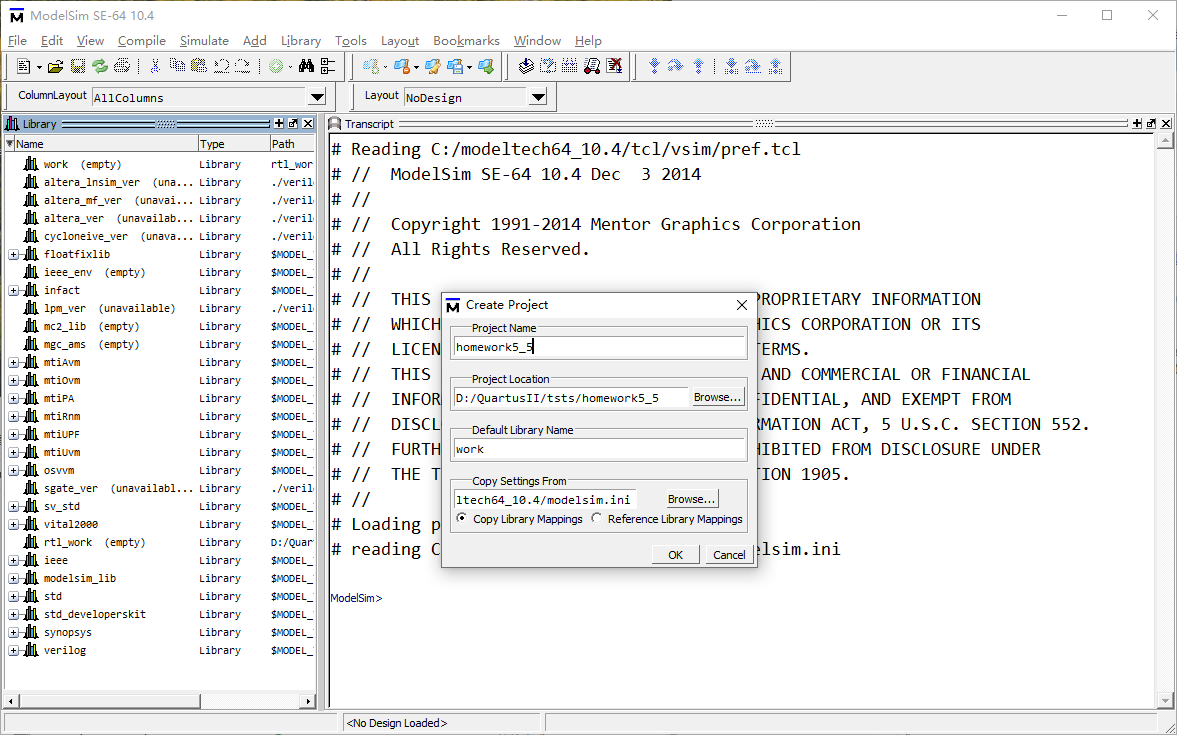

新建project

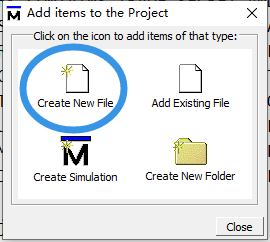

选择要使用的语言,这里使用systemverilog

对于初学者,可以只使用一个文件编写主要模块和testbench(tb文件),所以这里直接关闭窗口

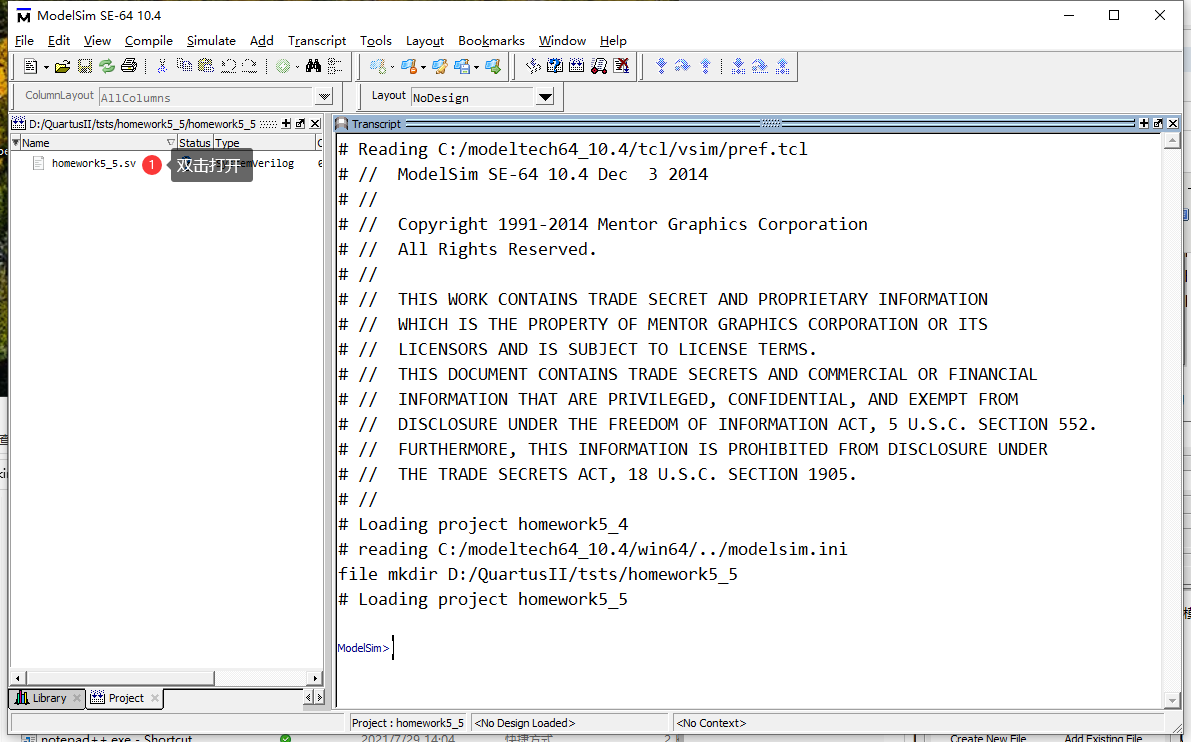

双击打开

填入测试代码

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 | package definitions; parameter version = "1.1"; typedef enum {ADD, SUB, MUL} opcodes_t; typedef struct { logic [31:0] a, b; opcodes_t opcode; //opcode ADD, SUB MUL } instruction_t; typedef union { logic [31 : 0] u_data; logic signed [31 : 0] s_data; } data_t; endpackage //import definitions::*;module homework5_5(// import definitions:: instruction_t IW, input logic read, output logic [31:0] result); import definitions:: *; enum logic {ON=1'b0, OFF=1'b1, HZ=1'bz, UN=1'bx} fo_st; endmodule`timescale 1 ns/ 1 nsmodule homework5_5_tb();logic read;//tb这里不要写input和outputlogic [31:0] result;// assign statements (if any) homework5_5 i1 (//注意这里的引用要和主模块名称一致// port map - connection between master ports and signals/registers .read(read), .result(result));initial begin read=0; result=0; $display("variable"); end always begin #10; result++; read+=2; if ($time >= 1000) begin $finish ; endend endmodule |

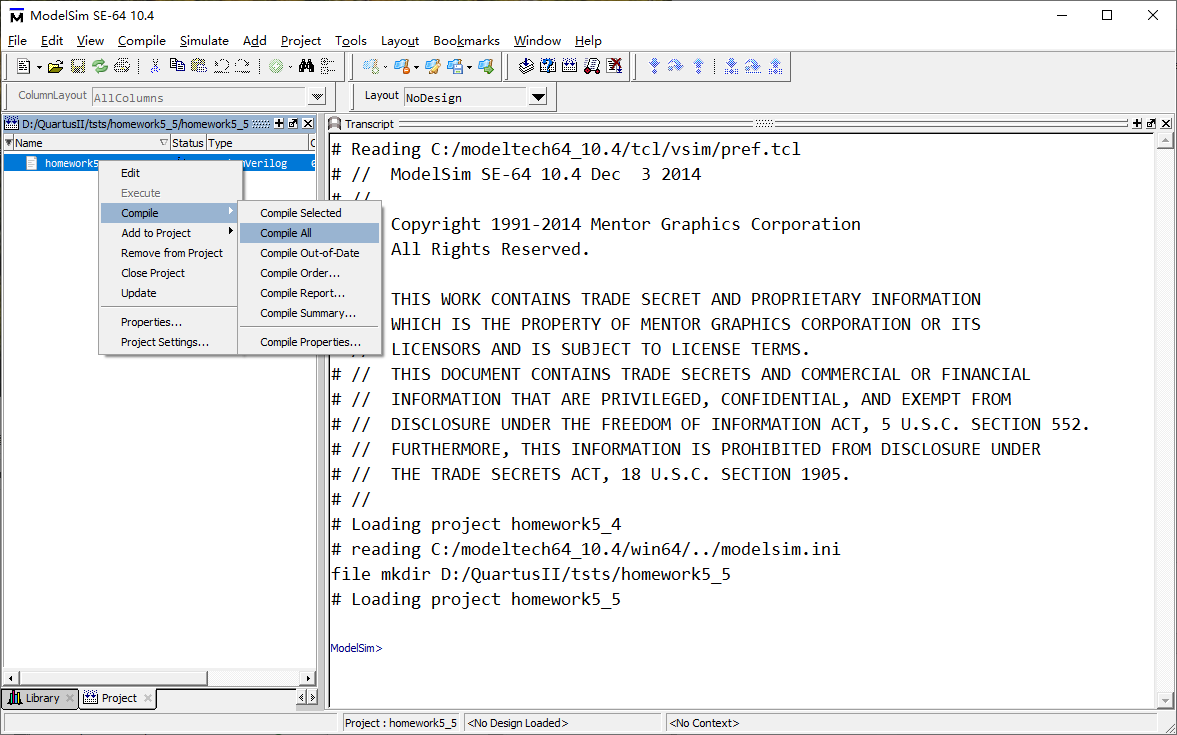

保存,右击,编译所有

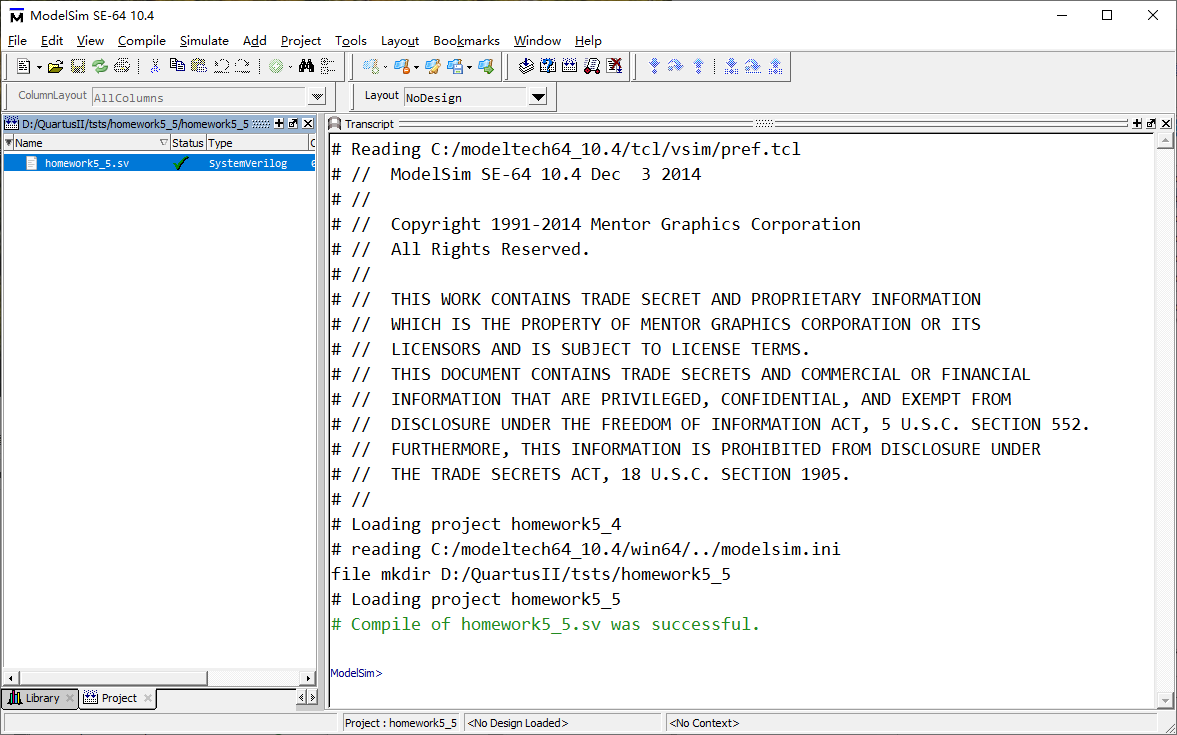

提示编译成功

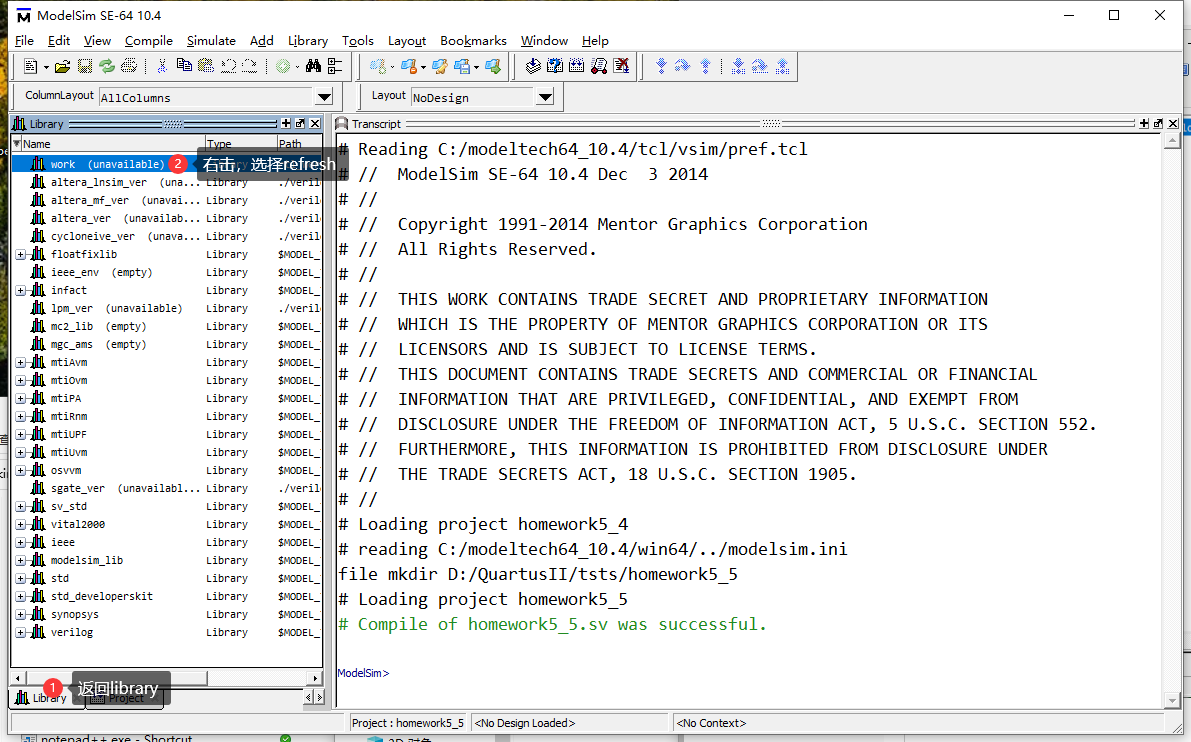

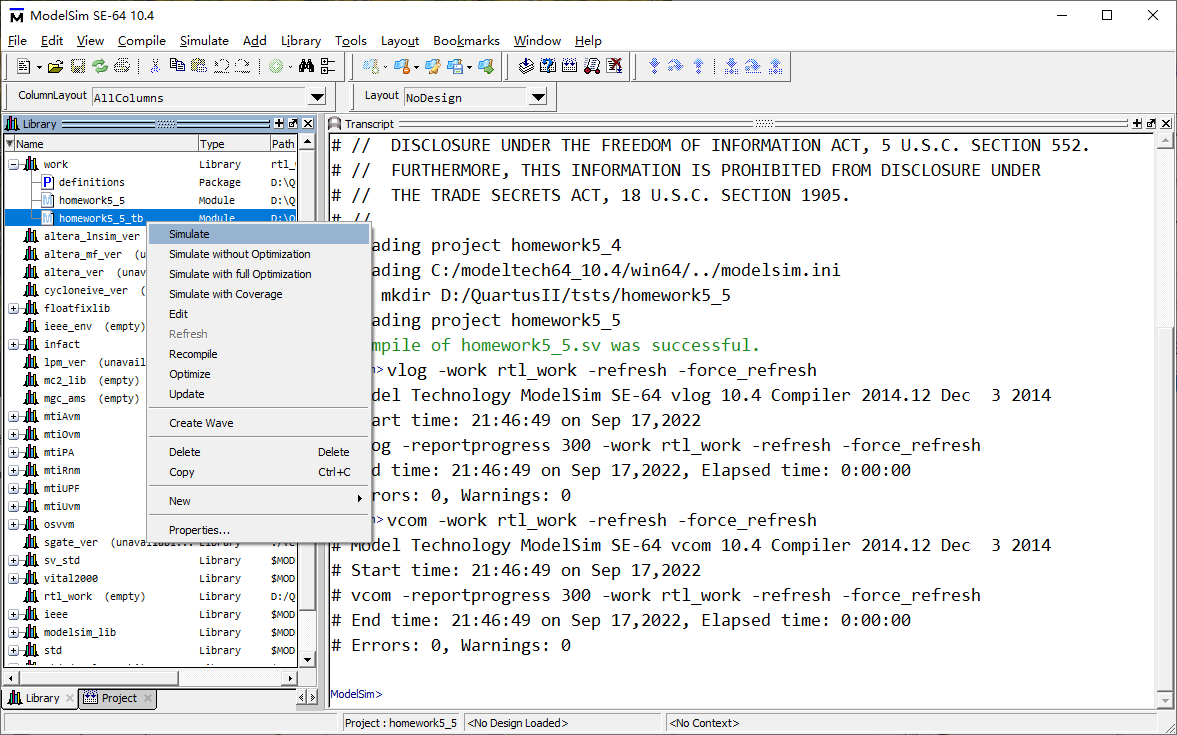

返回library,刷新工作区(如果不返回工作区刷新,有时候会报错Error loading design或者can't read "Startup(-L)": no such element in array)

右击tb模块,选择仿真(一定要选择tb模块来仿真,因为目的是为了测试)

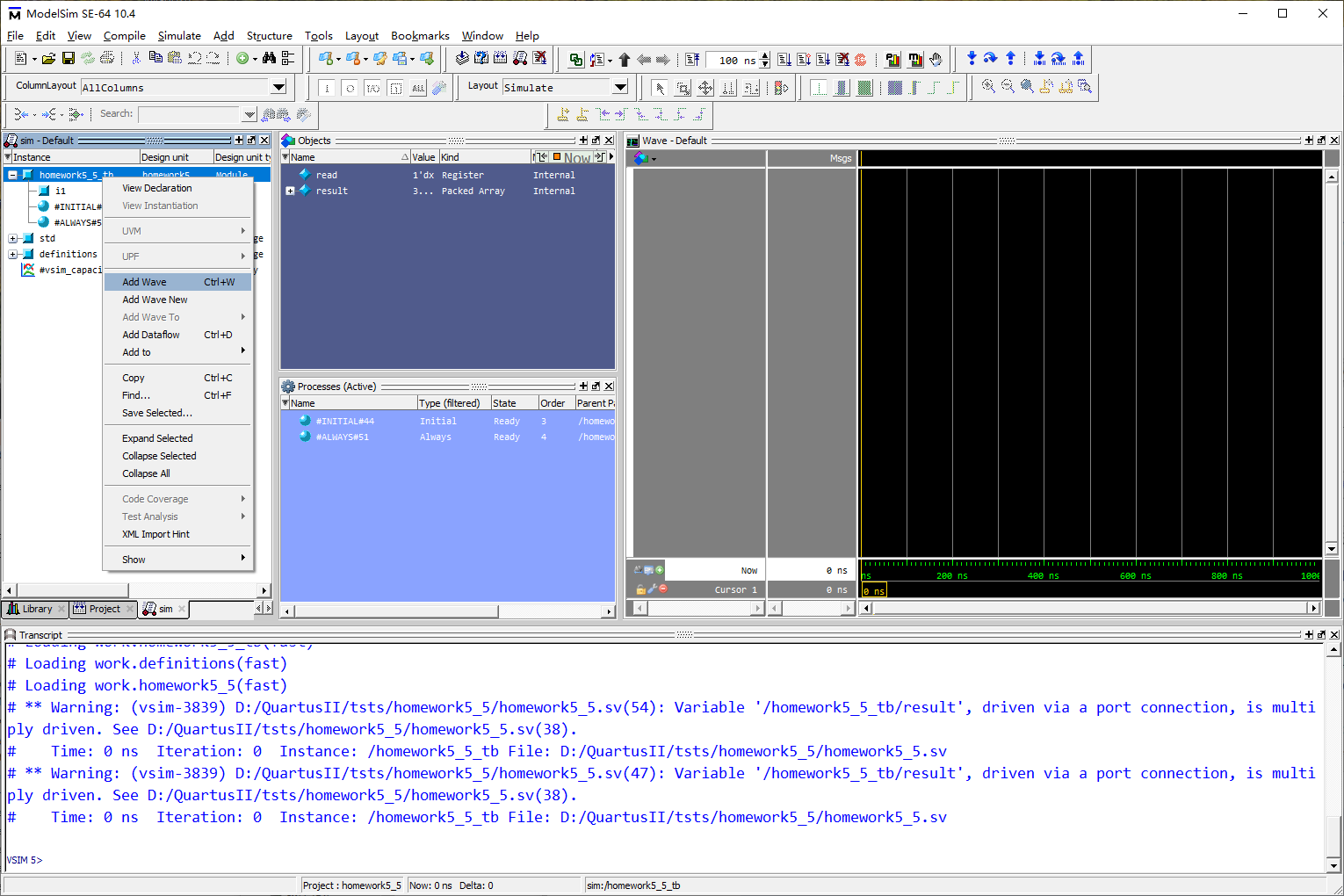

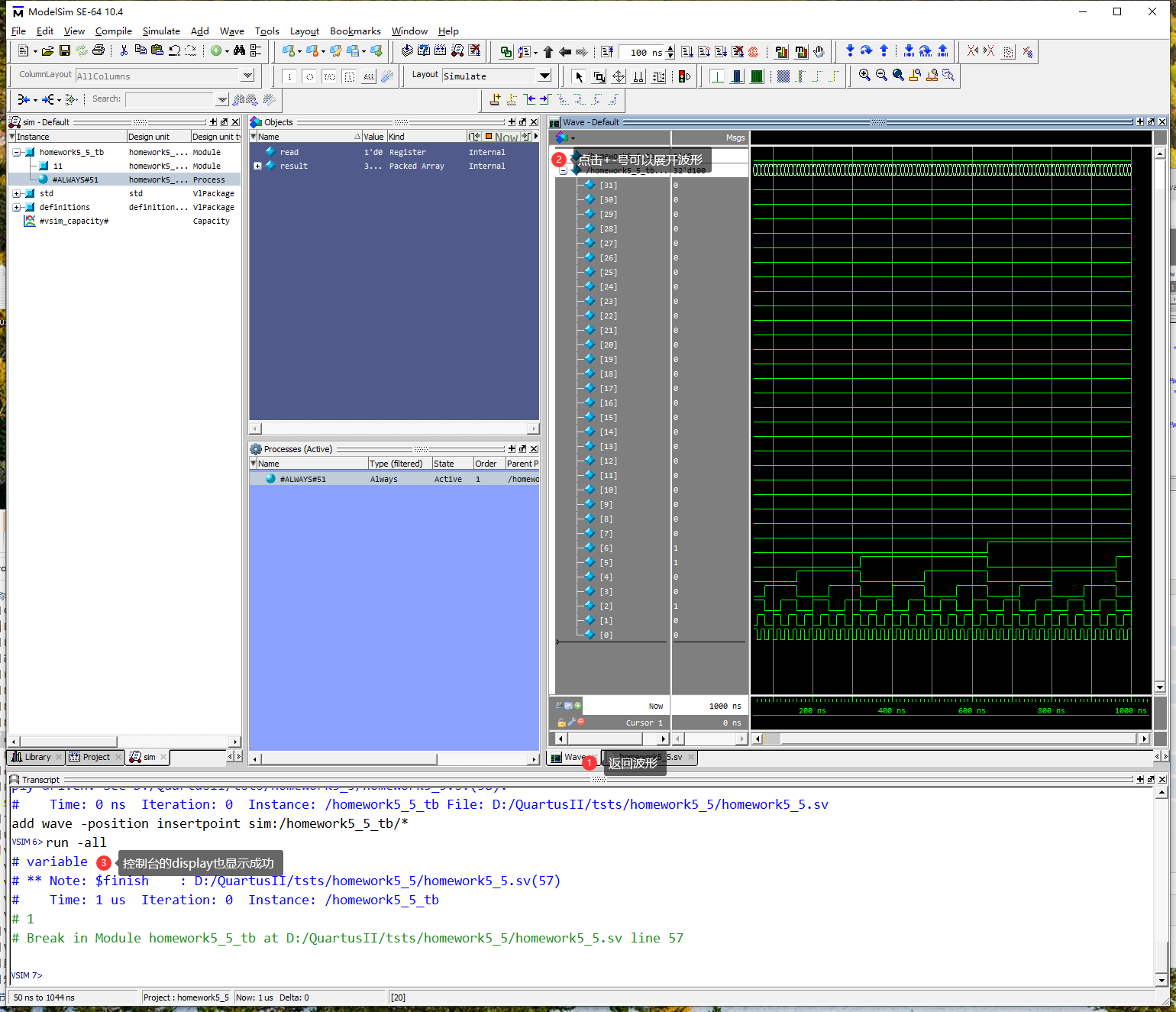

右击tb模块,添加波形

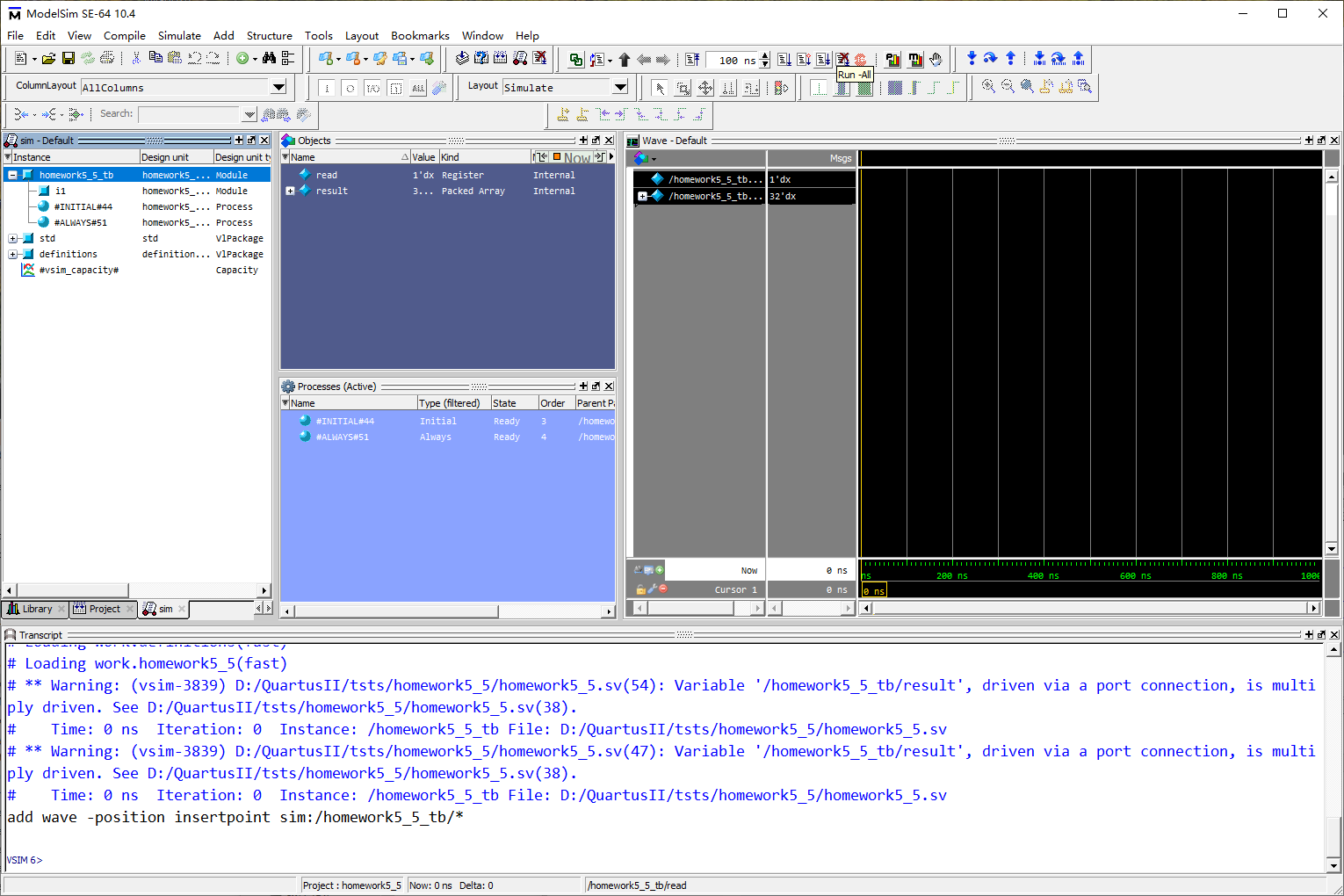

run-all

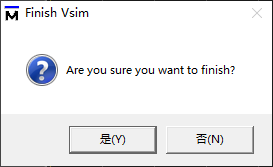

选择否

返回波形视图,查看仿真结果

版权声明: 本博客所有文章除特别声明外,均采用 CC BY-NC-SA 3.0 许可协议。转载请注明出处!

合集:

FPGA

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· 震惊!C++程序真的从main开始吗?99%的程序员都答错了

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人