操作系统 - 计算机组成原理

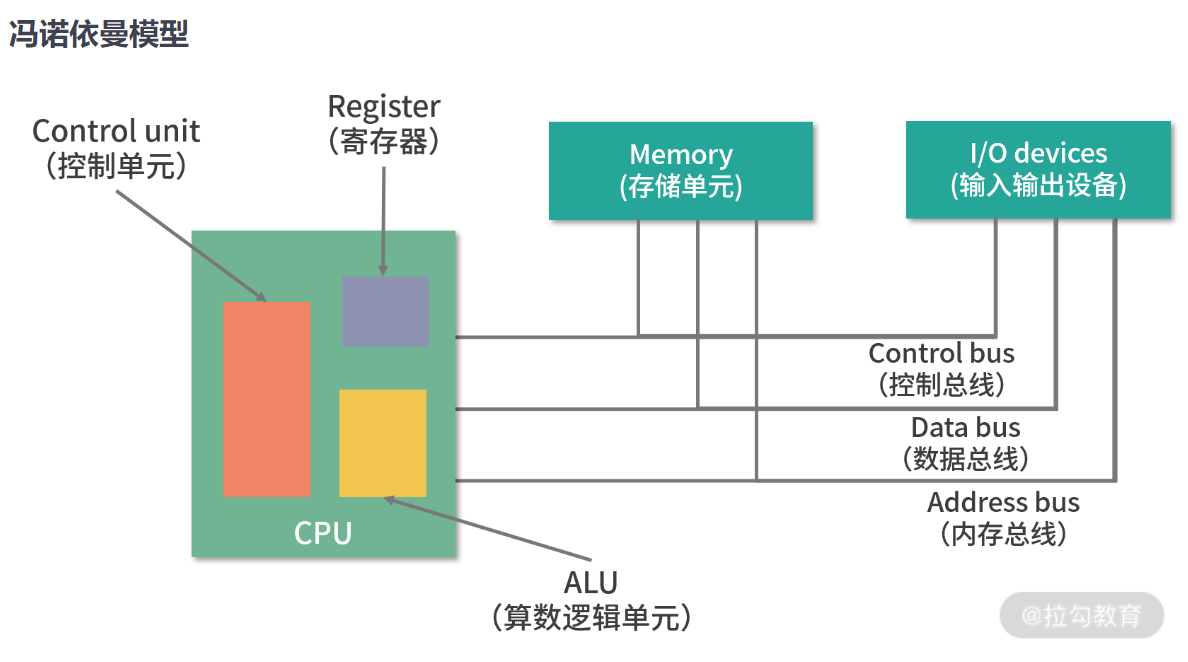

冯诺依曼模型

-

CPU

每次可以计算4个byte - 32位CPU; 每次可以计算8个byte - 64位CPU; 32 和 64 称为CPU的位宽。

-

寄存器

离CPU近的存储来存储需要被计算的数字

PC寄存器(Program Counter, PC): 存储需要CPU执行的指令的地址;始终保存下一条CPU要执行的指令地址

SP寄存器(Stack Pointer, SP):保存中断断点,保存函数调用的返回值,保存CPU现场数据等;始终指向栈空间的顶端,实现LIFO特性

-

总线

数据总线:读写内存中的数据;控制总线:发送和接收关键信号比如中断信号,设备复位等;地址总线:专门用来指定CPU将要操作的内存地址。

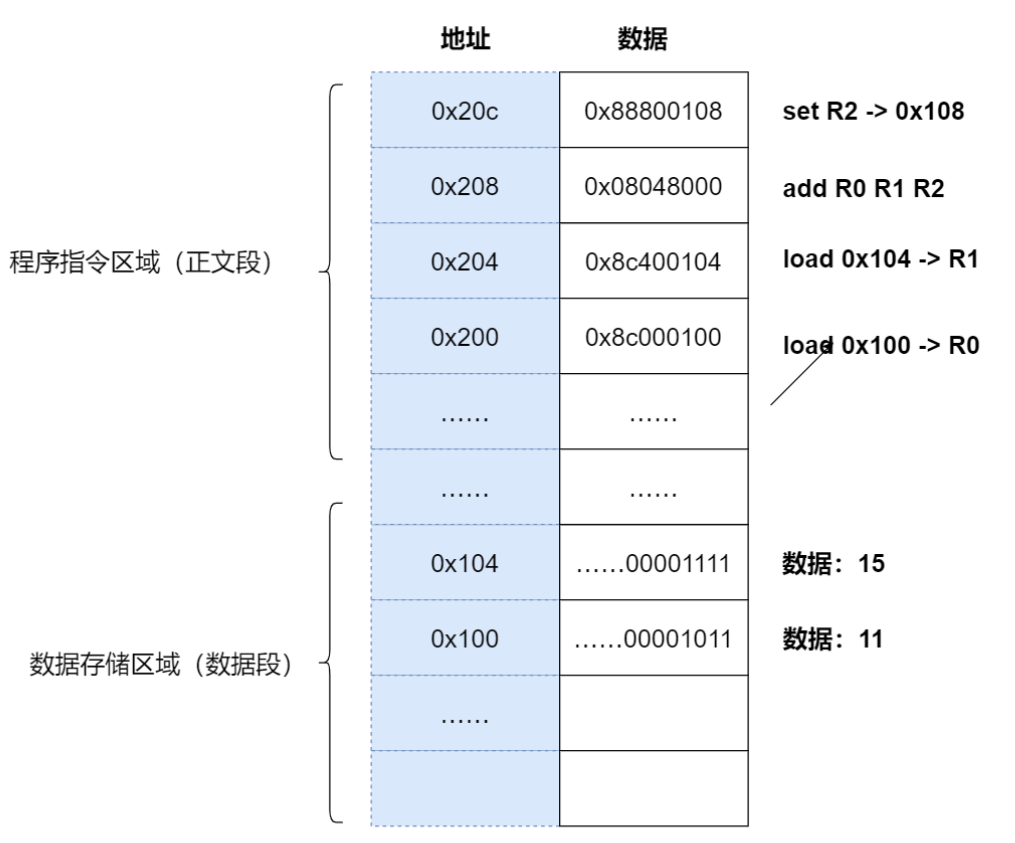

执行a=11+15

- 字符串“a=11+15”经过编译器将高级语言翻译成CPU认识的4条指令:

load 0x100 -> R0

load 0x104 -> R1

add R0 R1 R2

set R2 -> 0X108

-

CPU执行指令:

一个CPU指令周期:CPU通过PC指针读取对应内存地址的指令(Fetch)-> CPU对指令进行解码(Decode)-> CPU执行指令(Execution)-> CPU将结果存回寄存器或者将寄存器存入内存(Store)

CPU通过石英晶体产生脉冲转化为时钟信号驱动,每一次时钟信号高低电平转换就是一个时钟周期。CPU的主频也就是时钟信号的频率,也是CPU指令执行速度的表征。

存储器分级

| 名称 | 存储大小 | 读写速度 | 缓存命中 |

|---|---|---|---|

| 寄存器 | 4/8 个字节 X N | 0.5个CPU时钟周期 | |

| L1 Cache | e.g. 100 Kb (看具体型号) | 2~4个CPU时钟周期 | 80% |

| L2 Cache | e.g. 2 Mb (看具体型号) | 10~20个CPU时钟周期 | |

| L3 Cache | e.g. 2 Mb, 16 Mb (看具体型号) | 20~60个CPU时钟周期 | L1L2L3=95% |

| 内存 | e.g. 16 G (看具体型号) | 200~300个CPU时钟周期 | |

| SSD | e.g. 256 G | 比内存慢10~1000倍 |

其他

CPU的位宽,一般说的是数据总线的位宽;数据总线是双向总线,用来在CPU和存储器IO等之间交换数据。地址总线,是专门用于传输地址,是单向总线,只能从CPU向外部传,地址总线的位数决定了CPU可直接寻址的内存空间。但进程在访问内存的时候,访问的都是逻辑地址,逻辑地址是由操作系统提供。对于32位操作系统,所提供的逻辑地址寻址范围就是4GB

浙公网安备 33010602011771号

浙公网安备 33010602011771号