【学习】FPGA 学习笔记

数字芯片

芯片,又被称为微电路、微芯片、集成电路,它其实是半导体元件产品的统称。

芯片的分类有很多,按照不同的处理信号可分为模拟芯片和数字芯片两种。

- 模拟芯片:利用的晶体管的放大作用,用来产生、放大和处理各种模拟信号,种类细且繁多,包括模数转换芯片(ADC)、放大器芯片、电源管理芯片、PLL锁相环)等等;

- 模拟信号:说简单点就是连续信号,也就是连续发出的;

- 数字芯片:利用的是晶体的开关作用,用来产生、放大和处理各种数字信号,数字芯片一般进行逻辑运算,CPU、内存芯片和DSP芯片(数字信号处理器)都属于数字芯片。

- 数字信号:就是离散信号,简单点就是不连续的。

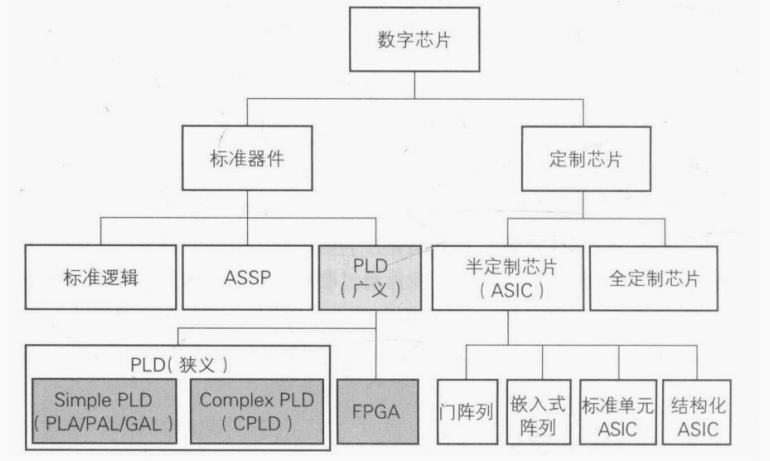

数字芯片可分为两种,标准器件(CPU、GPU及FPGA)和定制芯片。

一般来说,芯片越偏向定制,逻辑器件的性能(速度)、集成度(门数)和设计自由度等方面就越有优势,但相对地,设计、制造相关的开发费用(Non-Recurring Engineering,NRE 成本)也较为高昂,且从下单到出货的周转时间(Turn Around Time,TAT)会更长。

定制芯片

定制芯片也大致分为两种:从基础单元(cell)开始设计的全定制芯片和使用经过优化的标准单元实现的半定制芯片。

-

全定制芯片:

- 全定制需要集成电路设计团队对全部芯片的内部电路进行专门的优化设计以达到芯片的最佳性能,就像一座工程建筑所有的细节均需要从头设计。

-

半定制芯片:

- 工程师可以使用大量标准的逻辑单元进行芯片电路的构建,这些逻辑单元已经局部布局完毕,并且经过了可靠性验证,例如各类门电路、存储单元、乘法器等。

- 其包含了使用标准单元库进行设计的标准单元ASIC(特定应用集成电路,cell-based ASIC);

- 在预先摆放好标准单元(布线前的工艺全部完成)的晶圆上通过定制布线形成产品的门阵列(gate array);

- 介于标准单元ASIC和门阵列之间的嵌入式阵列(embedded array);

- 通过在门阵列上提供SRAM(静态随机存取存储器,Static Random-Access Memory)、时钟PLL(倍频器,可以将频率翻倍)等通用模块来将定制成本最小化的结构化ASIC(structured ASIC),等等。

- 这些工艺都是为了降低定制芯片的NRE成本和缩短TAT时间。

- 工程师可以使用大量标准的逻辑单元进行芯片电路的构建,这些逻辑单元已经局部布局完毕,并且经过了可靠性验证,例如各类门电路、存储单元、乘法器等。

标准器件

- ASSP:专用标准产品(Application Specific Standard Parts,ASSP)的设计和实施方式完全和ASIC(特定应用集成电路,Application Specific Integrated Circuit)相同,它们本质上是相同的东西,唯一的区别是,ASSP专门针对特定应用市场,可以销售给不止一个用户(因此才被称为“标准”),而 ASIC的设计和销售只针对单个客户。

- PLD:可编程逻辑器件(Programmable Logic Device,PLD),它不同于面向固定用途且无法定制的ASSP,是一类可通过编程来实现各种逻辑电路的逻辑器件。PLD这种 " 可以编程的逻辑电路 " 由于具有允许用户通过编程手段自由实现定制电路等特色,近些年取得了很大的发展。

FPGA

FPGA是PLD的一种,它通过组合使用器件内大量逻辑块来实现用户所需电路。FPGA比以往(狭义)的PLD设计自由度更高,并有近似于门阵列的构造,因此被命名为FPGA(Field-Programmable Gate Array,现场可编程门阵列)。FPGA量产时不具有任何逻辑功能(未编程状态),从半导体厂商的角度来看,它是一种可量产的标准器件,从用户的角度来看,它是一种不需要开模等高额费用(NRE成本)又可以随时实现定制电路的方便的ASIC。

EDA

EDA(Electronic Design Automation,电子设计自动化) 技术就是以计算机为工具,设计者在 EDA 软件平台上,用硬件描述语言完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。EDA 技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。利用EDA技术可以在FPGA芯片上构造自己所需的硬件电路,常见软件有Virtuoso,ICC2,Calibre。

F4PGA

F4PGA 是一个完全开源的工具链,旨在通过使用一组可插入的开源工具优化和自动化 FPGA 开发工作流程来推动 FPGA 得到更广泛的采用。目标是成为一个完整的 FOSS (Free and open source software,自由与开源软件)FPGA 工具链。

examples实例

此处省略f4pga代码clone和conda环境搭建

# 环境下载,目前文件存放在/home/f4pga/opt/f4pga/xc7/share/f4pga/arch

for PKG in $F4PGA_PACKAGES; do

wget -qO- https://storage.googleapis.com/symbiflow-arch-defs/artifacts/prod/foss-fpga-tools/symbiflow-arch-defs/continuous/install/${F4PGA_TIMESTAMP}/symbiflow-arch-defs-${PKG}-${F4PGA_HASH}.tar.xz | tar -xJC $F4PGA_INSTALL_DIR/${FPGA_FAM}

done

- F4PGA编译目录设置

# 这里的目录选择上一步中的下载路径

export F4PGA_INSTALL_DIR=~/opt/f4pga

- 硬件选择

export FPGA_FAM="xc7"

- 环境准备

source "$F4PGA_INSTALL_DIR/$FPGA_FAM/conda/etc/profile.d/conda.sh"

- 编译

# 编译,并在counter_test中创建build路径,输出到counter_text/build/arty_35中

TARGET="arty_35" make -C counter_test

Yosys

**Yosys **是一款开源的逻辑综合工具,支持几乎所有的Verilog2005(Verilog为硬件描述语言,于1984年诞生)中的可综合语法,能够把Verilog代码转换成BLIT/EDIF/BTOR/SMT-LIB/Simple RTL Verilog等网表。Yosys使用方便,鉴于其轻量的特点,运行速度快,且能够生成图形化的网表展示方式。但是,缺少时序分析功能。

VTR

开源软件vtr(Verilog-to-Routing)一项全球性的合作项目,旨在为进行 FPGA 架构和 CAD 研究和开发提供一个开源框架。vtr 设计流程将数字电路的 verilog 描述和目标 FPGA 架构的描述作为输入,然后执行。其对于FPGA架构的描述使用的是xml文件的形式。

浙公网安备 33010602011771号

浙公网安备 33010602011771号