4.3-高速缓冲存储器

概述

为什么使用cache

- 避免cpu“空等”现象

- cpu和主存(dram)的速度差异过大

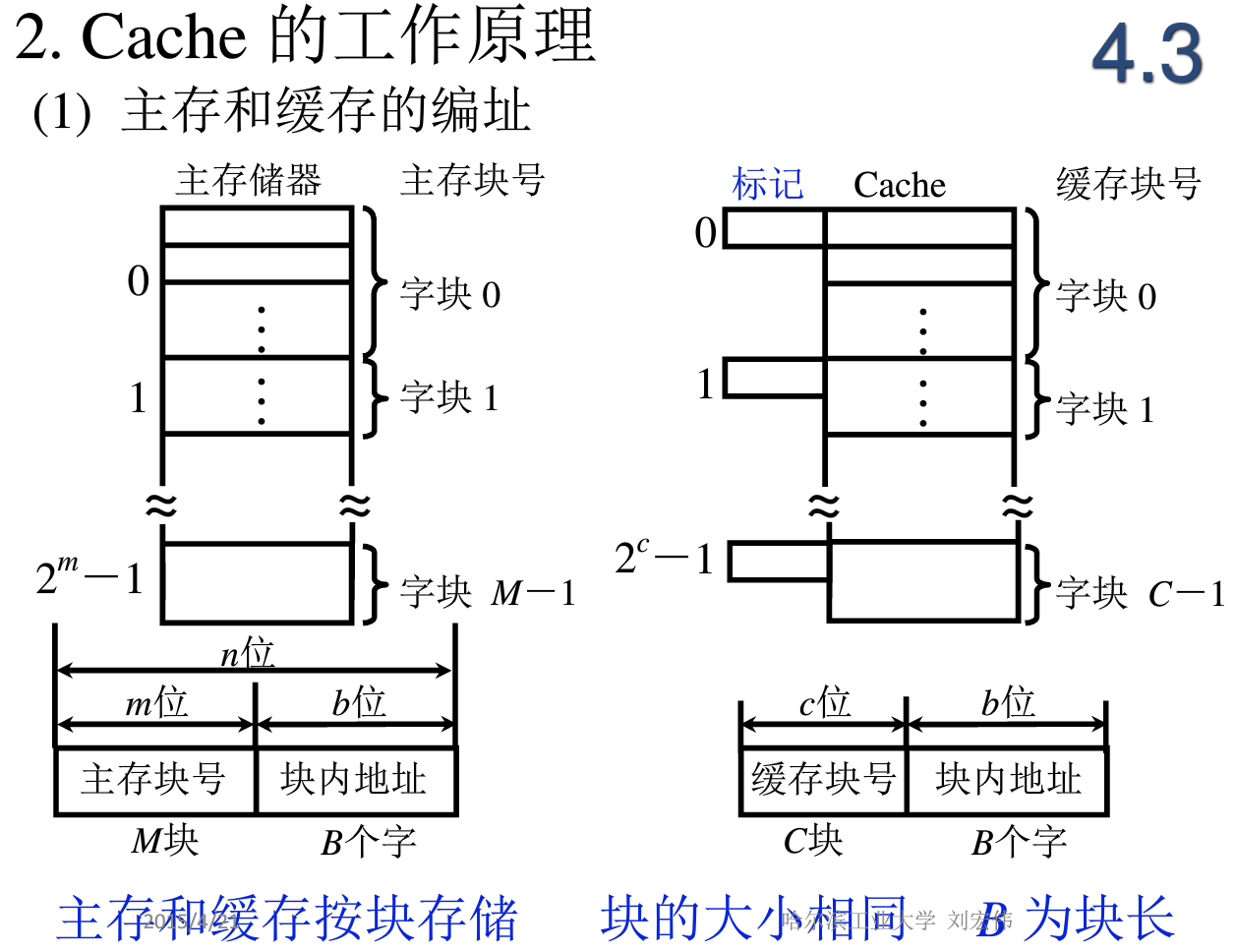

Cache的工作原理

- 主存和缓存的编址

- 命中与未命中

缓存共有C块

主存共有M块 M>>C

命中 主存块 调入 缓存

主存块与缓存块建立了对应关系

用标记记录与某缓存块建立了对应关系的主存块号

未命中 主存块未调入缓存

主存块与缓存块未建立对应关系

- Cache的命中率

cpu预访问的信息在cache 中的比率

命中率与cache的容量和块长有关

一般每块可取4-8个字

块长取一个存取周期内从主存调出的信息长度

CRAY_1 16体交叉 块长取16个存储字

IBM370/168 4体交叉 块长取4个存储字

(64位x4=256位)

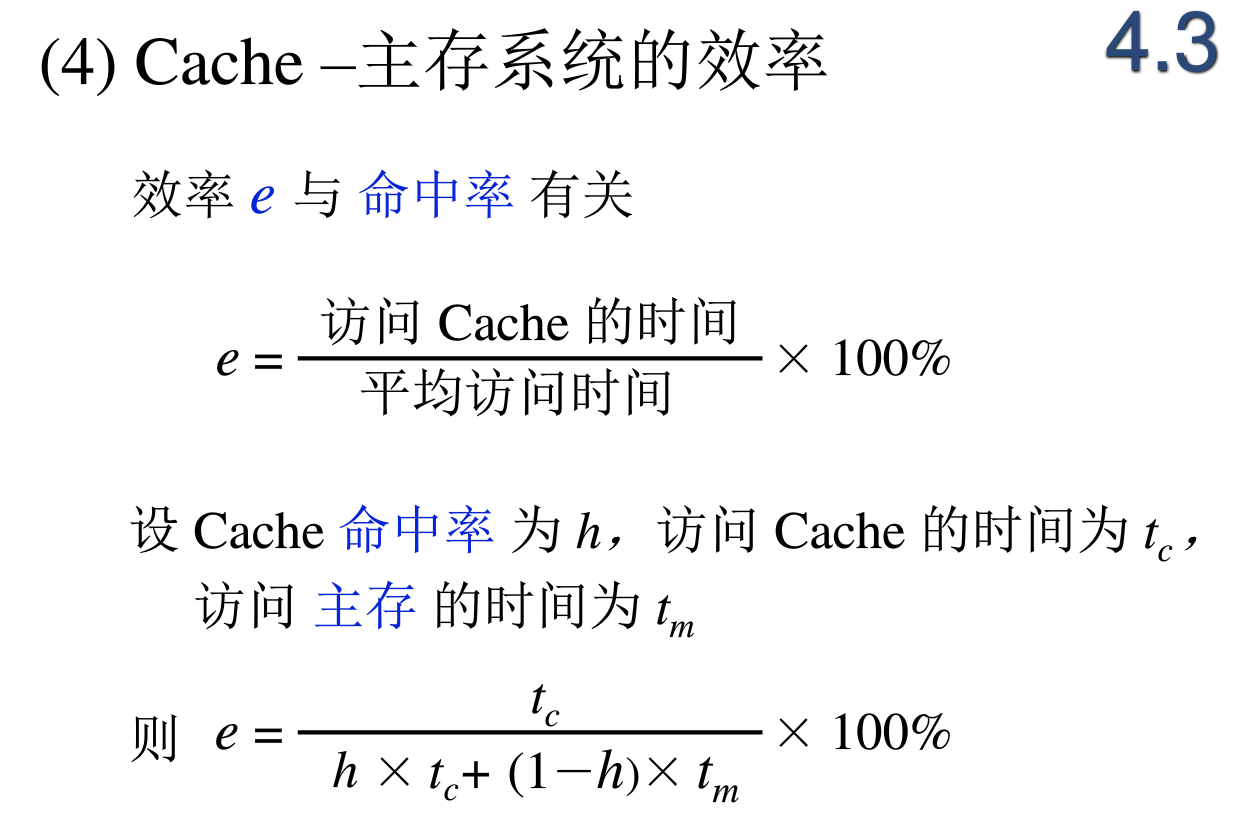

- Cache-主存系统的效率

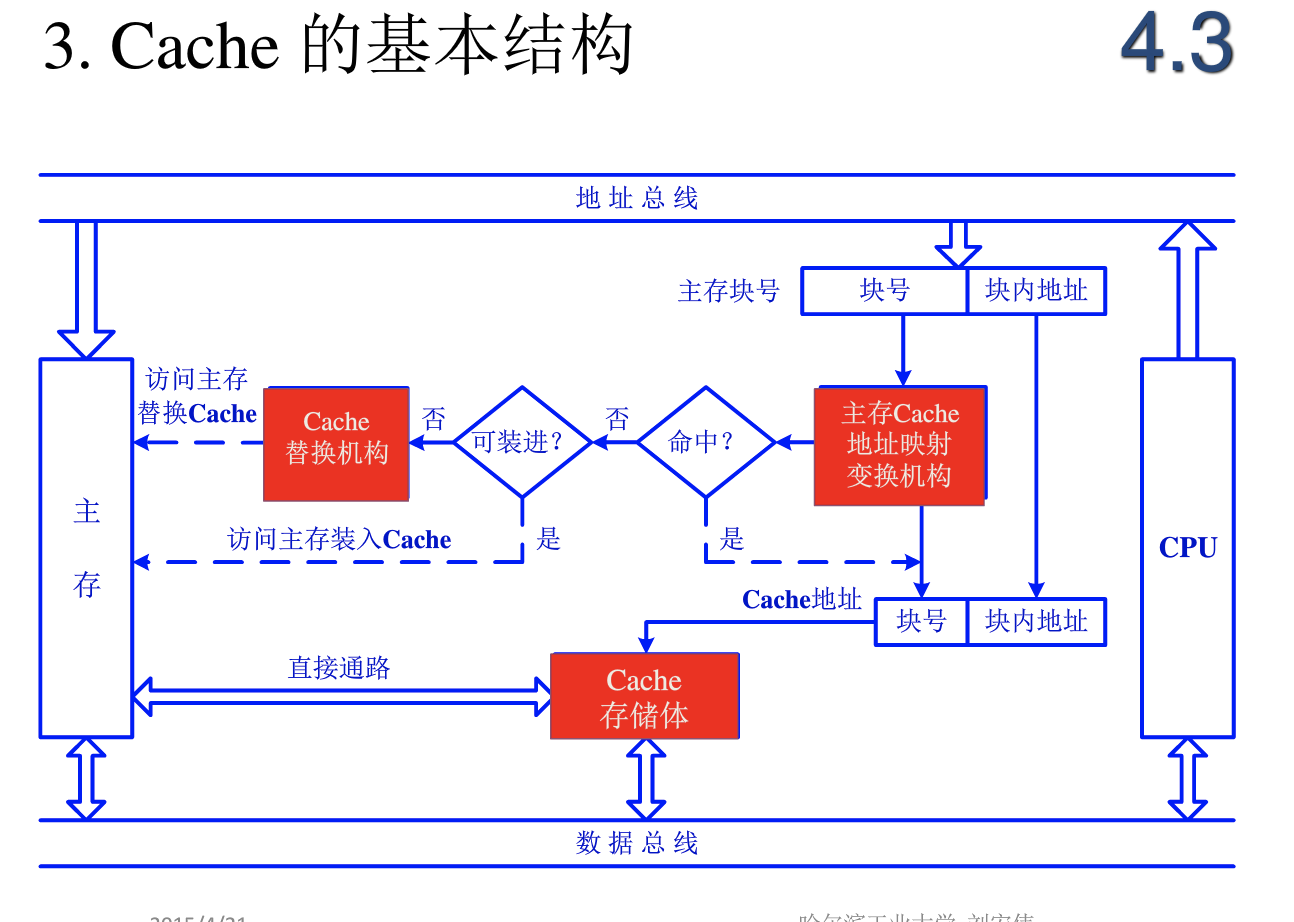

Cache的基本结构

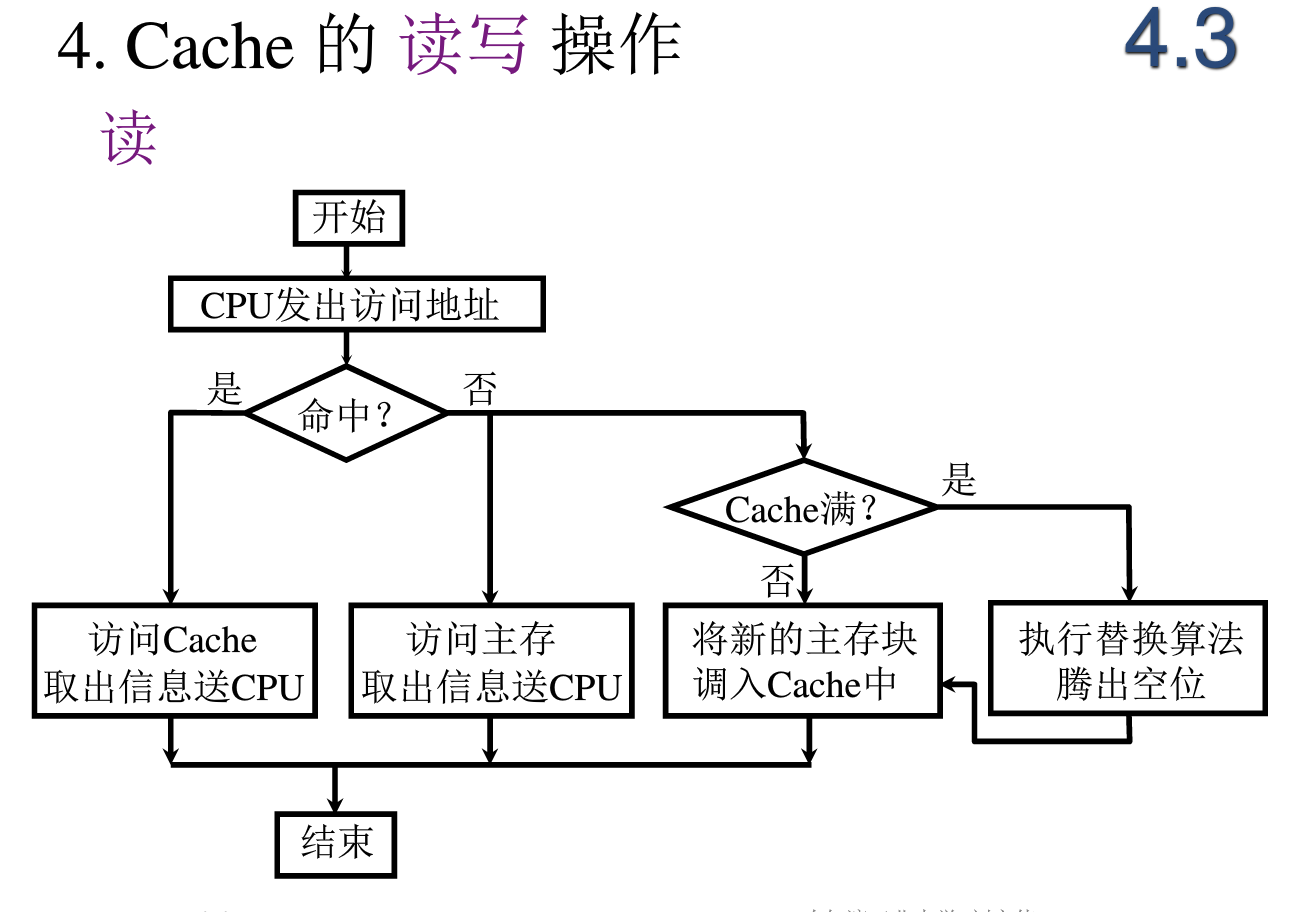

Cache的读写操作

写 Cache和主存的一致性

- 写直达法(Write-through)

- 写操作时数据既写入cache又写入主存

- 写操作时间就是访问主存的时间

- cache块退出时,不需要对主存执行写操作

- 更新策略比较容易实现

- 写回法(Write-back)

- 写操作时只把数据写入cache而不写入主存

- 当cache数据被替换出去时才写回主存

- 写操作时间就是访问cache的时间

- cache块退出时,被替换的块要写回主存,增加了cache的复杂性

Cache的改进

- 增加cache的级数

- 片载(片内)cache

- 片外cache

- 统一缓存和分立缓存

- 指令cache

- 数据cache

- 与指令执行的控制方式有关

- 是否流水

Pentium 8K 指令 Cache 8K 数据 Cache

PowerPC620 32K 指令 Cache 32K 数据 Cache

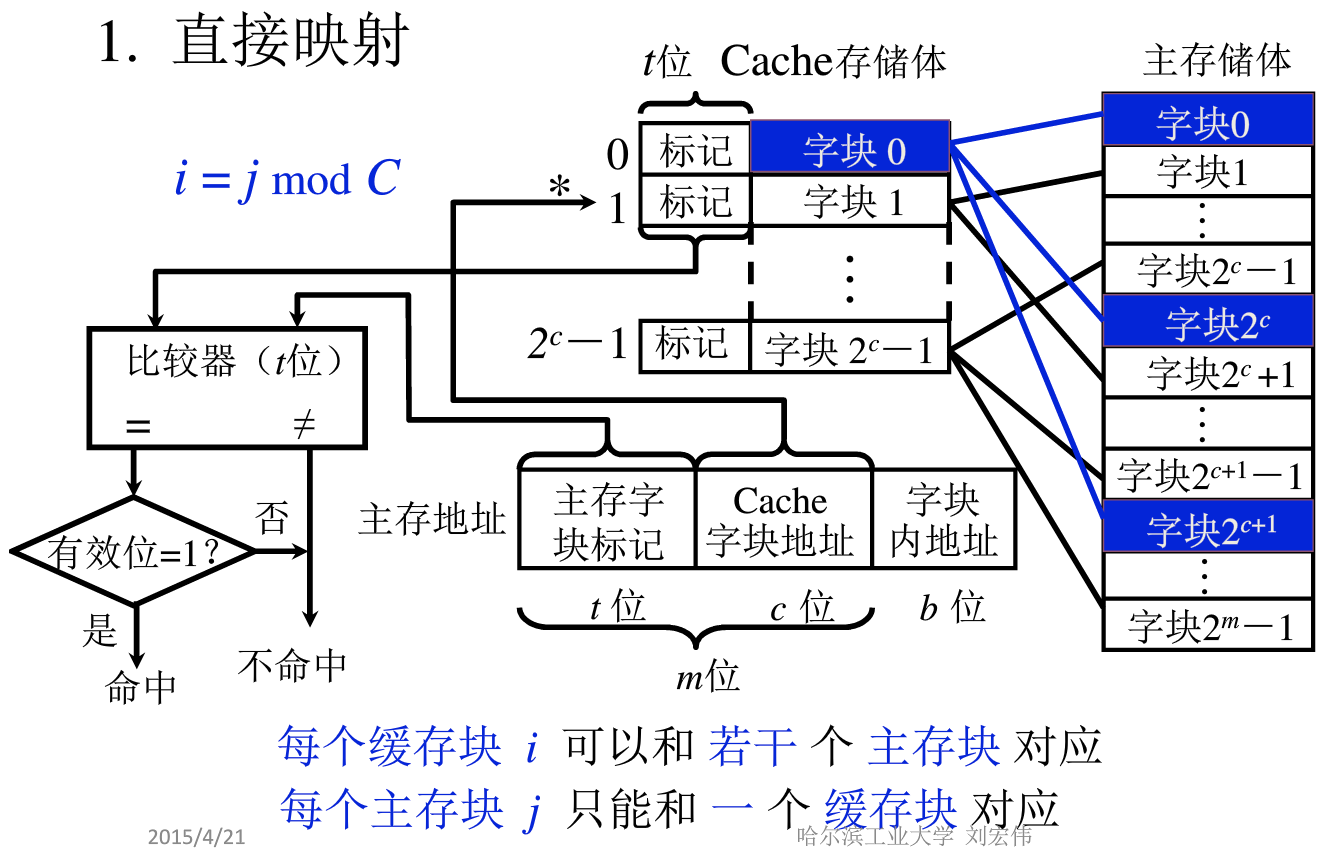

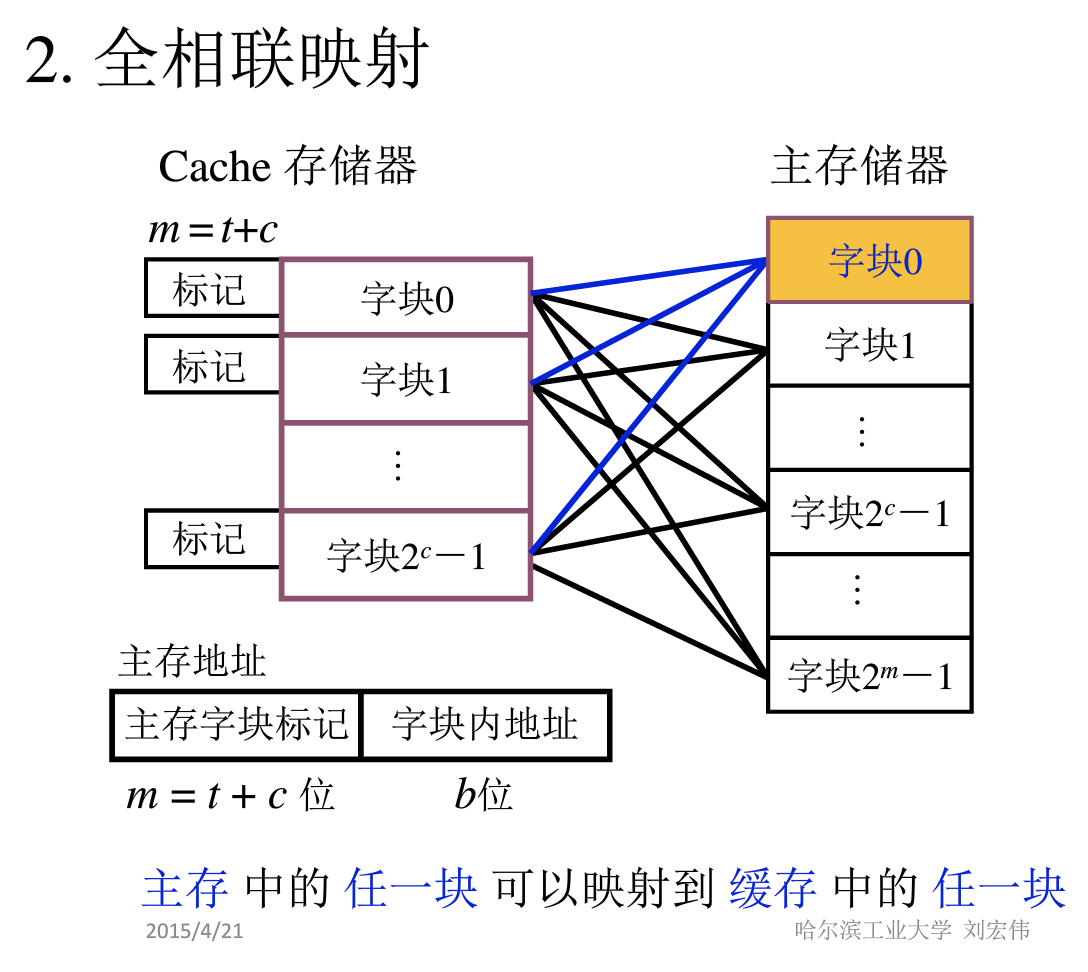

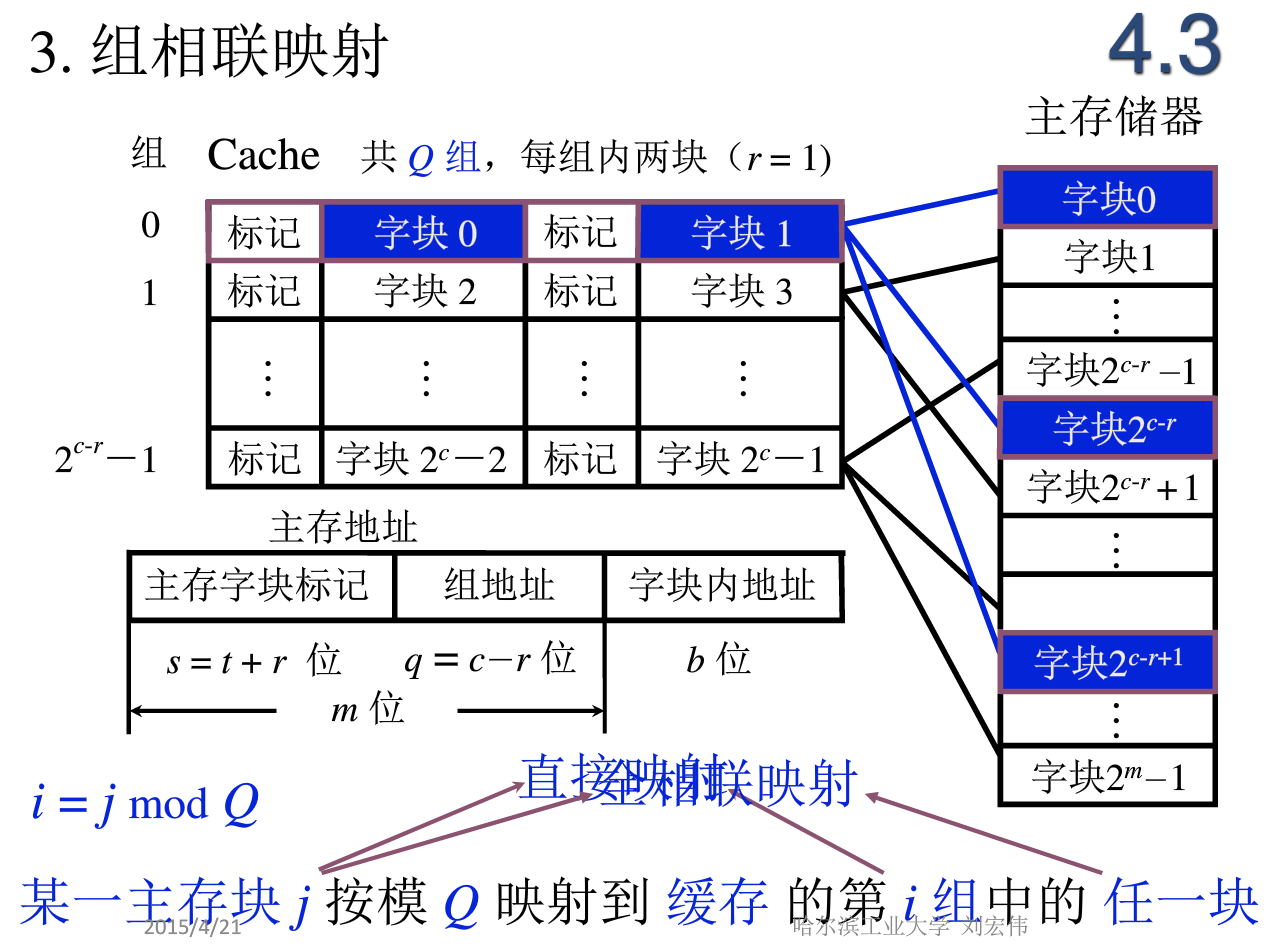

Cache-主存的地址映射

直接映射

全相联映射

组相联映射

替换算法

- 先进先出(FIFO)算法

- 近期最少使用(LRU)算法

浙公网安备 33010602011771号

浙公网安备 33010602011771号