4.2-主存储器

概述

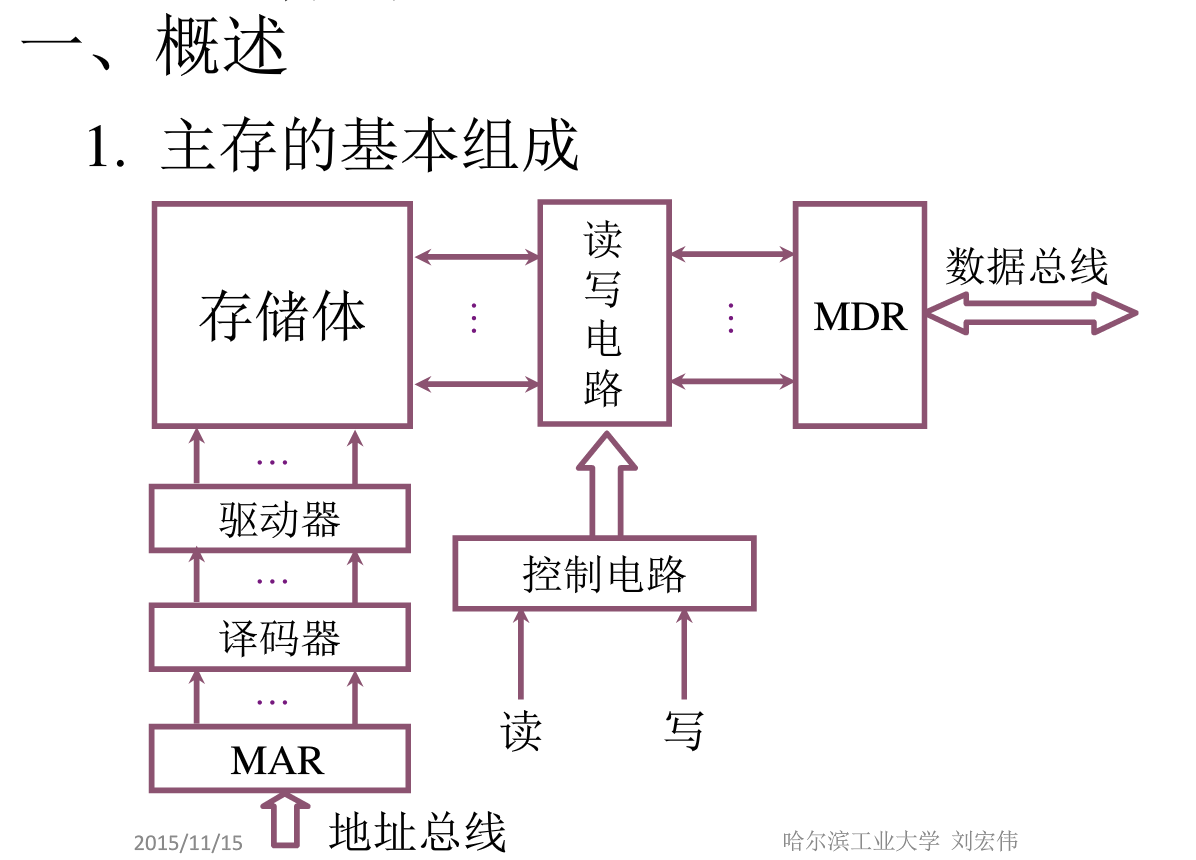

主存的基本组成

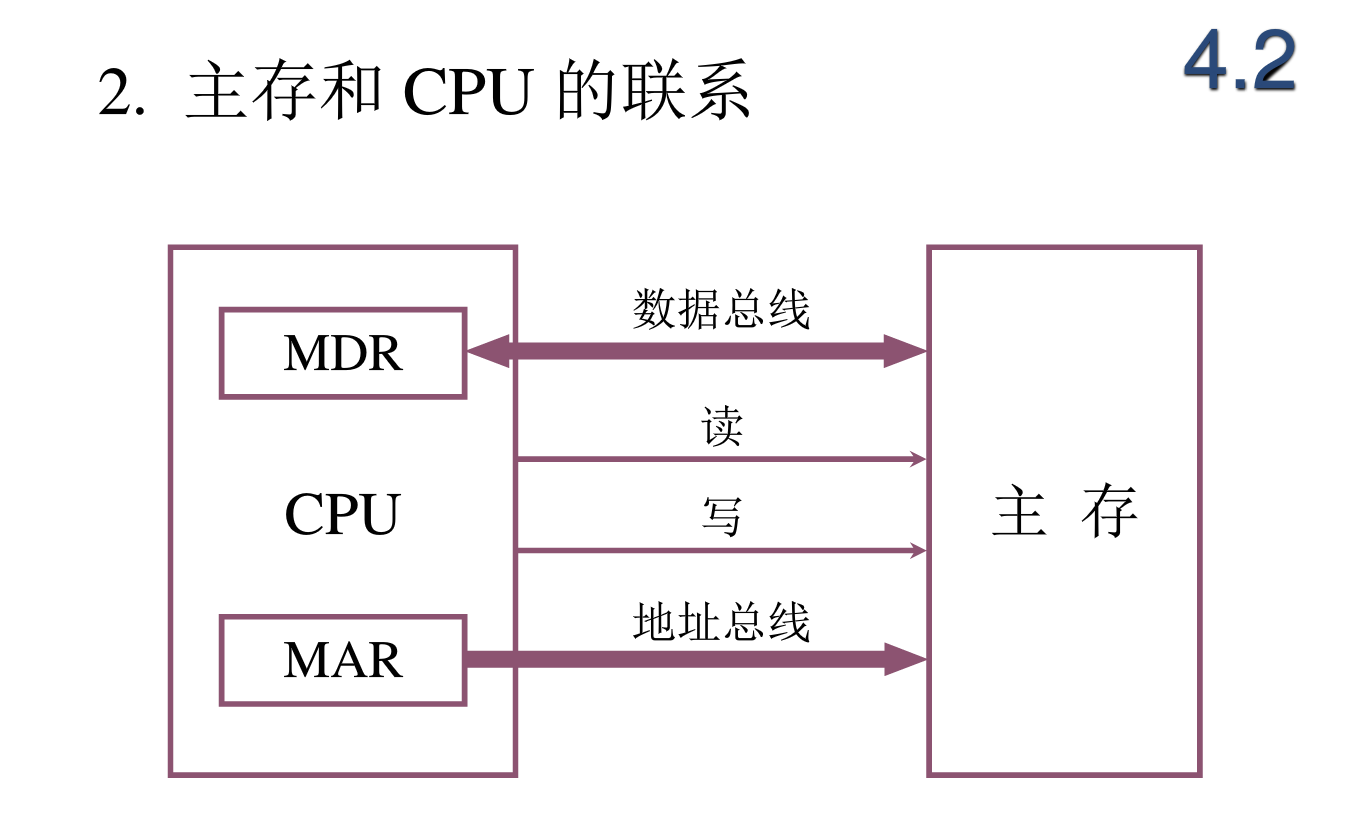

主存与cpu之间的联系

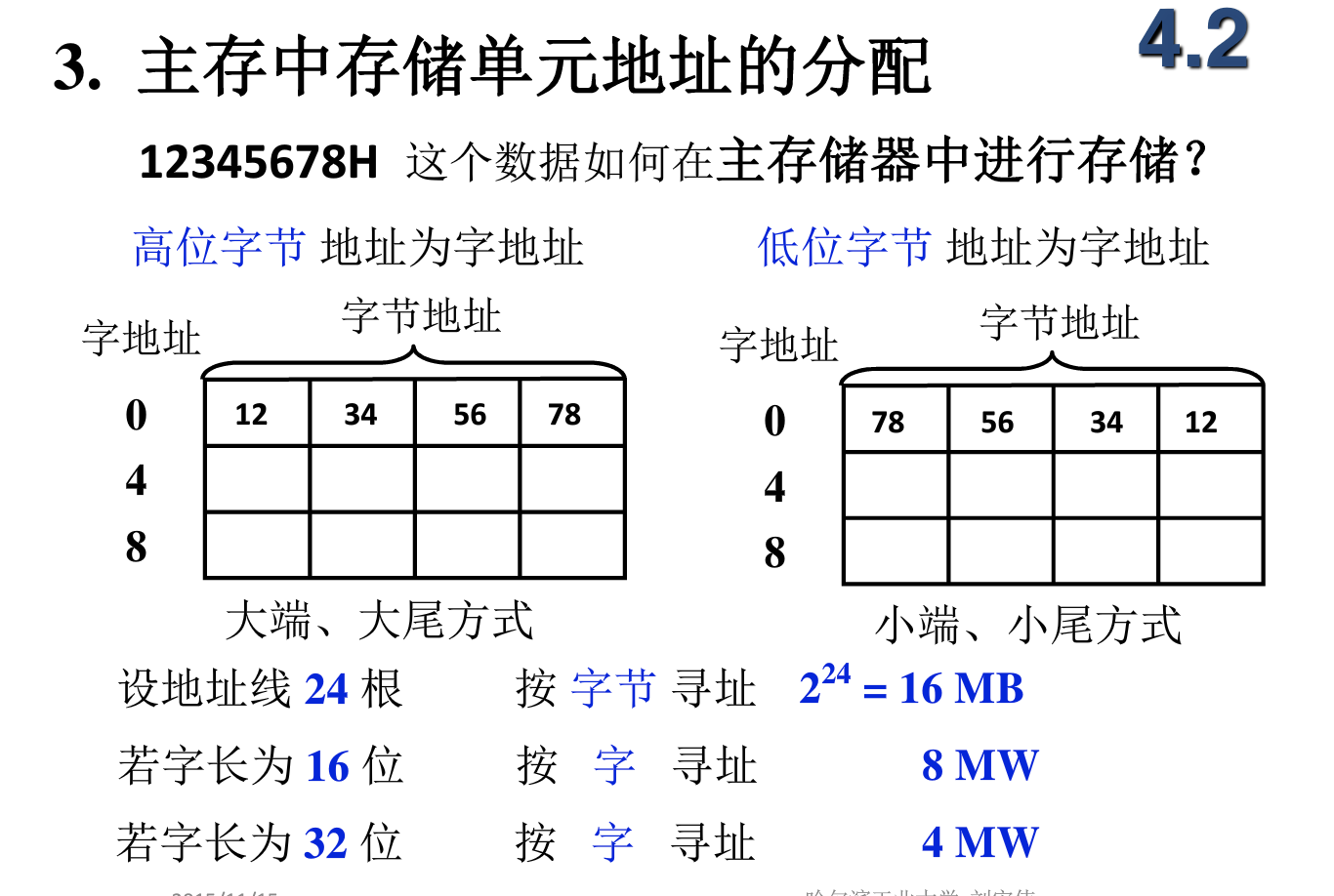

主存中储存单元地址的分配

主存的技术指标

- 存储容量

- 主存 存放二进制代码的总位数

- 存储速度

- 存取时间 存储器的访问时间 读出时间、写入时间

- 存取周期 连续两次独立的存储器操作 (读或写)所需的最小间隔时间 读周期、写周期

- 存储器的带宽

- 位/秒

半导体存储芯片介绍

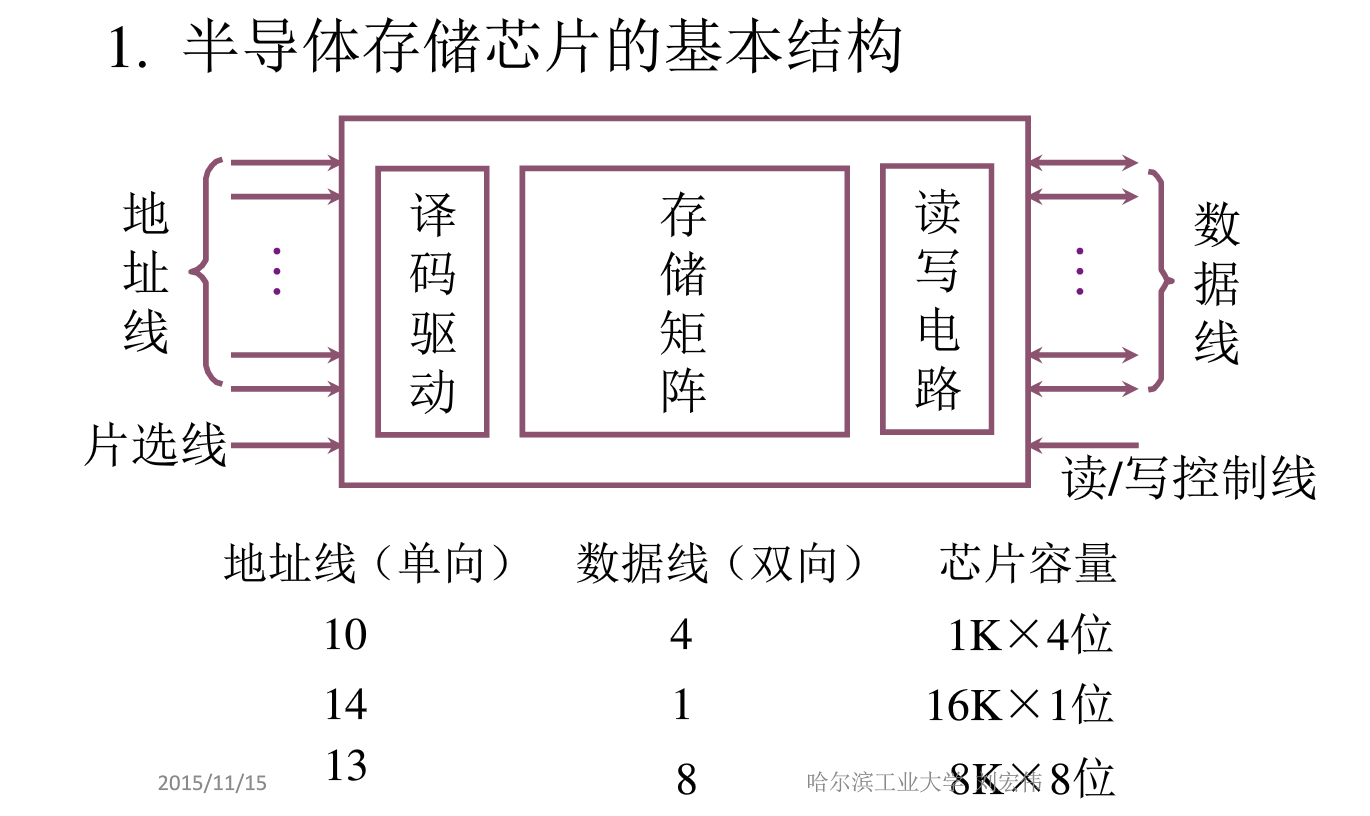

半导体存储芯片的基本结构

片选线 CS CE

读/写控制线 WE(低电平写,高电平读)

OE(允许读) WE(允许写)

- 存储芯片片选线的作用

半导体存储芯片的译码驱动方式

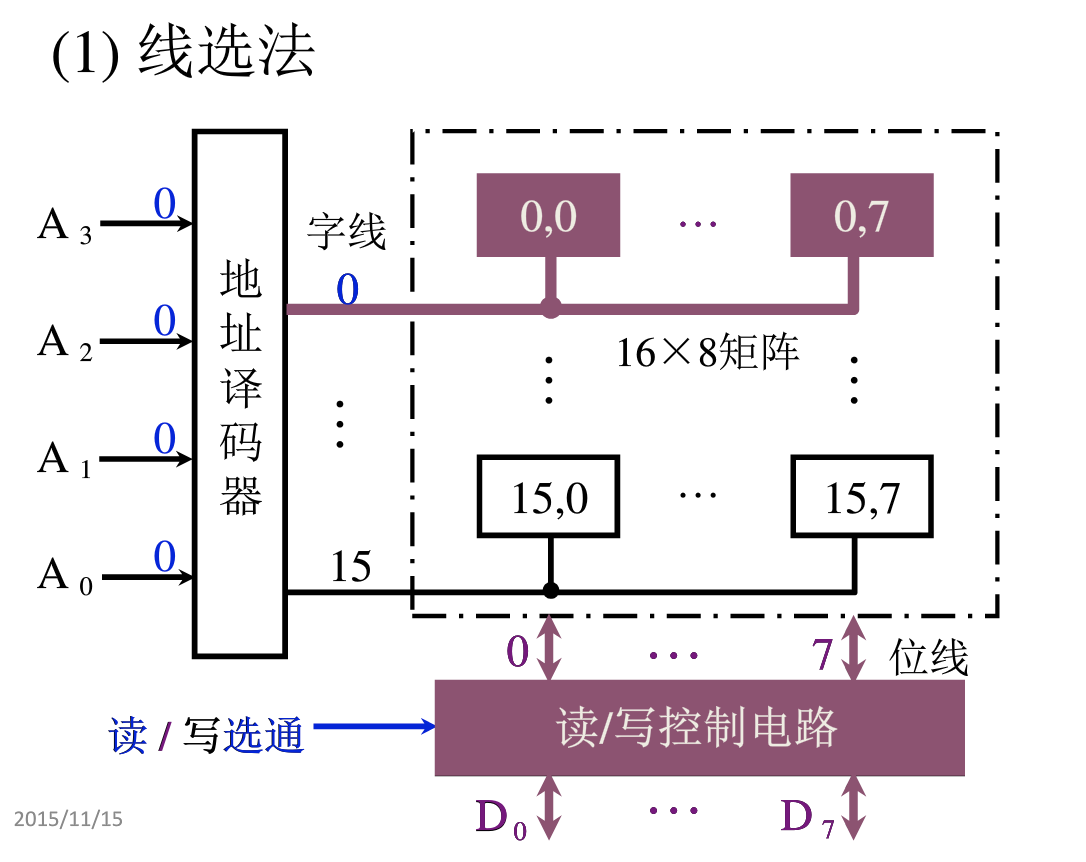

- 线选法

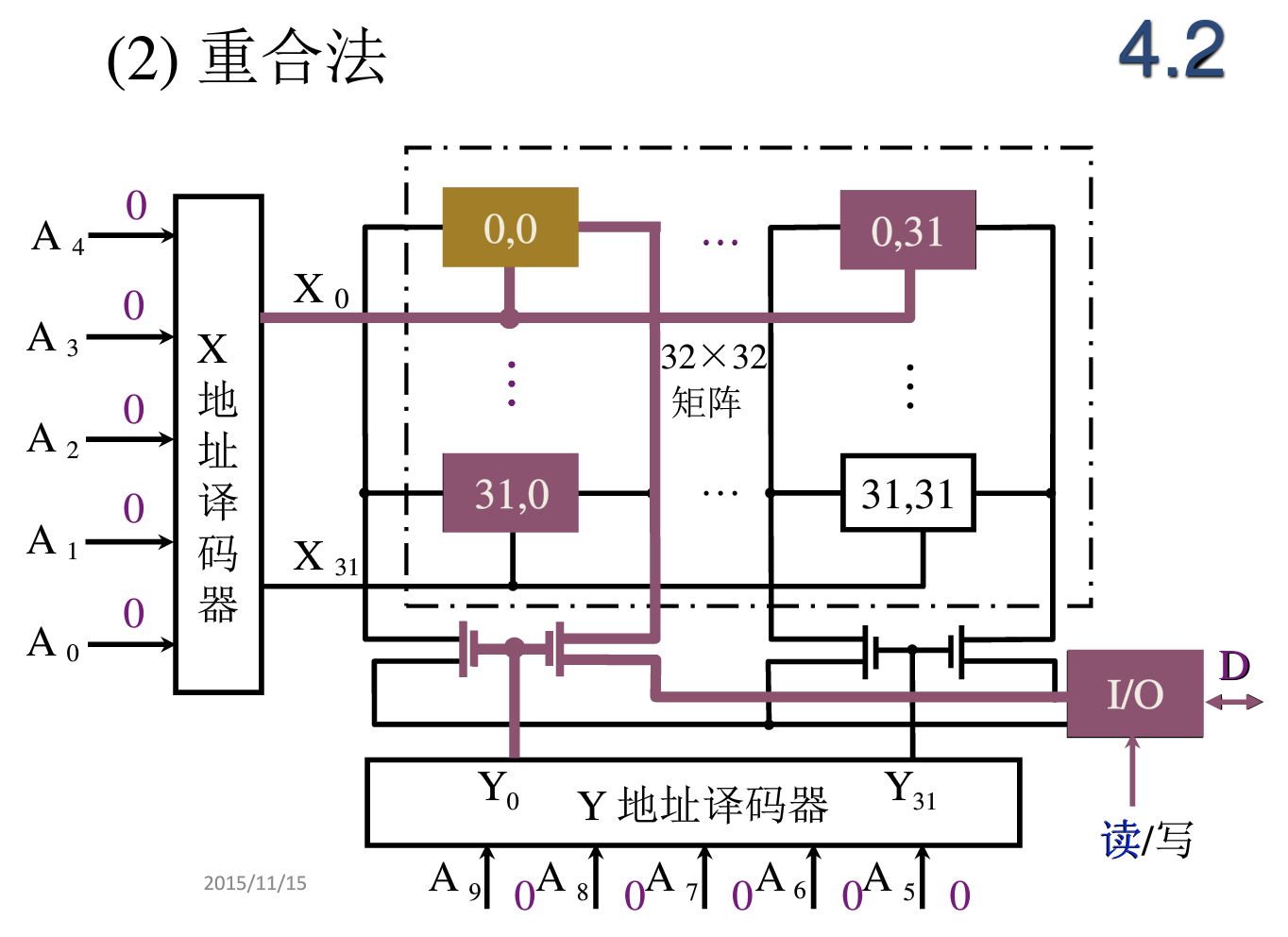

- 重合法

随机存取存储器(RAM)

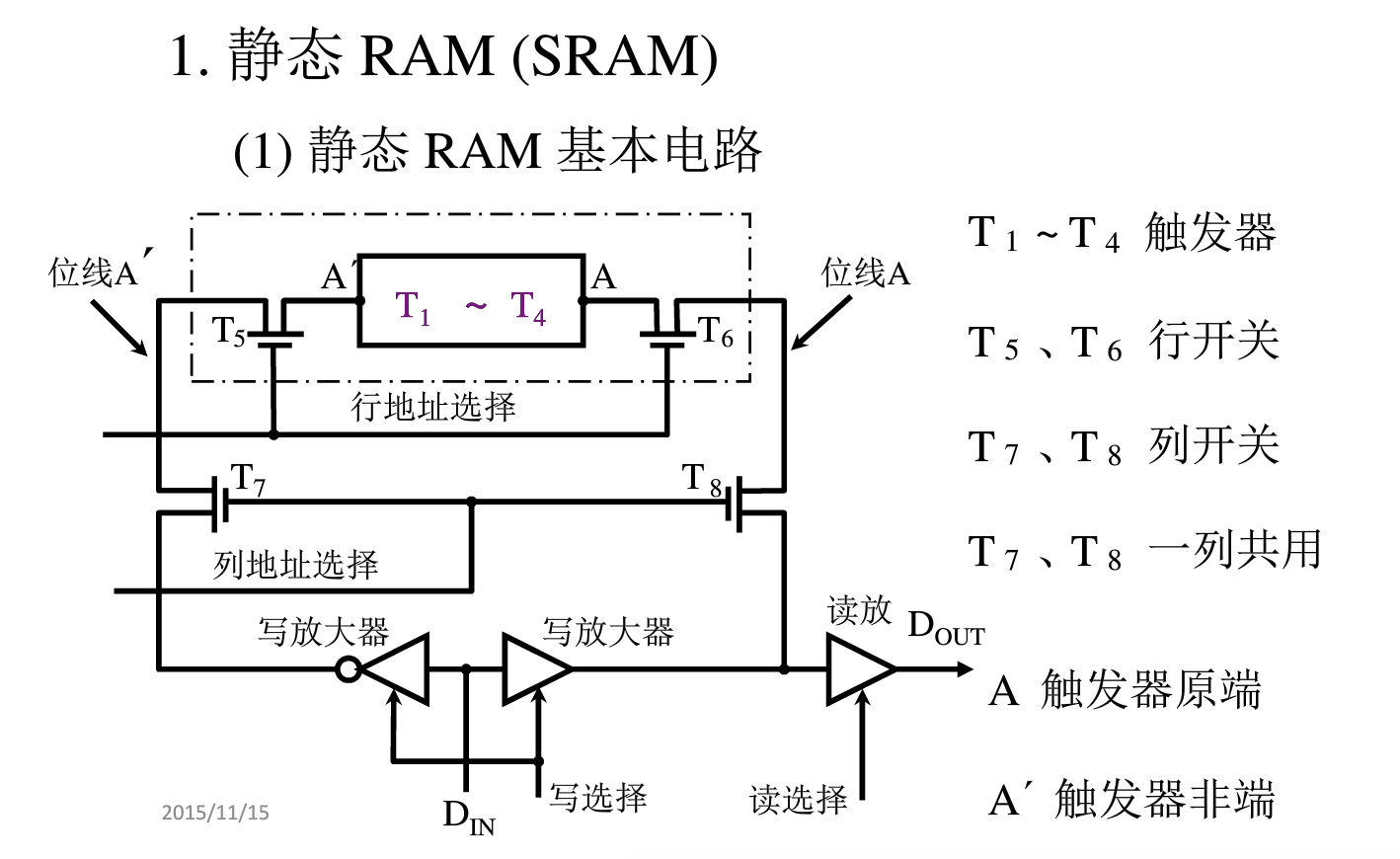

静态RAM(SRAM)

- 保存0和1的原理是什么

- 基本单元电路的构成是什么

- 对单元电路如何读出和写入

- 典型芯片的结构是什么样子的

- 静态ram芯片 如何进行读出和写入操作

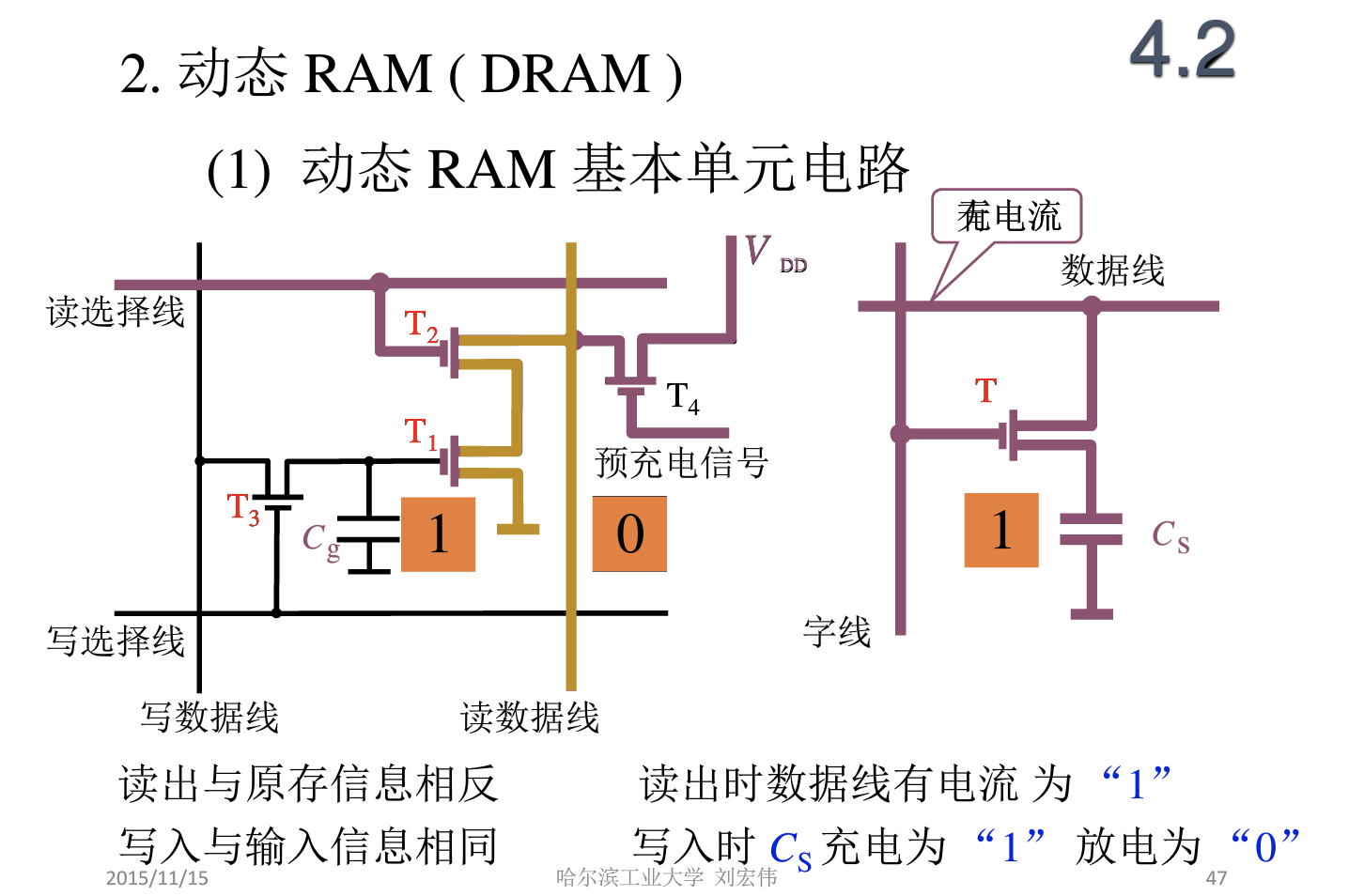

动态RAM(DRAM)

- 保存0和1的原理是什么

- 基本单元电路的构成是什么

- 对单元电路如何读出和写入

- 典型芯片的结构是什么样子的

- 动态ram芯片 如何进行读出和写入操作

- 动态ram为什么要刷新,刷新方法

动态RAM和静态RAM的比较

| 主存 DRAM | 缓存 SRAM | |

|---|---|---|

| 存储原理 | 电容 | 触发器 |

| 集成度 | 高 | 低 |

| 芯片引脚 | 少 | 多 |

| 功耗 | 小 | 大 |

| 价格 | 低 | 高 |

| 速度 | 慢 | 快 |

| 刷新 | 有 | 无 |

只读存储器(ROM)

- 早期的只读存储器(厂家写好了内容)

- 改进1--用户可以自己写--一次性

- 改进2--可以多次写--要对信息进行擦除

- 改进3--电可擦写--特定设备

- 改进4--电可擦写--直接连接到计算机上

掩模ROM(MROM)

- 行列选择线交叉处有MOS管为“1”

- 行列选择线交叉处无MOS管为“0”

PROM(一次性编程)

- 熔丝断 0

- 熔丝未断 1

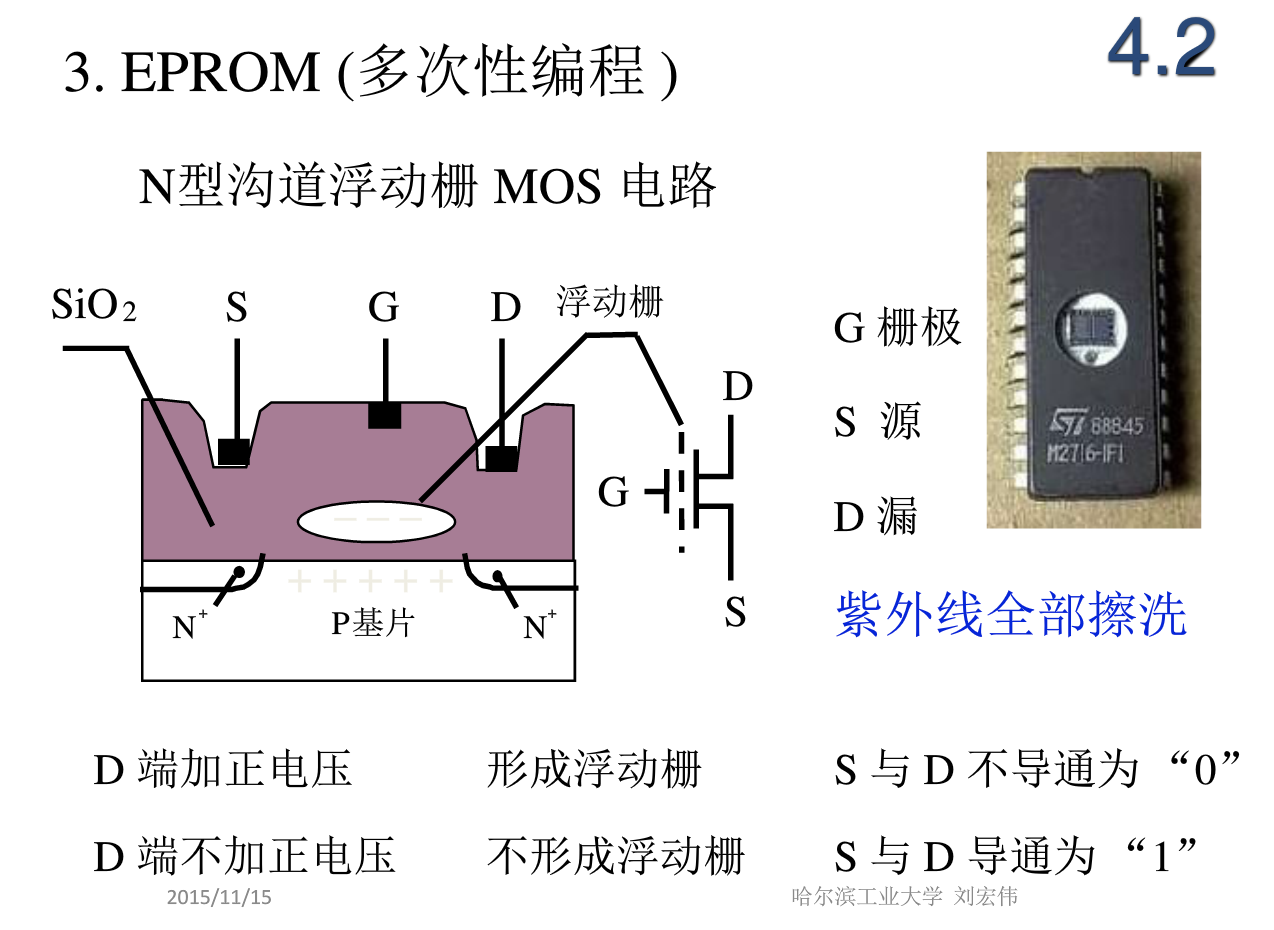

EPROM(多次编程)

EEPROM(多次编程)

- 电可擦写

- 局部擦写

- 全部擦写

Flash Memory(闪存型存储器)

- EPROM (价格便宜 集成度高)

- EEPROM (电可擦写重写)

- 比EEPROM快 (具备RAM功能)

存储器与CPU的连接

存储器容量的扩展

- 位扩展

- 增加存储字长

- eg:2片 1k x 4位的组成1k x 8位的存储器

- 字扩展

- 增加存储字的数量

- eg:2片 1k x 8位的组成2k x 8位的存储器

- 同时扩展

- 字、位同时扩展

- eg:8片 1k x 4位的存储芯片组成 4k x 8位的存储器

存储器与CPU的连接

- 地址线的连接

- 数据线的连接

- 读写命令线的连接

- 片选线的连接

- 合理选择存储芯片

- 其他 时序、负载

存储器的校验

编码的最小距离

任意两组合法代码之间二进制位数的最少差异编码的纠错、检错能力与编码的最小距离有关

- L-1=D+C (D>=C)

- L--编码的最小距离 L=3

- D--检测错误的位数 具有一位纠错能力

- C--纠正错误的位数

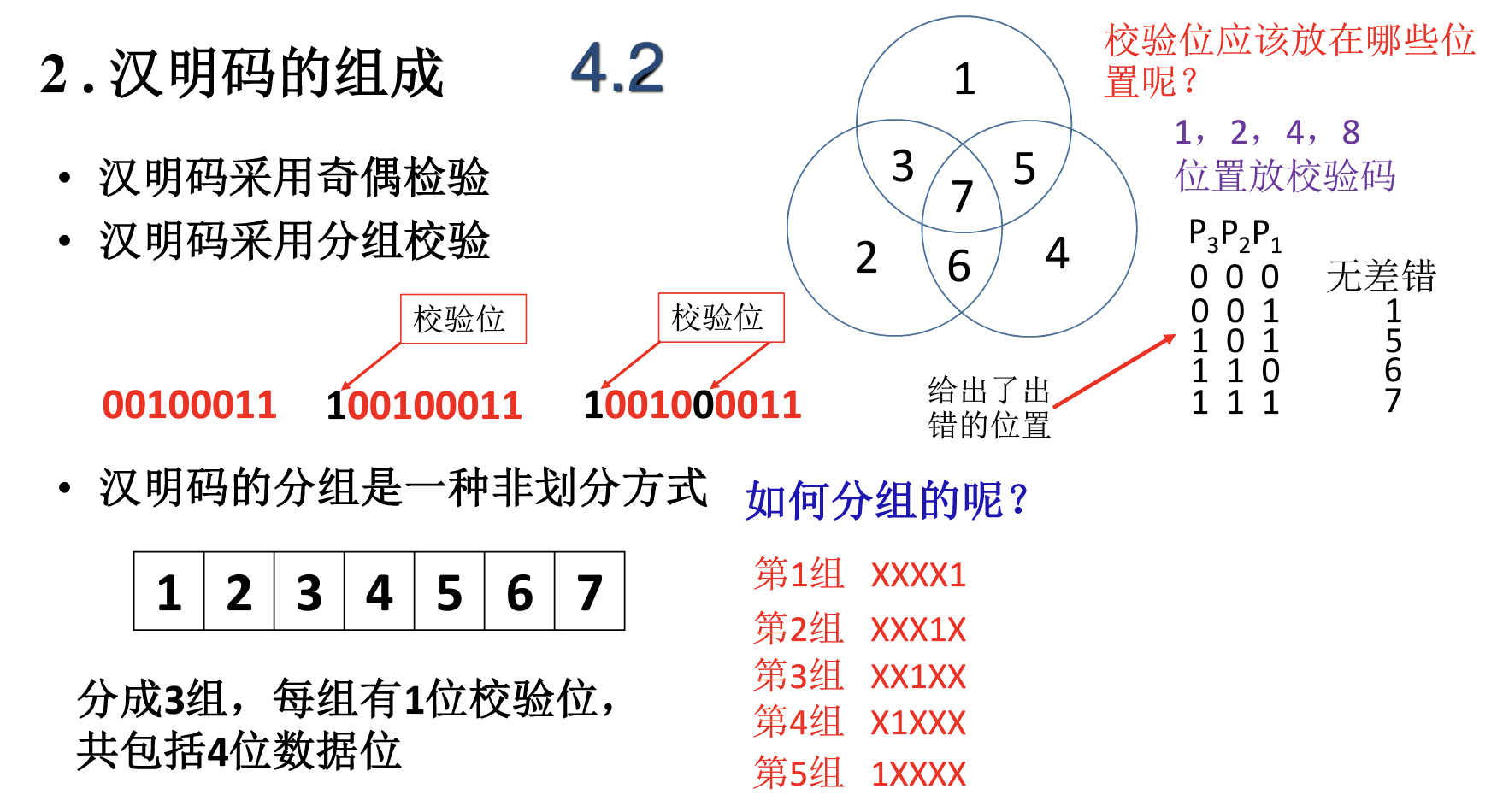

汉明码是具有一位纠错能力的编码

汉明码的组成

提高访存速度的措施

- 采取高速器件

- 采用层次结构 Cache-主存

- 调整主存结构

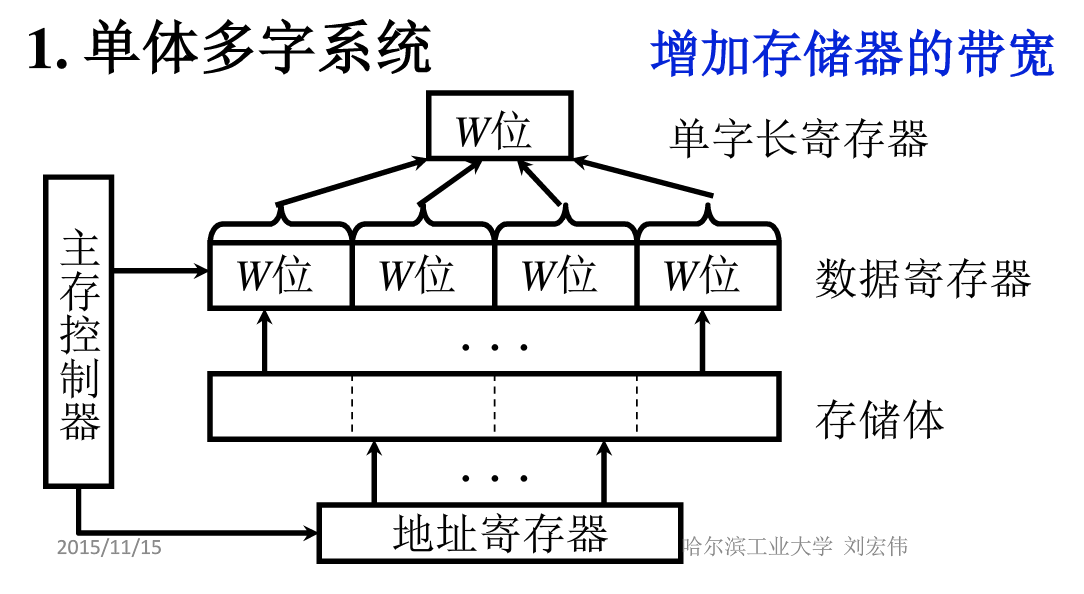

单体多字系统

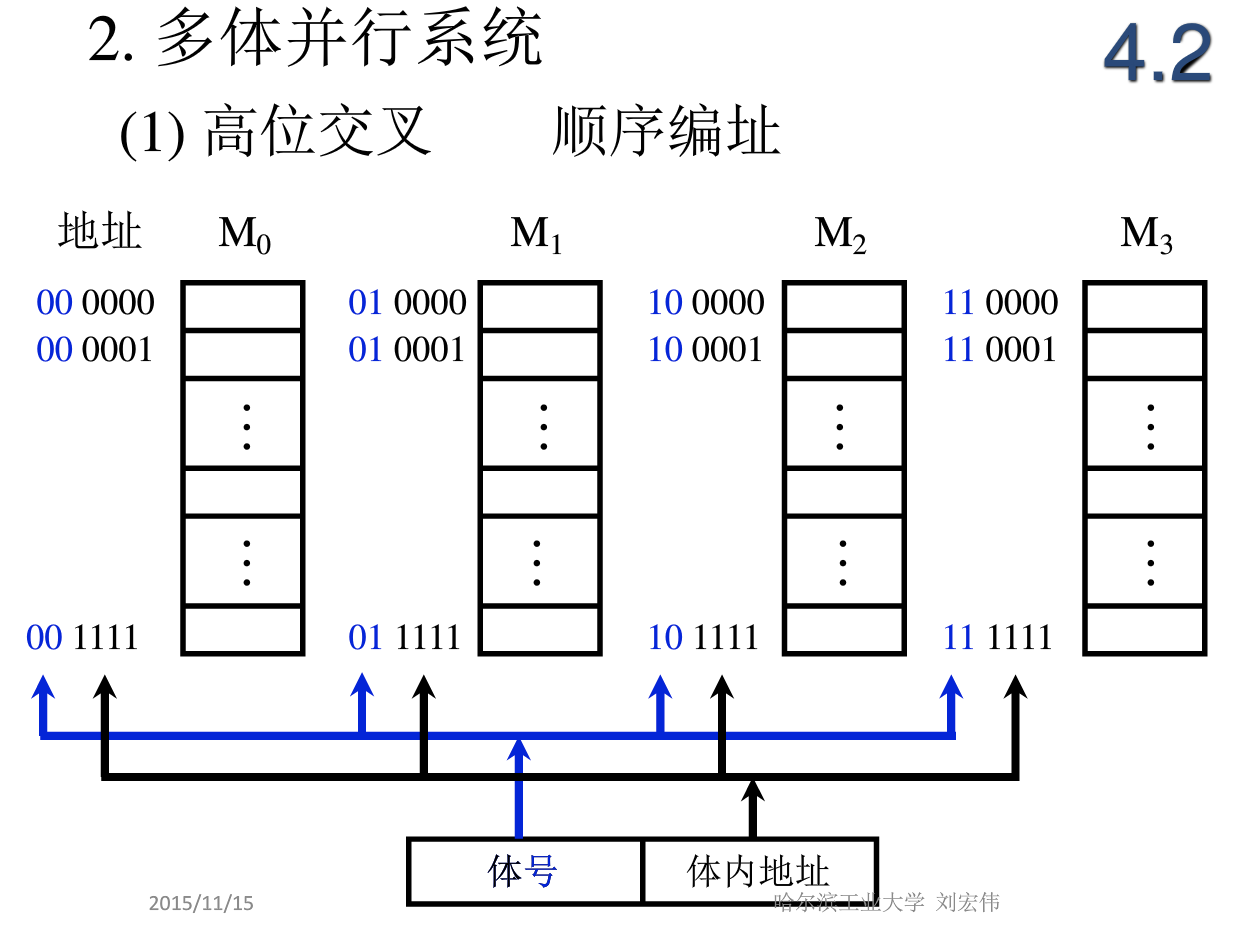

多体并行系统

高性能存储芯片

- SDRAM(同步DRAM)

- 在系统时钟的控制下进行读出和写入

- CPU无须等待

- RDRAM

- 有Rambus开发,主要解决 存储器带宽 问题

- 带Cache的DRAM

- 在DRAM的芯片内 集成 了一个由SRAM组成的Cache,有利于猝发式读取

浙公网安备 33010602011771号

浙公网安备 33010602011771号