锁相环学习---CD4046

介绍

cd4046主要用于调频(FM)信号的调制与解调,频率的合成,各种音频产生的领域。本博文主要介绍一下CD4046的一些基础配置还有基础用法,用2023年电赛H题为例子搭建(其实我也只会这个了QAQ),第一次学这个东西,如果有讲不到的东西,请见谅😶🌫️(所参考的资料还有自己所用的软件都丢到了后面的参考部分)

锁相环框图

下面是锁相环的最基本工作流程框图,信号输入到鉴频鉴相器(PD),然后流过环路滤波器(LP),然后控制压控振荡器(VCO)输出信号,无论是数字的还是模拟的,框图都是如此,只是各个部分的设计不一样,本博文从CD4046入手。

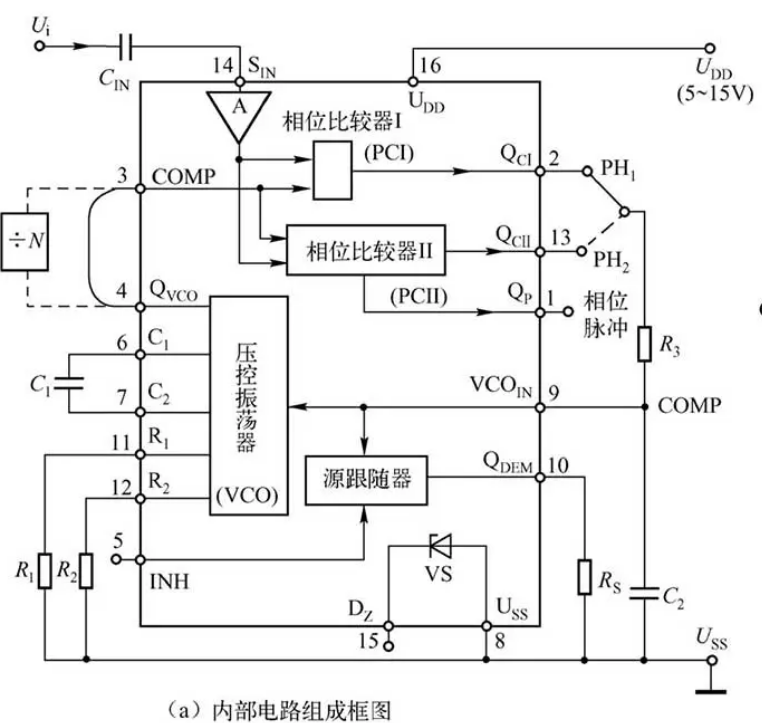

内部框图

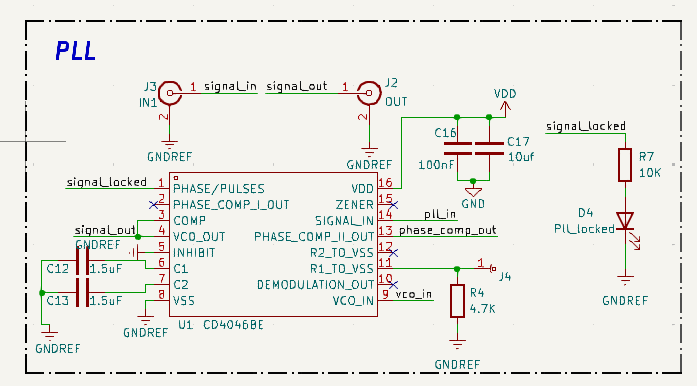

这个框图是手册最典型的电路设计图,内部主要是PD和VCO部分,设计的时候采用相位比较器Ⅱ(13引脚),这个比较准,输入的信号可以是正弦或者方波都可以锁定,这里要明确的就是锁相环锁定的是基频信号,剩下要注意的就在下面讨论好了,重点设计的部分也就是LP部分和VCO的配置。

引脚介绍

下面介绍一下关于引脚的配置,实际电路中不是所有的引脚都需要使用到,所以根据自身的要求选自己要使用的引脚就接线即可,具体的接线啥的,让我们继续往下看吧:D

| 引脚号 | 符号 | 功能 |

|---|---|---|

| 1 | Qp | 是相位比较器的锁定指示输出端,当电路进入锁定状态时,该脚输出高电平1,而在失锁时该脚输出低电平0(可以用作指示灯) |

| 2 | Q | 相位比较器PCⅠ的输出端 |

| 13 | QCⅡ | 相位比较器PCⅡ的输出端 |

| 3 | COMP | 比较输入端 |

| 4 | QVCO | VCO输出端 |

| 5 | INH | VCO的禁止端,该脚置高电平1时/悬空,VCO禁止工作;该脚置低电平0时,VCO工作 |

| 6 | C1 | 外接电容,作为内部震荡电容(用于确定固有震荡频率) |

| 7 | C2 | 外接电容,作为内部震荡电容(用于确定固有震荡频率) |

| 16 | VDD | 电源供电+5V/+15V |

| 8 | VSS | GND |

| 9 | VCOIN | 经过环路滤波之后输入控制VCO |

| 10 | QDEM | 为低通滤波后源极输出器的输出端 |

| 11 | R1 | 外接电阻,R1和C1决定 VCO的振荡频率 |

| 12 | R2 | 外接电阻,R2决定 VCO的最低振荡频率fmin,R2阻值减小时,fmin增大,频率范围会缩小 |

| 14 | SIN | 信号输入端,一般要求输入信号电压不小于100mv |

| 15 | DZ | 内部稳压二极管VDW的正电压输出端,为外电路提供稳压电源,稳压范围UZ=4.45~6.15V( IZ =50mA),一般为5.2V左右,在电路中需外接限流电阻 |

VCO的配置

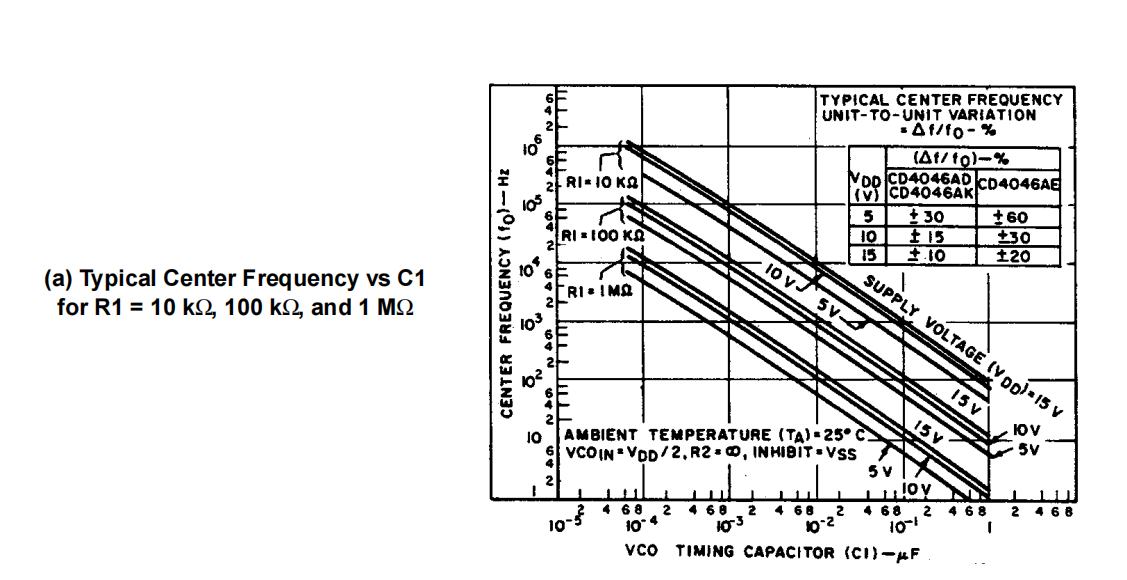

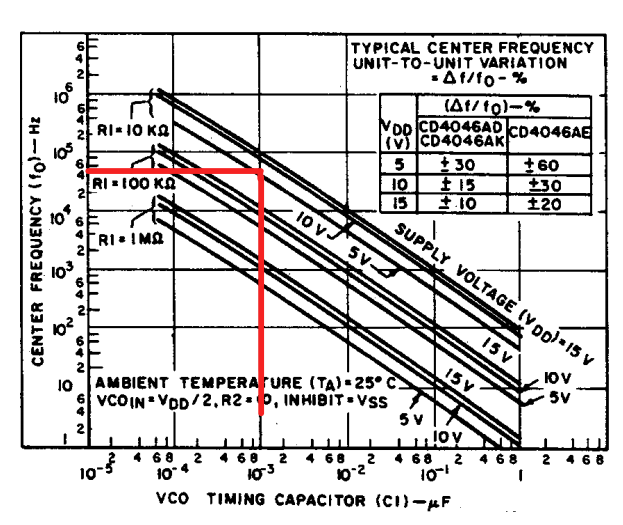

vco的配置是这款ic的重难点之一,是肥肠重要滴,重点注意的就是C1,C2和R1,这两个电容是vco的启震电容,与R1配合来确定锁相环的中心频率f0,下面的图就是关于C1与对应频率之间的关系。(截图来自ti官方的手册,放在下面的资料了)

其中横坐标是频率,看你设计的工作范围在哪里,对应选择,左边有个提示R1选择哪个,结合工作电压,看对应的曲线。但是实际中,我更喜欢用下面的方式来确定。

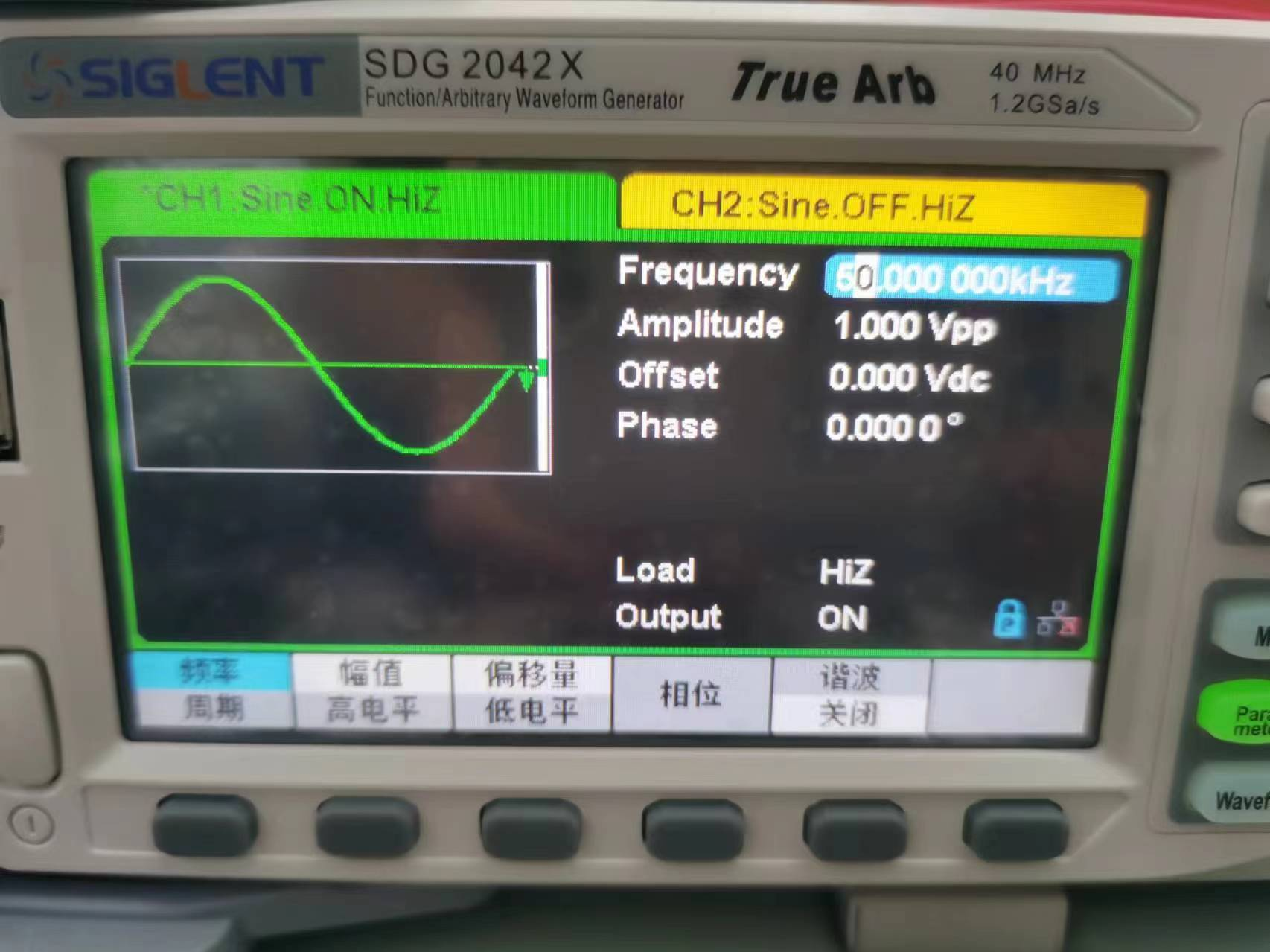

- 先确定自己的中心频率是多少(博主这边选取f0=50KHz,工作电压为5V,如下图红线所示)

- 确定C1和C2的大小(这两个电容是一样的,而且最好是同一个厂家的)

- 确定电容之后,用一个20K的电位器,替代R1(这里选20K是因为手册对应的是10K,所以建议从10K附近调节就好了)

- 将VCOIN(引脚9)接入2.5V的直流电压。

- 然后用示波器看 QVCO(引脚4)的波形,通过调节电位器,使得中心频率在50KHZ(这是我的设计!)

- 当调节到50KHz左右的时候(有点误差也行:D),然后断电,记录此时电位器是阻值

- 选一个固定的电阻,阻值和记录的阻值差不多即可,接入R1

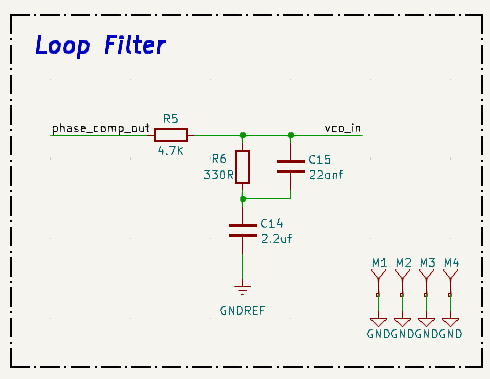

环路波器设计

这个环路滤波器的设计,就是重点的重点了,PD和VCO都集成在芯片里面,而环路滤波器就是外置的,也就是自己设计的部分,由于涉及了很多数学公式的推导,还有自控原理的知识(本人这部分学的不咋地QAQ),所以根据白白的小木鱼的教程,采用一款软件设计,计算公式和推导有兴趣的可以去参考一下《锁相环设计、仿真与应用(第五版)》

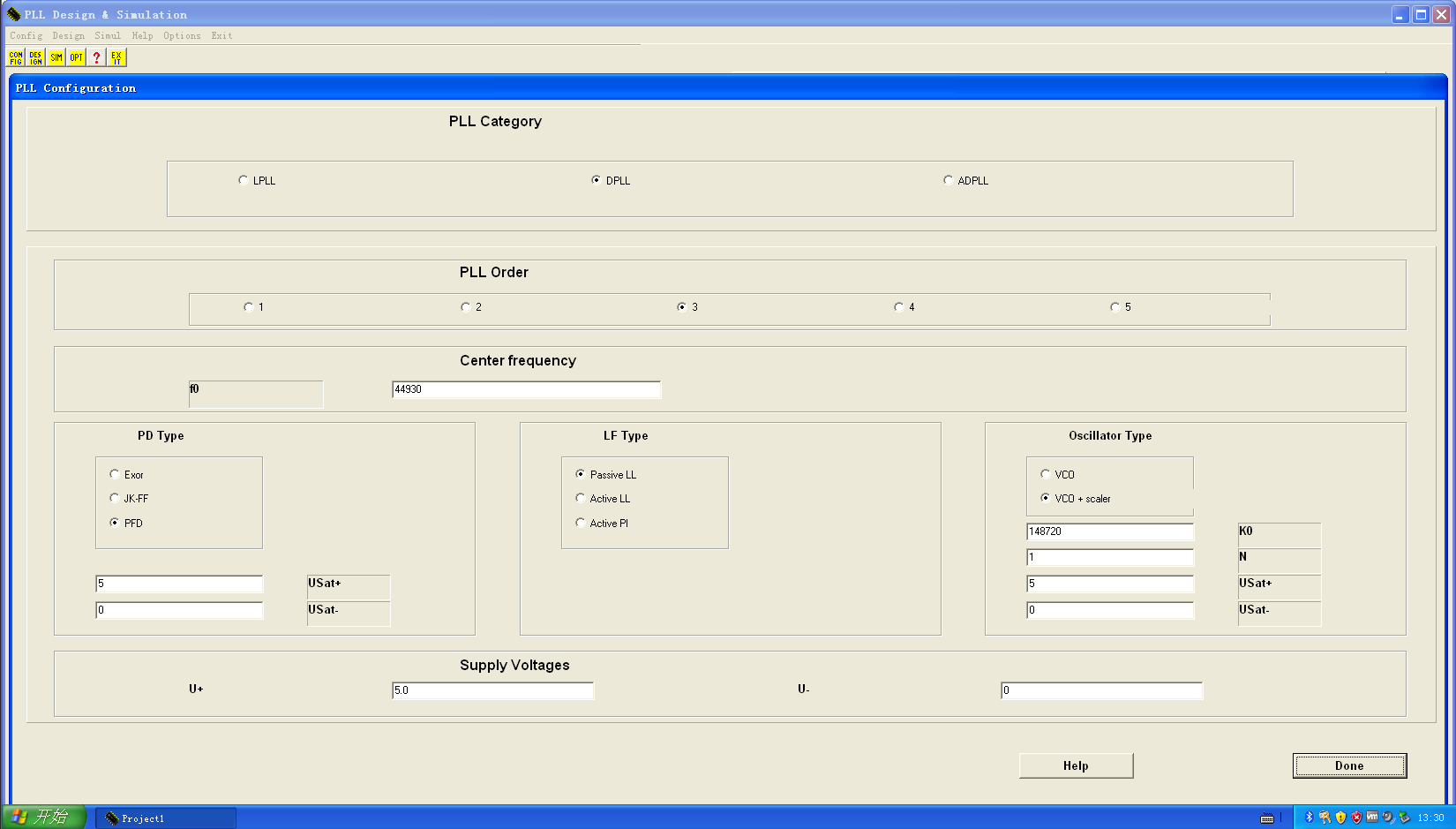

1.PLL Configuration

这个滤波器软件比较古老,得用虚拟机装一个XP系统在该系统之下设计,也是参考《锁相环设计、仿真与应用(第五版)》配套的软件设计。

安装打开之后就是上面的样子,一些的基础的配置我直接按照白白的小木鱼这个up来的,然后下面来重点关注一下两个参数。

- Center frequwency:这个就是中心频率f0,我建议根据实际测的中心频率填写就可以了

- K0:这个参数是环路的增益,计算公式是$k_0 = 2\pi f / U$,其中f就是输出的频率,U就是vco的控制电压

至于K0的测量,可以用扫频的方式,VCO的输入电压从5V递减到0.3V左右(看自己的情况),步长0.1V,记录电压与频率的对应数值,然后通过matlab或者excel表格做一个线性拟合,得到斜率,然后带入公式反解求出K0。

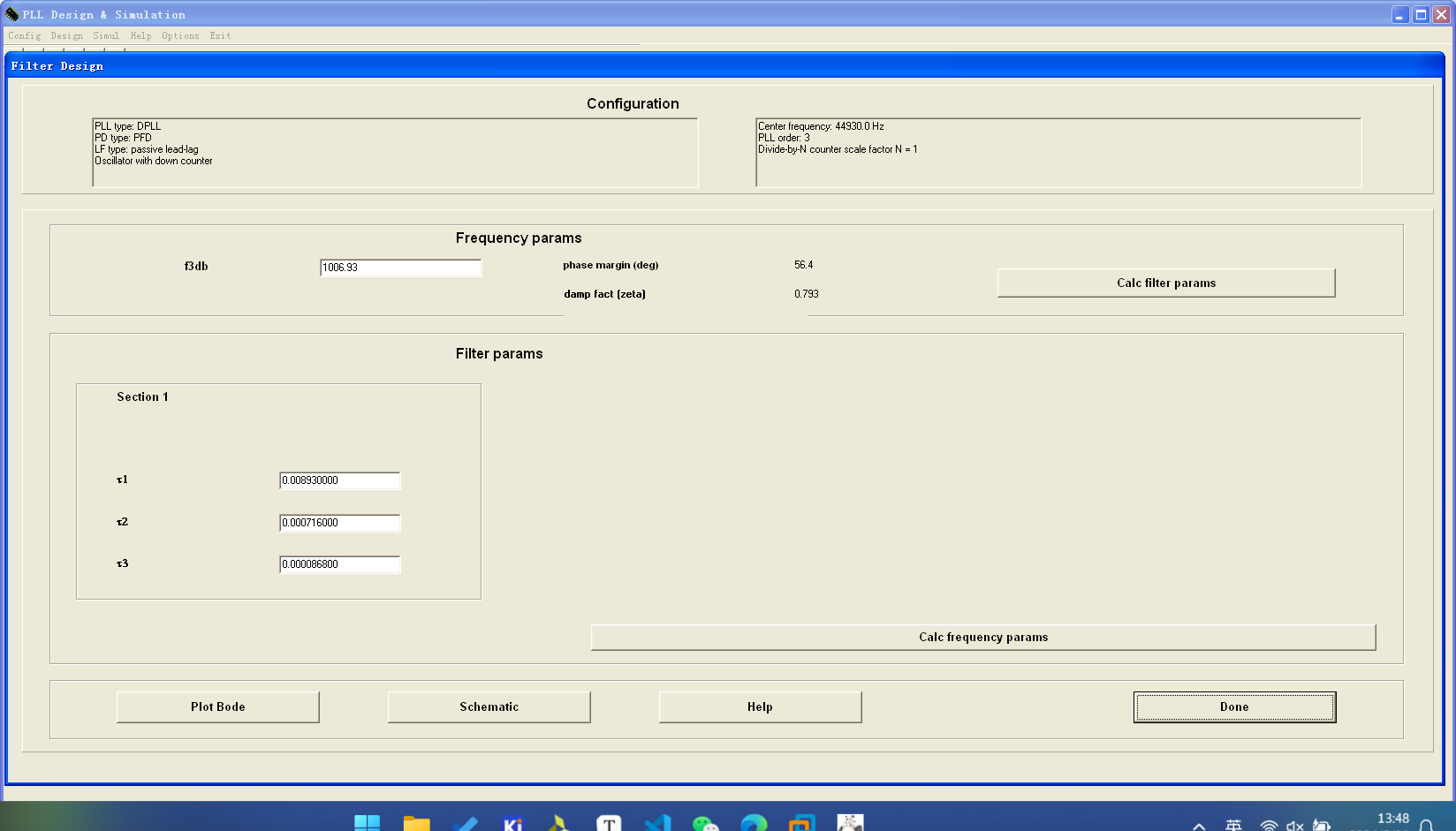

2.Filter Design

接下来是滤波器设计,上面是参数的设计,用于待会这个软件仿真使用。从下图中,也就是截止频率-3db的点,这里是我们要计算的,具体计算也是参考那本书,最后设计的要求就是相位裕度要在50°~ 70°左右,阻尼系数要在0.6~0.8之间,就尽量往这个结果调就没什么太大的问题了。

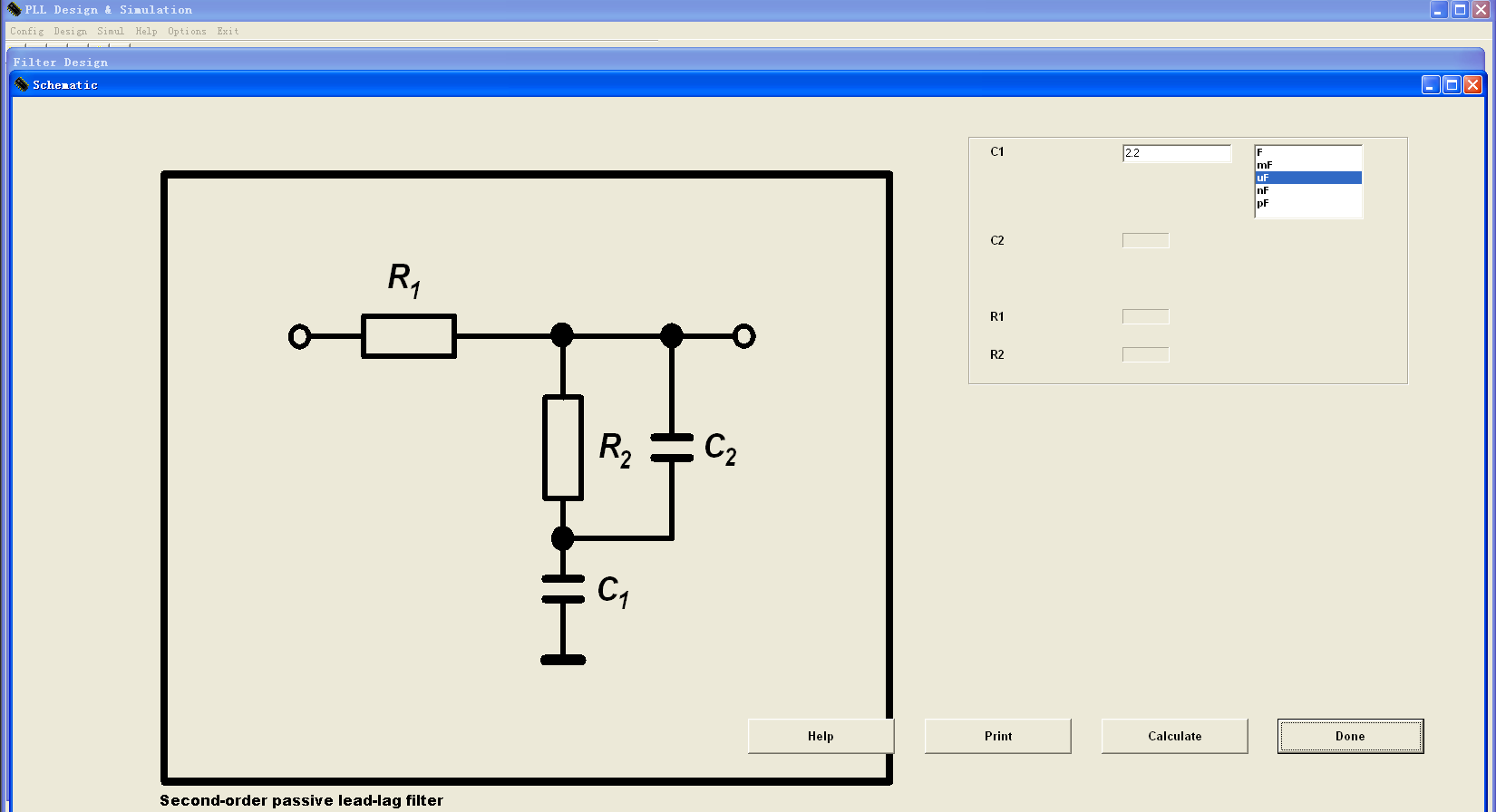

然后下面有一个Schematic这个按键,按完之后就弹出下面这个界面,也就是滤波器的拓扑结构图,一个超前滞后滤波器,然后确定C1的取值,点击Calculate就会自动帮你计算出符合设计的参数,然后就可以根据拓扑图进行搭建。

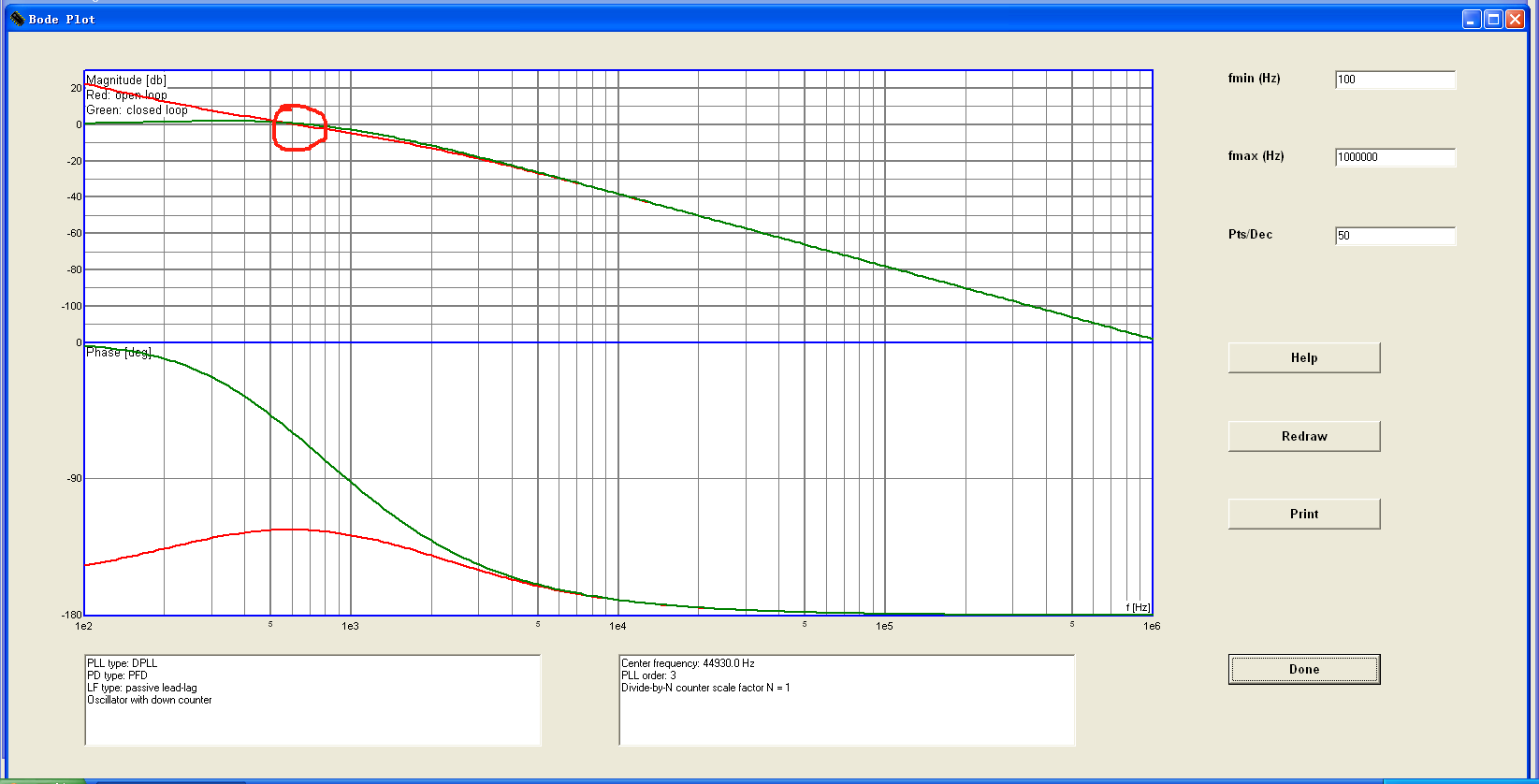

完成以上的设计之后,回到刚刚Filter Design界面,然后看到下面有一个Plot Bode,这是用来查看波特图的,如果自控学的比较好的就很容易明白是什么意思,如果跟我一样学的不咋地的,就看看红线和绿线是否如下图所示,并且交点正好就是设计的截止频率的点(后面得恶补一下自控了QAQ,这玩意真不好理解),旁边的参数是调整一些图形显示的比例的,没有什么太大的要求。

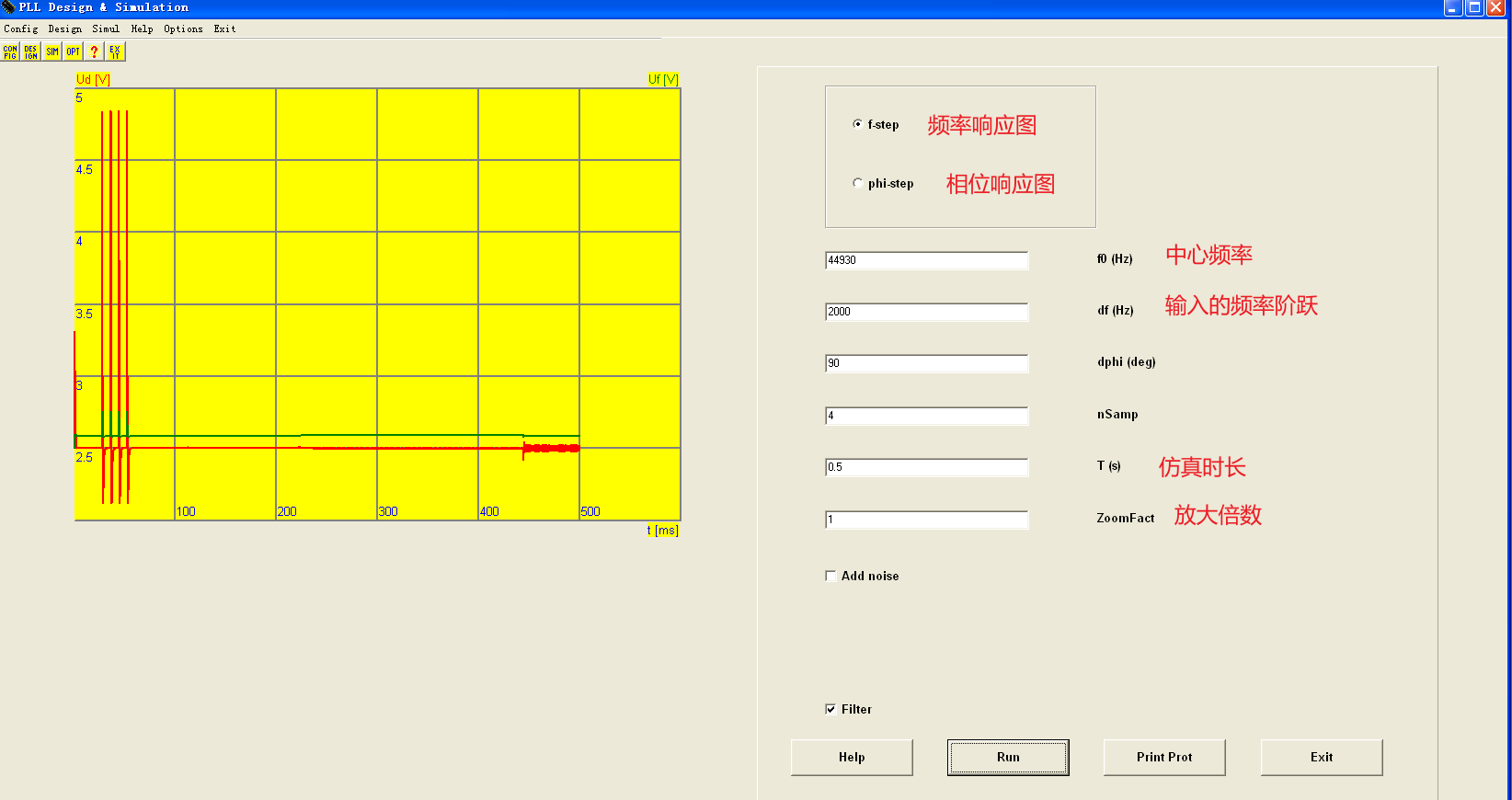

3.PLL simulation

接下来是看看设计的滤波器的频响图,看看设计的滤波器是否符合系统的稳定等参数(主要为了验证设计是否正确),部分博主觉得比较重要的已经做了标记,无论设计的如何,主要看仿真后面是否都如下图一样稳定了,稳定了说明已经锁住了,反之则需要重新设计一下滤波器,可能某些参数没有调好。

接线与实物展示

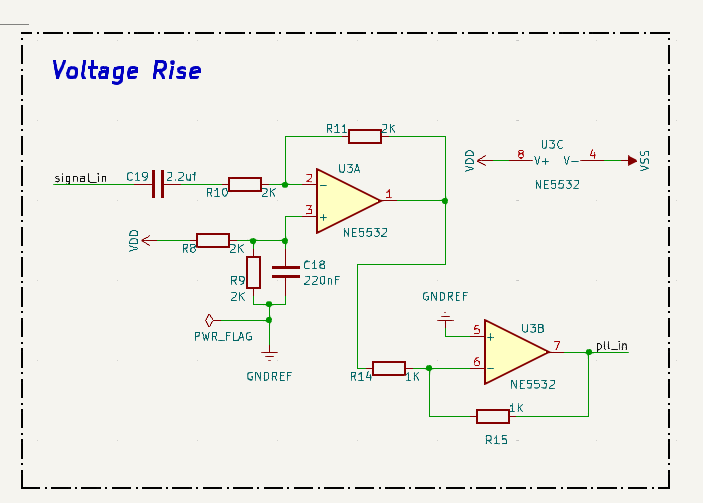

1.设计框图

这是我自己的想法,因为这个锁相环输入的要在2.5V的地方工作(实际测是这样的),然后峰峰值要大于100mv,然后输出的电压是5V的方波信号,考虑到单片机还有fpga等输入IO都是3.3V,为了防止损坏,就再设计一路降低幅值的电路(这里我直接用电阻分压的,没找到好的电路,如果频率高于200K,建议换其他方案)

2.原理图参考

3.实物测试

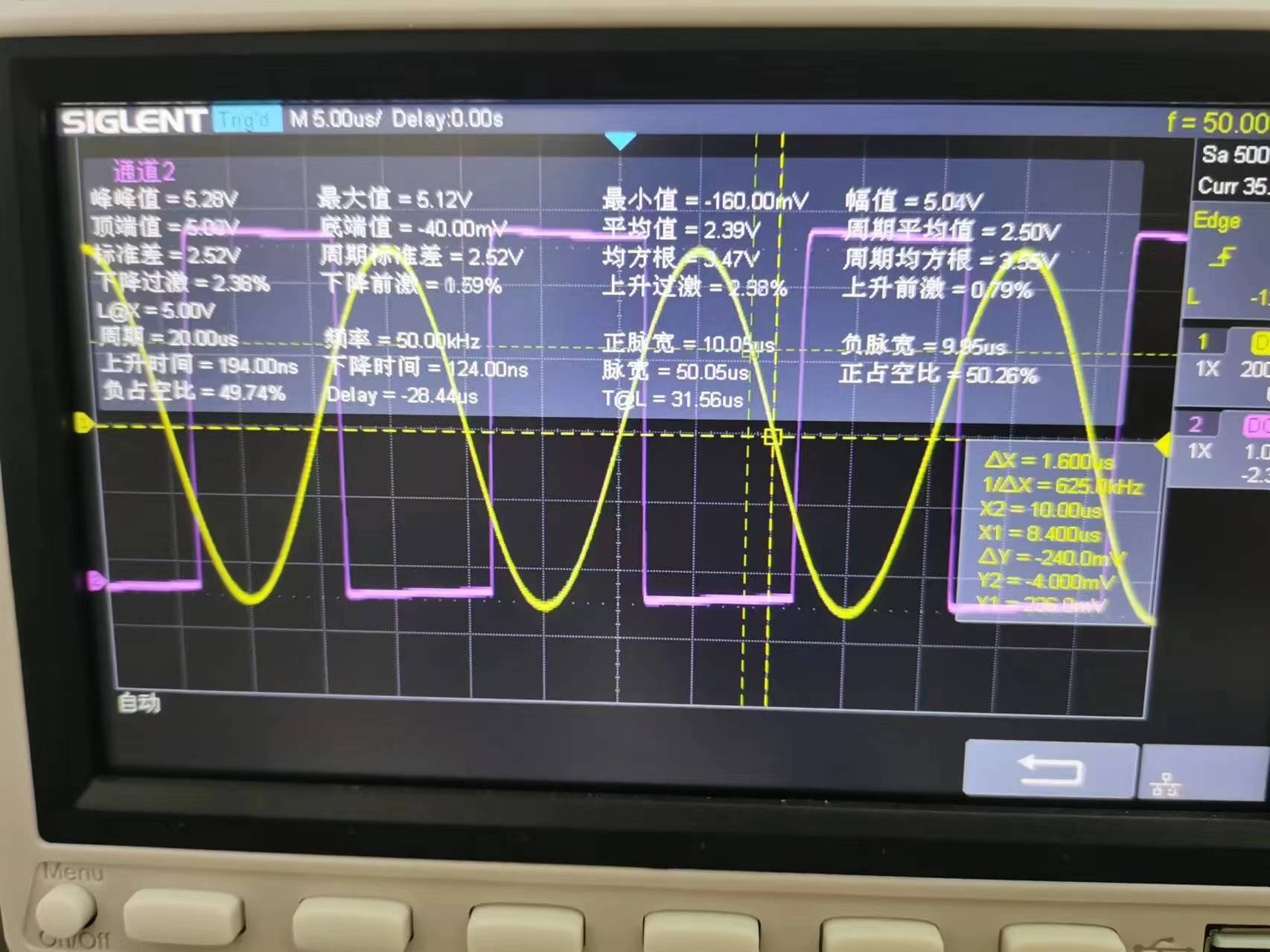

- 下面测试的是50KHz的正弦波形,示波器得出确实锁定了

|

|

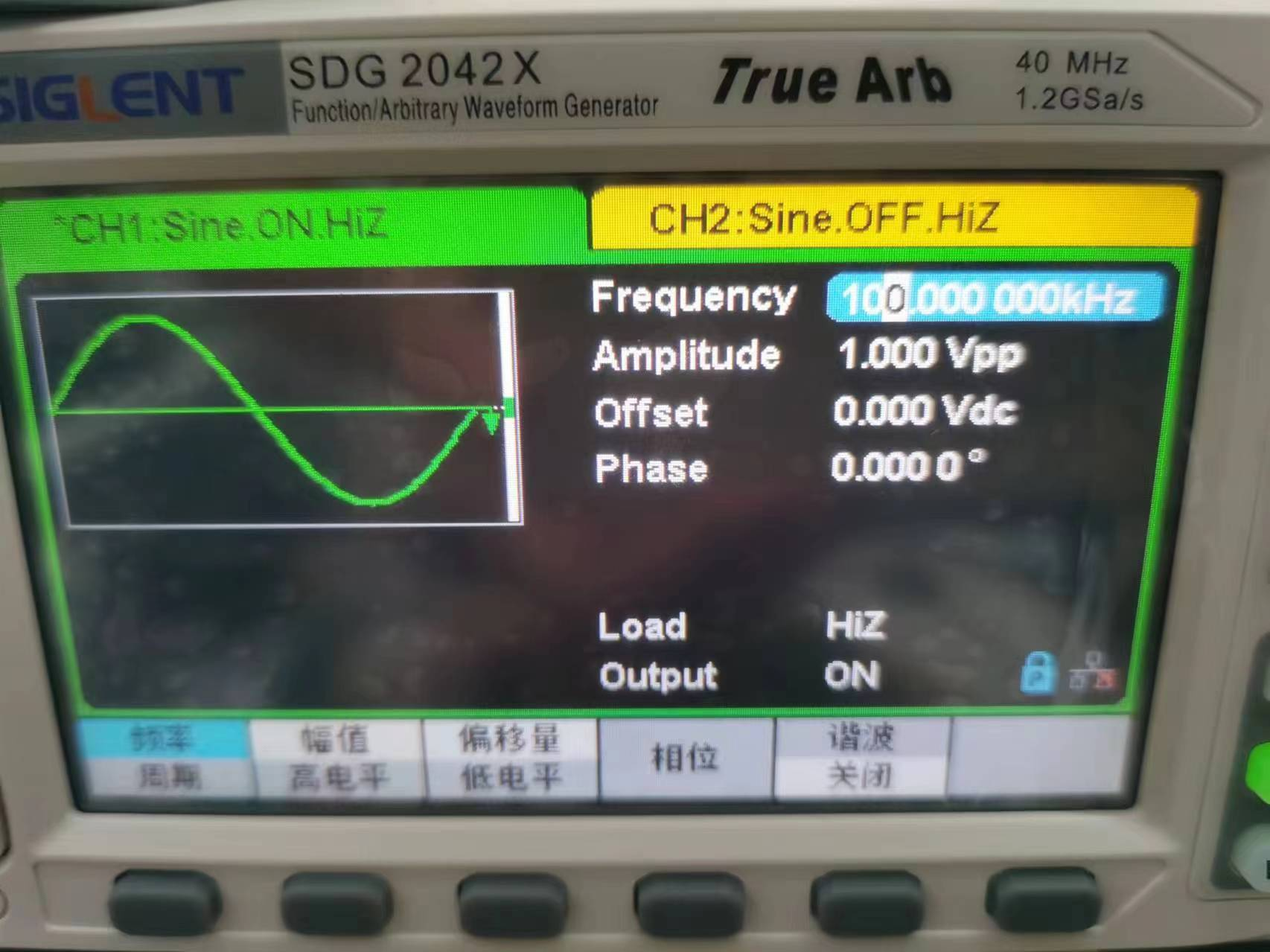

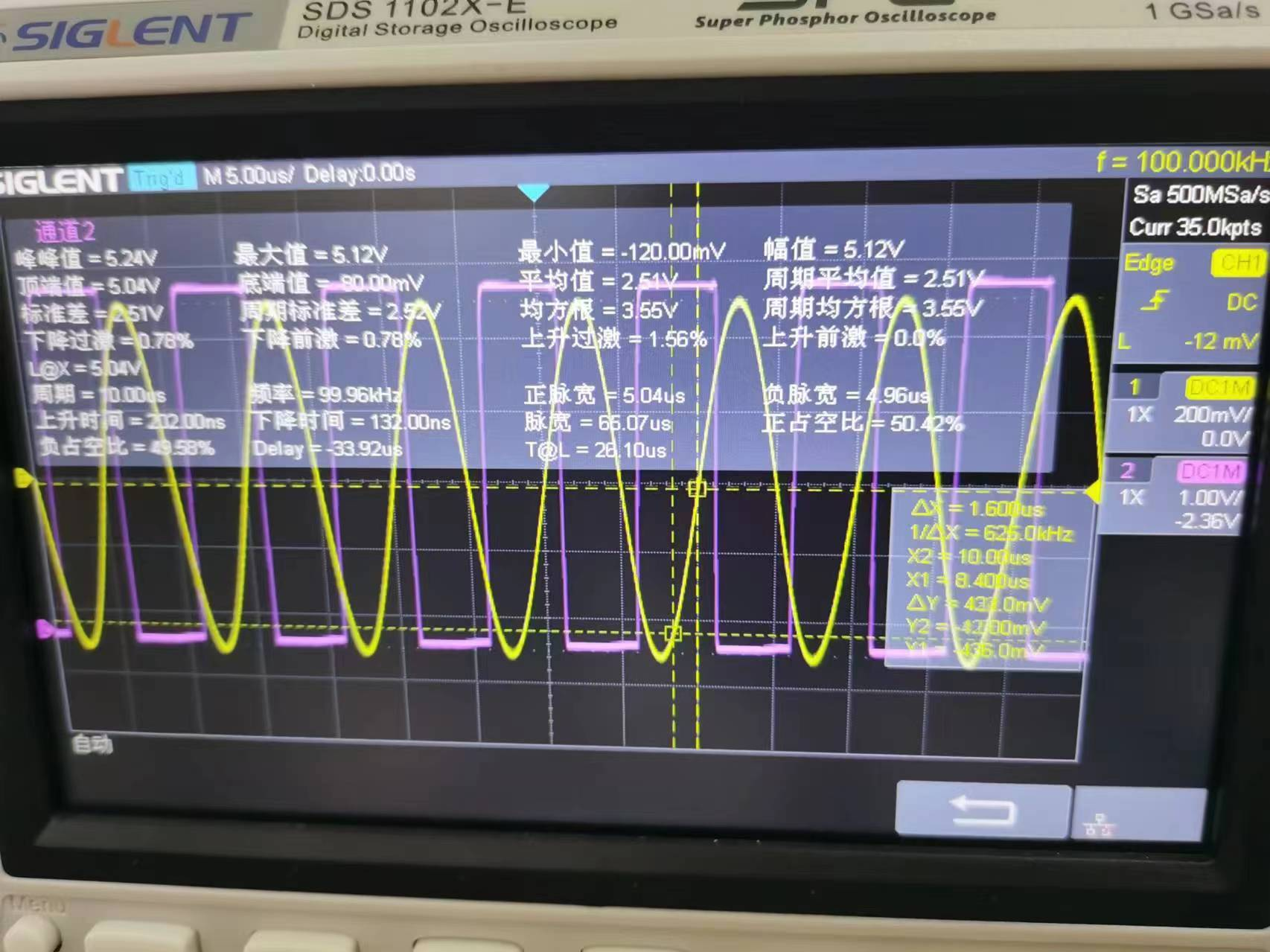

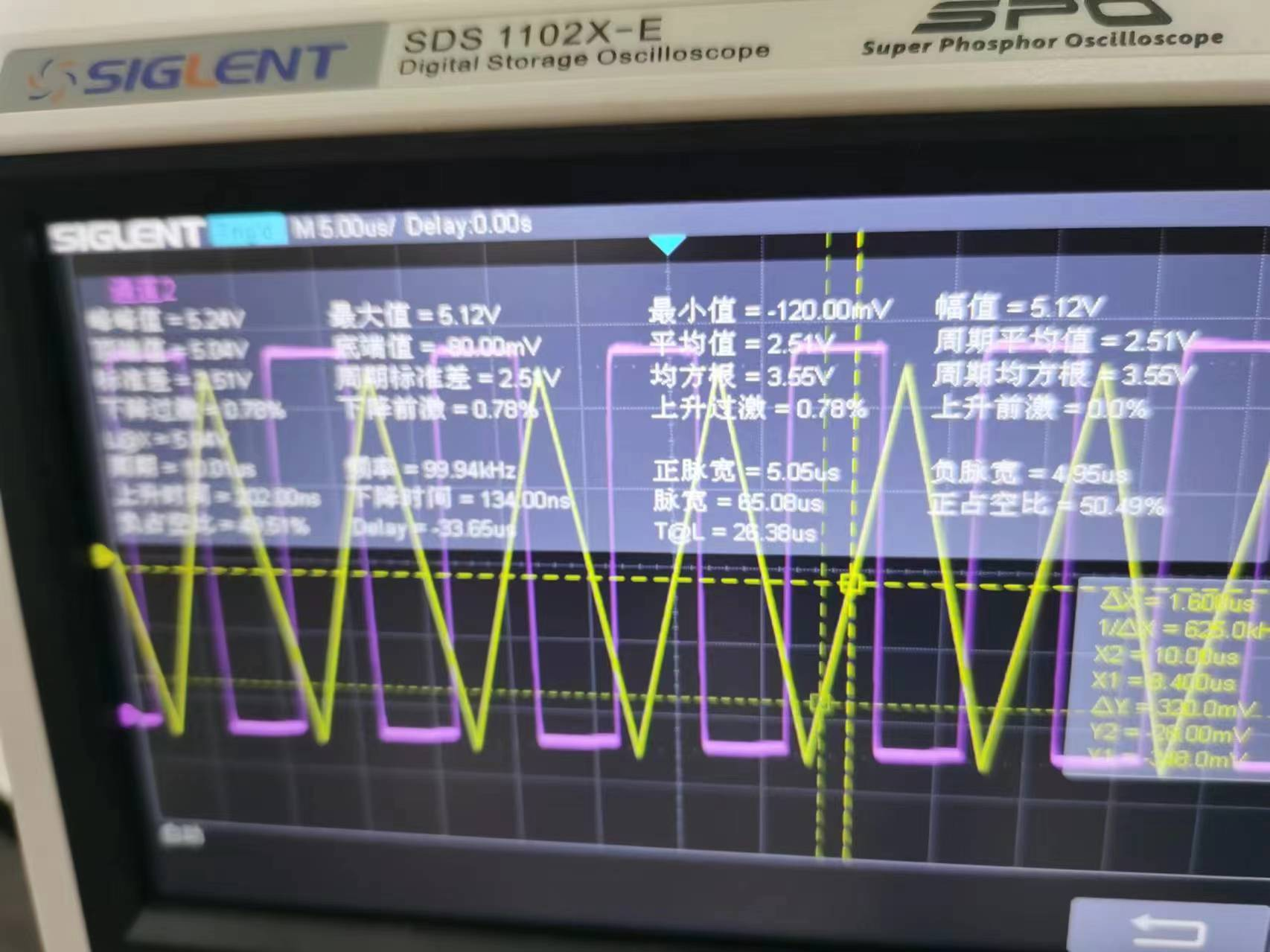

- 同理测试一下,100KHz是否可以锁定

|

|

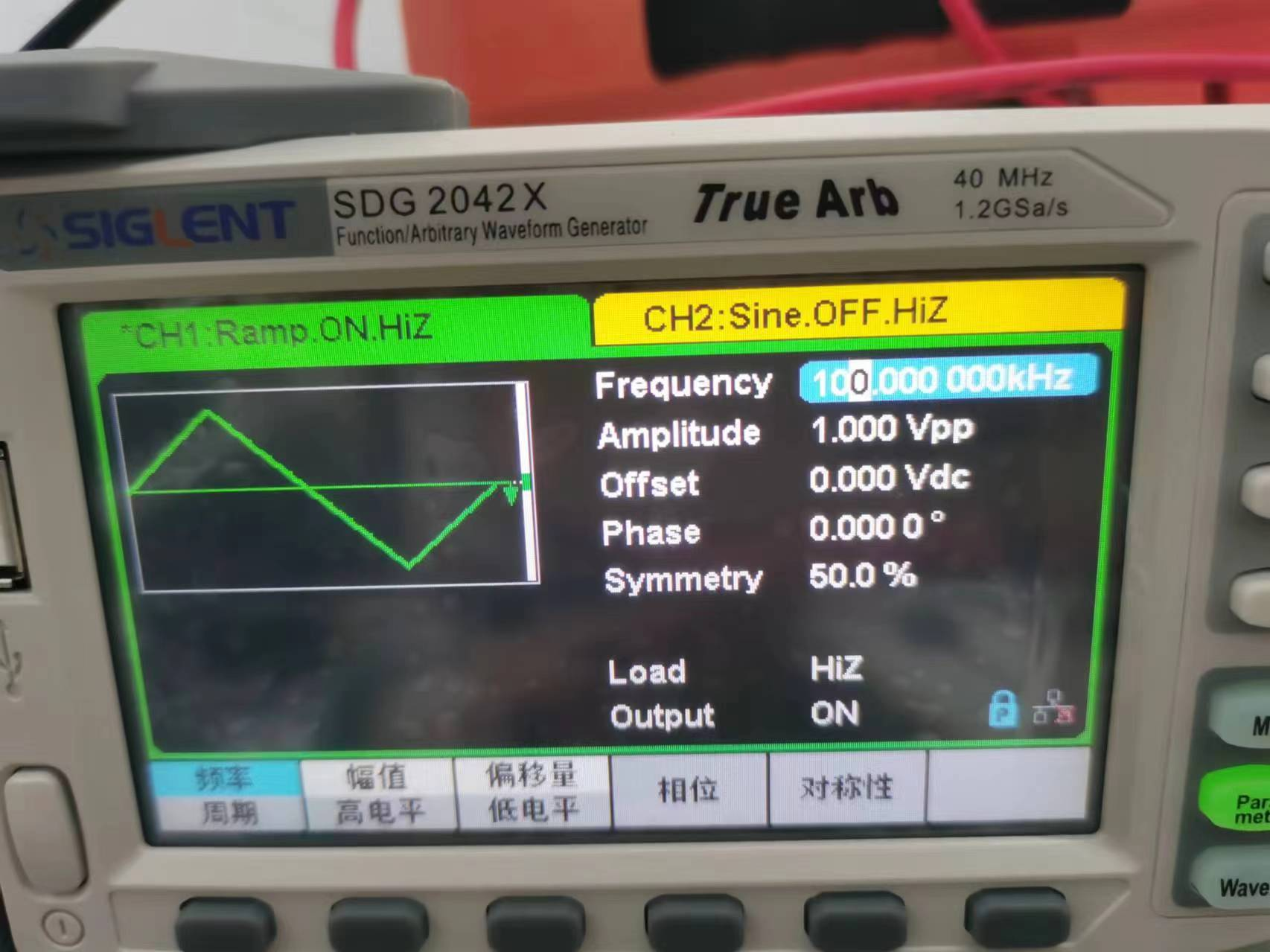

- 下面来测试一下三角波

|

|

通过以上测试可以得到对应的频率,说明锁相环没什么问题了,如果后面用的是单片机的IC捕获功能,那么直接将锁相环输出的信号接入输入捕获就可以了,但是如果是fpga的话,就得下降一下幅值,用两电阻分压就可以得到降幅的波形了,博主就不在这演示了