2. 基于MCU应用的EMC指南

1. 硬件

主要的噪声感受器和发生器是印刷电路板(PCB)上的轨道和布线,特别是MCU附近的轨道和布线。

因此,防止噪声问题的第一步行动涉及到PCB布局和电源设计。

一般来说,MCU周围的元器件数量越少,抗噪声性能越好。

例如,ROM-less解决方案通常比嵌入式存储电路对噪声更敏感,产生的噪声也更大。

1.1 优化PCB布局

噪声基本上是通过轨道和组件接收和传输的,一旦被激发,这些轨道和组件就像天线一样。

每个回路和轨道都包括寄生电感和电容,它们在电流、电压或电磁通量变化时辐射并吸收能量。

MCU芯片本身表现出对电磁干扰的高抗扰性和低产生率,因为它的尺寸相对于电磁干扰信号的波长较小(通常是毫米对GHz范围内的电磁干扰信号的10厘米)。

因此,单芯片解决方案与小回路和短电线减少噪音问题。

PCB层的初始行动是减少可能的天线数量。连接到单片机的回路和电线,如支持、振荡器和I/O,应特别注意。振荡器回路必须特别小,因为它在高频率下工作(图18)。

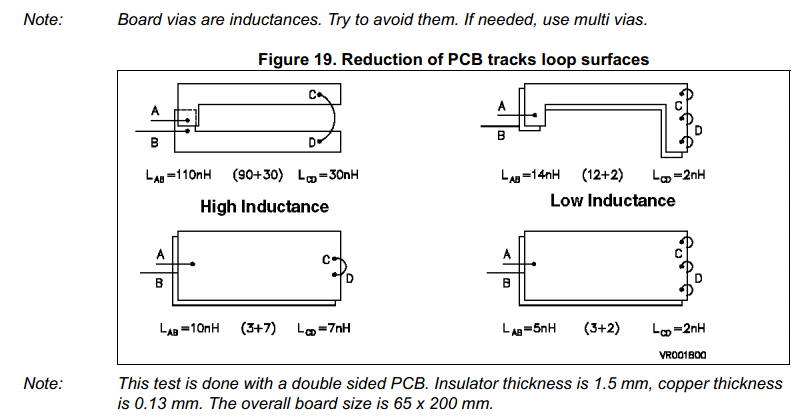

减小电感可以通过减小轨道的长度和表面来实现。这可以通过将轨道回路靠近同一PCB层或相互叠加来实现(图19)。产生的环路面积小,电磁场相互减小。

与电感值和线回路所限定的面积有关的数量级比值约为10 nH/cm2。低电感电线的典型例子是同轴、双绞线或具有一地一电源层的多层pcb。由于磁道的扩大或安装在电流流中的几个小电容的并联,磁道中的电流密度也可能更小。

在关键情况下,MCU和PCB之间的距离,因此MCU和它的环境之间的回路表面,也必须被最小化。

这可以通过去除MCU封装和PCB之间的任何插座,用塑料封装替换陶瓷MCU封装,或者使用表面安装代替双列直插封装来实现。

1.2 电源滤波

电路的各个部分都要用到电源,因此必须特别注意。

电源回路必须解耦,以确保信号电平和功率电流不相互干扰。

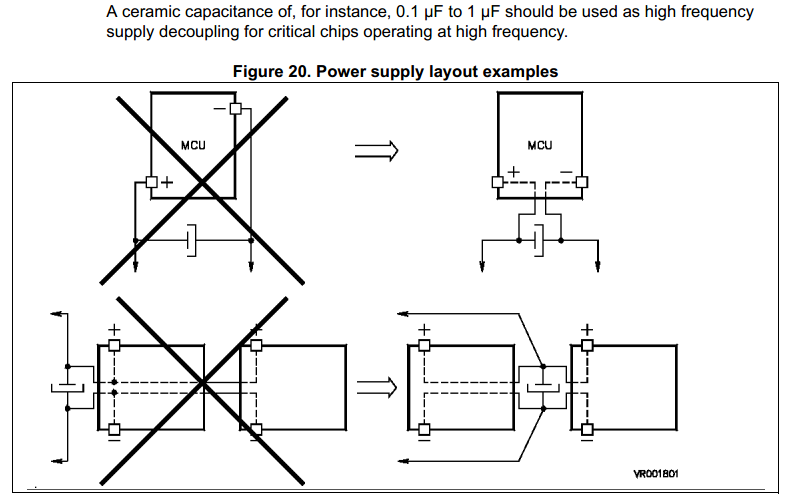

这些回路可以使用星型布线来分隔,其中一个节点指定为电路的公共节点(图20)。

解耦电容应该放置在非常靠近MCU电源引脚的位置,以最小化产生的环路。

它也应该足够大,在没有显著的电压增加的情况下,吸收通过输入保护二极管从MCU传入的寄生电流。

该板的解耦可以用电解电容器来完成(通常是10 µF to 100 µF),因为这种电容器中使用的电介质提供了一个高容量的电容。

然而,这些电容器在高频时表现得像电感(通常在10MHz 以上),而陶瓷或塑料电容器在较高频率时保持电容性行为。

1.3 接地

建议将所有VSS引脚通过最短的可能路径连接在一起,以减少在设备数据表中所述的绝对最大额定值以上的VSS引脚之间产生电压差的风险,由于电流是由外部干扰引起的,从而降低了接地回路的阻抗。

最好的做法是通过尽可能靠近设备VSS引脚的vias将VSS线连接到地平面。接地面应该是固体的,没有可能导致接地面阻抗增加的槽或孔。

不建议将模拟地和数字地分开。虽然它可能对从数字域到模拟域的噪声分布有可疑的影响,但它总是显示出较差的EMC性能。

1.4 I / O配置

一个开(浮动)引脚对电路是一个潜在的危险。

在应用程序中不使用的I/O引脚应该最好配置在输出低状态。这也将使当前的消耗最小化。

在基于微控制器的应用程序中,一个主要的发射源可能是由于高速数字I/O和通信接口,如SPI, I2C时钟,USB或PWM。涨跌时期是关键时期。典型的设计增加RC低通滤波器。

1.5 屏蔽

屏蔽有助于降低噪声感度和发射,但其成功与否直接取决于屏蔽材料的选择(高磁导率,低电阻率)和通过低串联阻抗(低电感,低电阻)与包括解耦电容在内的稳定电压源的连接。

如果发生重大干扰的发生器靠近MCU板,可以识别为强dV/dt发生器(即变压器或速调管),噪声主要由静电场携带。噪声发生器与控制板之间的临界耦合是电容耦合的。在控制板周围形成法拉第笼的高导电性屏蔽(如铜)可以大大提高免疫能力。

如果最强烈的扰动源是dI/dt发生器(即继电器),那么它是一个高电磁场源。因此,屏蔽材料(即合金)的渗透性对提高板的抗扰性至关重要。此外,应尽量减少屏蔽上的孔的数量和尺寸,以提高其效率。

在关键的情况下,在MCU下方植入接地面,去掉器件与PCB之间的插座,可以降低MCU的噪声灵敏度。实际上,这两个动作都导致MCU、电源、I/O和PCB之间环路的表面减少。