1. 内部管脚电路

0. 静电放电和闭锁

CMOS集成电路通常对暴露在高压静电下非常敏感,高压静电会对器件造成永久性损伤:典型的故障是薄氧化物击穿,导致高漏电流,有时还会短路。

闭锁是发生在集成电路中的另一个典型现象:寄生双极结构或硅控制整流器(SCR)不必要的打开,可能会过热并迅速损坏设备。

这些非有意的结构是由P和N区域组成的,它们作为寄生双极晶体管的发射极、基极和集电极:阱和衬底中硅的体积电阻在可控硅结构上起到电阻的作用。

施加低于VSS或高于VDD的电压,并且当电流水平能够在可控硅寄生电阻上产生电压降时,可控硅可能被打开;要关闭可控硅,必须从设备上取下电源。

1. 内部电路:数字IO

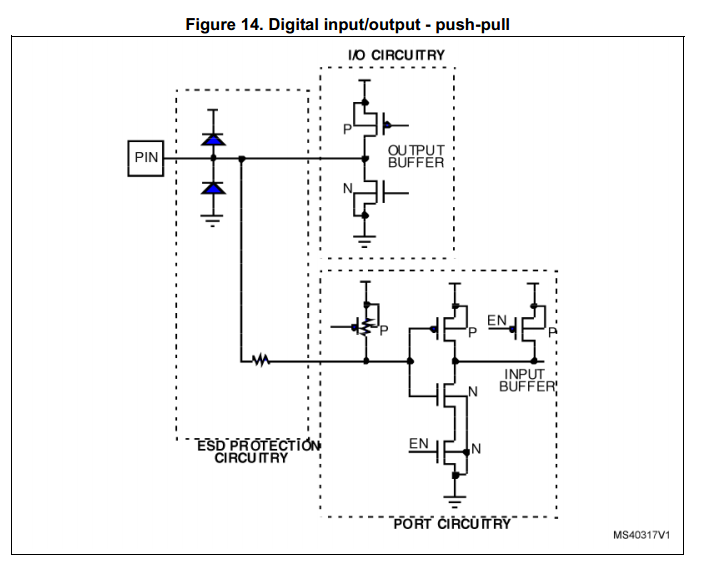

图14显示了既可以作为输入也可以作为输出操作的微控制器引脚的示意图表示。

电路实现了一个标准输入缓冲器和一个输出缓冲器的推挽配置。

很明显,当输入部分被使用时,虽然有可能禁用输出缓冲器,缓冲器本身的MOS晶体管仍然会影响引脚暴露在非法条件下的行为。

实际上,输出增益器的p通道晶体管实现了一个直接二极管到VDD(p扩散的漏极连接到引脚和n井连接到VDD),而输出缓冲的n通道实现一个二极管到VSS (p衬底连接到VSS和漏极的n扩散连接到引脚)。

在并联这些二极管中,实现专用电路以保护逻辑免受ESD事件(MOS、二极管和输入串联电阻)的影响。

这些额外器件最重要的特点是它们在暴露于超限条件下工作时,不能干扰正常工作模式,避免对逻辑电路造成永久性损坏。

根据所使用的MCU,一些I/O引脚可以编程也作为开路输出,只需写入相应的I/O端口寄存器。

输出缓冲器的p通道门被禁用:重要的是要强调物理上p通道晶体管仍然存在,所以二极管到VDD工作。

在某些应用中,可能会发生施加到引脚的电压高于VDD值(假设外接线保持高电平,而微控制器电源关闭):这种情况将通过二极管注入电流,对设备造成永久性损害的风险。

在任何情况下,当系统中的几个引脚被绑定到同一点时,将I/O引脚编程为开漏引脚会有帮助:当然,软件必须注意在任何时候只将其中一个引脚编程为输出,以避免输出驱动争用;

建议将这些引脚配置为输出漏极,以减少当前竞争的风险。

图15显示了一个真正的开漏引脚原理图。

在这种情况下,所有到VDD的路径都被删除(p通道驱动器,ESD保护二极管,内部弱上拉),以便允许系统关闭微控制器的电源,并保持电压水平在引脚高,而不注入电流在设备中。

这是一个典型的情况,当几个设备连接一个串行总线时可能发生:如果一个设备不参与通信,可以通过关闭它的电源来禁用它,以减少系统的电流消耗。

当一个非法的负电压水平被应用到微控制器I/O引脚(两个版本,推挽和真正的开漏输出)钳位二极管总是存在和有效(参阅ESD保护电路和n通道驱动器)。

2. 内部电路:模拟输入管脚

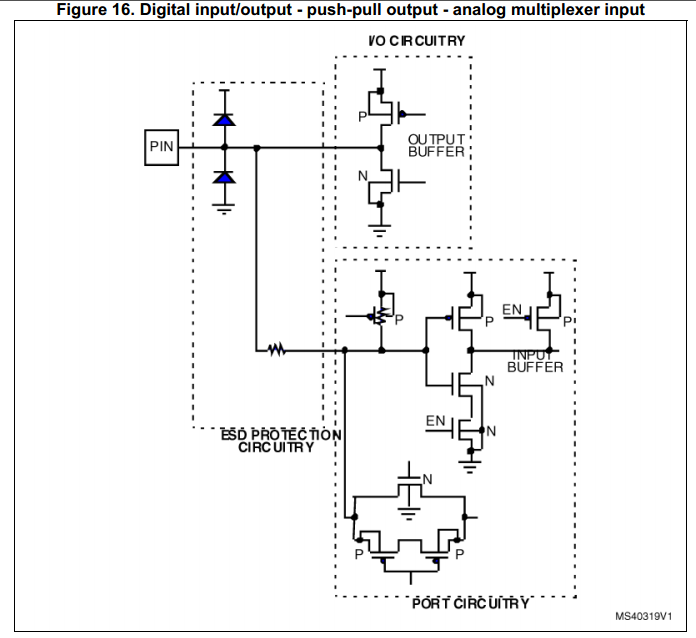

图16显示了用于模拟输入的内部电路。

它主要是一个数字I/O加上一个模拟多路复用器,用于选择模数转换器(ADC)的输入通道。

当暴露在非法电压条件下时,多路复用器p通道和n通道的存在会影响引脚的行为。

这些晶体管是由低噪声控制逻辑,偏置通过AVDD AVSS包括p沟道n阱:重要的是要始终验证输入电压值对模拟电源和数字电源,为了避免无意当前注射(如果不是有限的)可以破坏设备。