Cortex-M3基础

(一)寄存器

1 寄存器组

R0-R12: 通用寄存器

-----------------------------------------------------------------------------------------

R13: 堆栈寄存器

有两个,MSP和PSP,同时只能看见一个,引用R13时,引用的是正在使用的那个

MSP:可用于异常服务和应用程序

PSP:只能用于应用程序

系统复位后,用的堆栈指针是MSP。

------------------------------------------------------------------------------------------

R14: 连接寄存器,又名LR,存储返回地址

R15: 程序计数寄存器,又名PC

-------------------------------------------------------------------------------------------

2 特殊功能寄存器

程序状态字寄存器组(PSRs)

中断屏蔽寄存器组(PRIMASK, FAULTMASK, BASEPRI)

控制寄存器(CONTROL) *****☆

程序状态字寄存器组(PSRs)分为

应用程序 PSR(APSR)

中断号 PSR(IPSR)

执行 PSR(EPSR)

每个都是32位,由于这3个寄存器有效位是错开的,因此可以组合访问。

中断屏蔽寄存器组(PRIMASK, FAULTMASK, BASEPRI) ,这三个寄存器用于控制异常的使能和除能。

----------------------------------------------------------------------------------------

控制寄存器(CONTROL)它有两个作用:

1.定义特权级别

2.选择当前使用哪个堆栈指针

3.3 操作模式和特权极别

操作模式: 处理者模式和线程模式

异常处理:处理者模式

主程序:线程模式

对于ucosii,不区分特权级和用户级,程序始终工作在特权级

MSP、PSP两个堆栈指针的切换是全自动的,就在出入异常服务例程时由硬件处理。

-------------------------------------------------------------------

3.3.8 复位序列

0x00000000 MSP初值

0x00000004 PC 初值 复位向量

(二)异常

1 异常类型

分为系统异常(编号1-15)和外部中断(大于15)

2 优先级

CM3支持3个固定的高优先级和多达256级的可编程优先级。

----------------------------------------------------------------------------------------------------------

NVIC 中,每个中断都有一个优先级配置寄存器(1 个 byte) ,用来配置该中断的优先级。但该寄存器并不是每个位都被

使用,不同制造商生产的芯片不相同,譬如stm32使用 4位,也就是说stm32支持16个可编程优先级(参考:chapter9) 。

注意该寄存器是以MSB对齐的,因此stm32每个中断的优先级配置寄存器7:4位有效,3:0位无效。

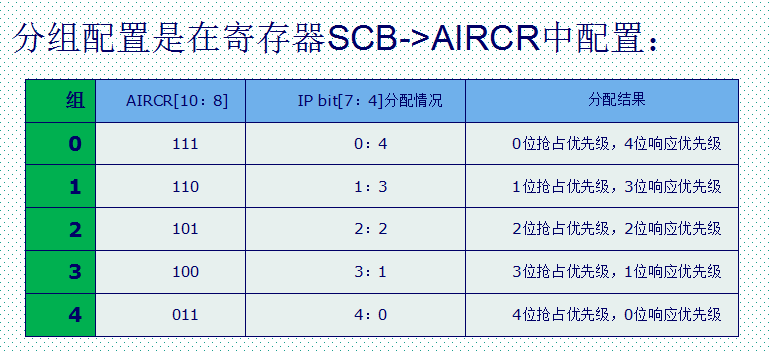

对于优先级, CM3又分为抢占优先级和亚优先级, NVIC中的应用程序中断及复位控制寄存器(AIRCR)的优先级分组(10:8)

描述了如何划分抢占优先级和亚优先级。

什么意思?以 stm32 为例,优先级配置寄存器不是 7:4 位有效吗,如果 AIRCR 中的优先级分组值为 4,则优先级配置寄

存器的7:5位确定抢占优先级,位4确定亚优先级。此时所有中断有8个抢占优先级,每个抢占优先级有2个亚优先级。

抢占优先级高的中断可以抢占抢占优先级低的中断,即抢占优先级决定了中断是否可以嵌套。

相同抢占优先级的中断不能嵌套,但当抢占优先级相同的异常有不止一个到来时,就优先响应亚优先级最高的异常。

参考附录D

表D.9 中断优先级寄存器阵列 0xE000_E400 - 0xE000_E4EF 共240个。

表D.16系统异常优先级寄存器 0xE000_ED18 - 0xE000_ED23 共12个。

优先级相同,看中断号,中断号小的优先。

3 向量表

初始在0x00000000处,可以通过向量表偏移量寄存器(VTOR)(地址:0xE000_ED08)更改,一般无需更改。

------------------------------------------------------------------------------------------------------

(三)SVC和PendSV

SVC

SVC主要用在分特权级和用户级的操作系统,ucosii不区分特权级和用户级,可以不管这个东西。

这里说点题外话,一开始我很奇怪为什么会提供这种中断,因为这种中断一般都是用在大型的操作系统上,如linux系

统上,可 CM3 又不提供 MMU,应该是无法移植 linux 系统。后来我才知道 uclinux 是针对没有 MMU 的嵌入式系统而设计的,

不过还是很怀疑有人会在像stm32这种芯片上用uclinux。

PendSV

PendSV中断主要做上下文切换,也就是任务切换,是ucosii移植过程中最重要的中断。

主要有两点:

1.PendSV中断是手工往NVIC 的PendSV悬起寄存器中写1 产生的(由OS 写) 。

2.PendSV中断优先级必须设为最低。

在讲移植代码时会介绍具体是如何做的。 对于7.6的PendSV部分应认真研读一下。

(四) NVIC 与中断控制

NVIC负责芯片的中断管理,它和CM3内核紧密相关。

(五)中断的具体行为

1 中断/异常的响应序列

当CM3开始响应一个中断时

1.xPSR, PC, LR, R12以及R3‐R0入栈

2.取向量

3.选择堆栈指针MSP/PSP,更新堆栈指针SP,更新连接寄存器LR,更新程序计数器PC

对移植ucosii 来说,需要注意1,3

2 异常返回

在CM3中,进入中断时,LR寄存器的值会被自动更新。9.6节对更新后的值进行说明。这里统称EXC_RETURN。返回时通

过把EXC_RETURN往PC里写来识别返回动作的。因为EXC_RETURN是一个特殊值,所以对于CM3,汇编语言就不需要类似reti

这种指令,而用 C 语言开发时,不需要特殊编译器命令指示一个函数为中断服务程序。实际上,中断服务程序如果是 c 代码

编写,汇编成汇编代码,函数结尾一般是reti。

3 嵌套的中断

只要注意:中断嵌套不能过深即可。

(六)Cortex-M3 的低层编程

汇编与C 的接口

有两点需要知道:

1.当主调函数需要传递参数(实参)时,它们使用R0‐R3。其中R0传递第一个,R1 传递第2个……在返回时,把返回

值写到R0中。

2.在函数中,用汇编写代码时,R0-R3, R12可以随便使用,而使用R4‐R11,则必须先PUSH(入栈),后POP(出栈)。

----

组别:0>1>2>3>4

组别优先顺序(第0组优先级最强,第4组优先级最弱):NVIC_PriorityGroup_0>NVIC_PriorityGroup_1>NVIC_PriorityGroup_2>NVIC_PriorityGroup_3>NVIC_PriorityGroup_4

及号越小优先级越高

-------

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0; // 指定响应优先级别1

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0; // 指定响

如上,NVIC_IRQChannelPreemptionPriority 和 NVIC_IRQChannelSubPriority 两个主要指什么呢?有什么区别,如我把两个中断的 // 指定响应优先级别都设置相同的.会不会冲突呢?

它们的值是越大优先级越高还是越小越高呢?

取值范围又是如何的?

能不能详细介绍下NVIC中断的设置吗?

但理解不清,如何才算是嵌套?stm32的中断设置优点突出在哪里?

STM32(Cortex-M3)中的优先级概念

STM32(Cortex-M3)中有两个优先级的概念——抢占式优先级和响应优先级,有人把响应优先级称作'亚优先级'或'副优先级',每个中断源都需要被指定这两种优先级。

具有高抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说高抢占式优先级的中断可以嵌套低抢占式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪一个。

既然每个中断源都需要被指定这两种优先级,就需要有相应的寄存器位记录每个中断的优先级;在Cortex-M3中定义了8个比特位用于设置中断源的优先级,这8个比特位可以有8种分配方式,如下:

所有8位用于指定响应优先级

最高1位用于指定抢占式优先级,最低7位用于指定响应优先级

最高2位用于指定抢占式优先级,最低6位用于指定响应优先级

最高3位用于指定抢占式优先级,最低5位用于指定响应优先级

最高4位用于指定抢占式优先级,最低4位用于指定响应优先级

最高5位用于指定抢占式优先级,最低3位用于指定响应优先级

最高6位用于指定抢占式优先级,最低2位用于指定响应优先级

最高7位用于指定抢占式优先级,最低1位用于指定响应优先级

这就是优先级分组的概念。

--------------------------------------------------------------------------------

Cortex-M3允许具有较少中断源时使用较少的寄存器位指定中断源的优先级,因此STM32把指定中断优先级的寄存器位减少到4位,这4个寄存器位的分组方式如下:

第0组:所有4位用于指定响应优先级

第1组:最高1位用于指定抢占式优先级,最低3位用于指定响应优先级

第2组:最高2位用于指定抢占式优先级,最低2位用于指定响应优先级

第3组:最高3位用于指定抢占式优先级,最低1位用于指定响应优先级

第4组:所有4位用于指定抢占式优先级

可以通过调用STM32的固件库中的函数NVIC_PriorityGroupConfig()选择使用哪种优先级分组方式,这个函数的参数有下列5种:

NVIC_PriorityGroup_0 => 选择第0组

NVIC_PriorityGroup_1 => 选择第1组

NVIC_PriorityGroup_2 => 选择第2组

NVIC_PriorityGroup_3 => 选择第3组

NVIC_PriorityGroup_4 => 选择第4组

接下来就是指定中断源的优先级,下面以一个简单的例子说明如何指定中断源的抢占式优先级和响应优先级:

// 选择使用优先级分组第1组

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);

// 使能EXTI0中断

NVIC_InitStructure.NVIC_IRQChannel = EXTI0_IRQChannel;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1; // 指定抢占式优先级别1

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0; // 指定响应优先级别0

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

// 使能EXTI9_5中断

NVIC_InitStructure.NVIC_IRQChannel = EXTI9_5_IRQChannel;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; // 指定抢占式优先级别0

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 1; // 指定响应优先级别1

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

--------------------------------------------------------------------------------

要注意的几点是:

1)如果指定的抢占式优先级别或响应优先级别超出了选定的优先级分组所限定的范围,将可能得到意想不到的结果;

2)抢占式优先级别相同的中断源之间没有嵌套关系;

3)如果某个中断源被指定为某个抢占式优先级别,又没有其它中断源处于同一个抢占式优先级别,则可以为这个中断源指定任意有效的响应优先级别。

大家交流一下吧..

可以通过调用STM32的固件库中的函数NVIC_PriorityGroupConfig()选择使用哪种优先级分组方式,这个函数的参数有下列5种:

NVIC_PriorityGroup_0 => 选择第0组

NVIC_PriorityGroup_1 => 选择第1组

NVIC_PriorityGroup_2 => 选择第2组

NVIC_PriorityGroup_3 => 选择第3组

NVIC_PriorityGroup_4 => 选择第4组\

要注意的几点是:

1)如果指定的抢占式优先级别或响应优先级别超出了选定的优先级分组所限定的范围,将可能得到意想不到的结果;

我想问下.这分组是如何的呢?怎才算超出,如分组是4,那么其NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority 值不能大于4吗?

```

应该不会吧? stm32中断源可有许多的哦~~~

第1组:最高1位用于指定抢占式优先级,最低3位用于指定响应优先级

第2组:最高2位用于指定抢占式优先级,最低2位用于指定响应优先级

第3组:最高3位用于指定抢占式优先级,最低1位用于指定响应优先级

第4组:所有4位用于指定抢占式优先级

由上面可知,当选择分组4时,所有4位用于指定抢占式优先级,四位二进制能表示的最大值是什么?请枫儿自已算.

它是用来设置中断优先级,与多少个中断无关.

在程序中合理按排中断优先级可以达到具有高抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说高抢占式优先级的中断可以嵌套低抢占式优先级的中断。

2*2*2*2=16

它是用来设置中断优先级,与多少个中断无关.

在程序中合理按排中断优先级可以达到具有高抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说高抢占式优先级的中断可以嵌套低抢占式优先级的中断。

这个我还想不明白.

优先级2正在处理事件,优先级3排队有事件处理,而优先级1这时有事件处理,等优先级1处理后,优先级2立即处理事件;这是响应优先。

优先级2正在处理事件,优先级3排队有事件处理,而优先级1这时有事件处理,等优先级2处理后,优先级3才处理事件;这是响应优先。

那本书很神级,不知道出纸板了没有

既然已经设置了先占优先级那么为什么还要再设置响应优先级,老是把这两个弄混。还有就是谁比较理解系统优先级介绍一下。

void NVIC_SystemHandlerPriorityConfig(u32 SystemHandler, u8

SystemHandlerPreemptionPriority, u8 SystemHandlerSubPriority) Handler 1 SystemHandler Handler SectionSystemHandler 2 SystemHandlerPreemptionPriority Handler SectionSystemHandlerPreemptionPriority 3 SystemHandlerSubPriority Handler SectionSystemHandlerSubPriority

SystemHandler Handler Table 308.

Table 308. SystemHandler

NVIC_ VectTab

SystemHandler_MemoryManage Handler 存储器管理

SystemHandler_BusFault Handler 总线错误

SystemHandler_UsageFault Handler 使用错误

SystemHandler_SVCall SVCall Handler SVCall

SystemHandler_DebugMonitor Handler 除错监控

SystemHandler_PSV PSV Handler PSV

SystemHandler_SysTick Handler 系统滴答时钟

提示:如果死循环那一个不设置,它的默义优先级别多少?

/* Enable the EXT5-9 Interrupt on PD.3 */

NVIC_InitStructure.NVIC_IRQChannel = EXTI9_5_IRQChannel;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0;

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 2;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

/* Enable the EXTI10-15 Interrupt on PD.3 */

NVIC_InitStructure.NVIC_IRQChannel = EXTI15_10_IRQChannel ;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1;

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 5;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪一个。

当两个中断源抢占式优先级不同时,当正在处理的中断的抢占式优先级比后来的低,则后来的中断将会打断前一个中断处理,先处理后来的抢占式优先级较高的中断。

抢占式优先级与响应优先级,抢占式优先级是用于占先即可以中断比它较低抢占式优先级的中断处理过程。而响应优先级只在两个或多个中断源到达时,中断响应时起作用。

因此我在13楼的描述是不正确的。

摘录

浙公网安备 33010602011771号

浙公网安备 33010602011771号