从信号完整性角度看电容应用与计算

从信号完整性的角度来看,电容在电子电路中具有关键的应用。电容是一种被用来存储电荷并在电路中传递电流的被动元件,它对信号完整性有着重要的影响。

1. 去耦电容的选择

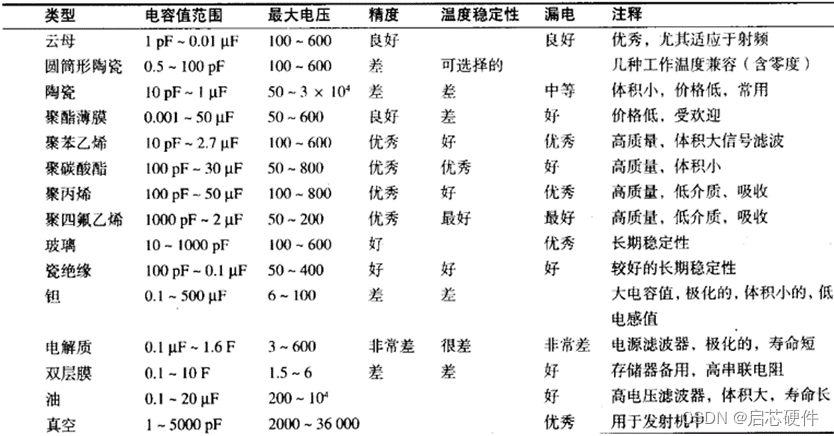

电容类型总结表格

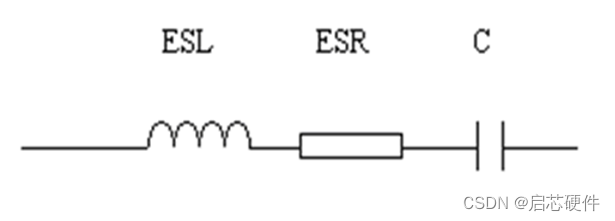

实际的电容并不是理想,表现为:

a.电容具有引脚电感,当频率高到一定的值后会使得电容的阻抗增加;

b.电容具有ESR,这也会降低电容的性能;

c.电容有温度特性,随着温度的改变,电容的介质属性会变化并引起容值的变化;

d.电容的容值会由于介质老化而慢慢变化;

e.电容过压会爆炸。

当选择去耦电容时,充分理解上述非理想性是很重要的,串联电感和ESR的影响可以计算得到,关于温度特性、老化特性和电压范围只能由生产厂家提供详细资料。

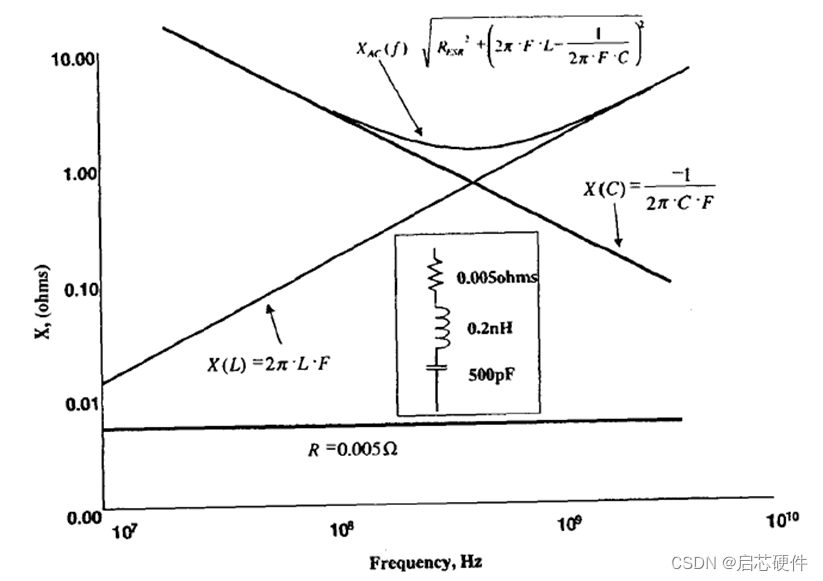

用等效交流阻抗来评估一个去耦电容的优劣,等效交流阻抗用电阻、电感和电容阻抗的均方根值来近似:ohms

其中:RESR:电容的串联电阻;Xac:电容的等效交流阻抗;L:电容管脚、封装、接插件电感的和。

下图所示的为一个电容的频响曲线。图中可以看出电容的带通特性(bandpass characteristics),低频段,电容表现为电容,当频率增加,电感成分占了上风,阻抗随频率增加而增加。

电容的阻抗很大程度上依赖于数字信号的频谱成分。因此,应该正确选择这一频率,可是在数字系统中因为信号包含很多频率成分,所以这一频率不是可以直接得到的。有一些方法可以得到旁路电容必须通过的最大频率。一些工程师简单的选择最大频率为基频的五次谐波,例如,如果总线的频率为500MHz,它的五次谐波为2500MHz。如果电容的引脚电感或ESR很高,那么可以另外选择电容或并联放置电容以降低等效电感和电阻。

主要的考虑因素及计算方法如下:

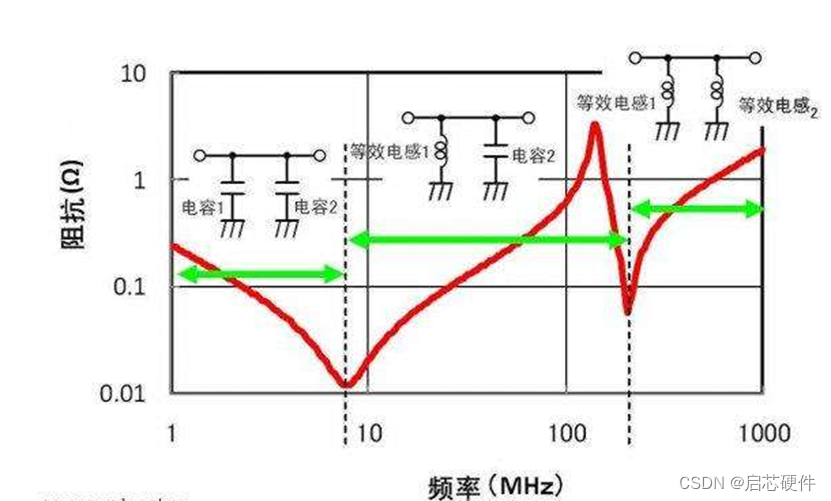

去耦电容的计算和应用:在高速数字电路中,去耦电容被用来消除电源和地平面之间的噪声,提供瞬态电流,并减少地弹。一般可以通过并联不同容值的电容来达到这个目的。

一种常见的计算方法是,首先根据目标阻抗确定所需的电容值。在高频电路中,可以使用更小、更多的电容,而在低频电路中则需要使用更大、更少的电容。

电容的ESL(等效串联电感)和ESR(等效串联电阻):这两个参数对于信号完整性有很大的影响。

ESL越小,电容的阻抗频率越高,因此更适合用于高频电路。

ESR越小,电容的低频性能越好。

电容的封装尺寸:封装尺寸会影响电容的ESL和ESR。

在高频电路中,通常选择封装尺寸较小、ESL较小的电容。

电容的电压和温度特性:不同的电容具有不同的电压和温度特性。

在选择电容时,需要考虑电路的工作电压和温度范围。

电容的稳定性:在某些应用中,需要使用稳定性好的电容,例如在电源滤波和信号耦合等应用中。

2. 去耦电容的去耦时间的计算

本文从另外一个更直观的角度来说明去耦电容的这种特性,即电容的去耦时间。稳压电源以及去耦电容是构成电源系统的两个重要部分。对于,现在芯片的速度越来越快,尤其对于高速处理芯片,负载芯片的电流需求变化也是非常快。内部晶体管开关速度极快。

例如,处理芯片内部有2000个晶体管同时发生状态翻转,转换时间是1ns,总电流需求为600mA。

这就意味着,电源系统必须再1ns时间内补足600mA瞬态电流。但是,对于目前的稳压源系统来说,在这么短的时间内并不能反应过来,相对于快速变化的电流,稳压源明显滞后了。根据一般经验来说,稳压源的频率响应为几百K左右,因为在时域系统里,1/100KHz=10us,也就是说,稳压源最快的响应时间为10us,无法在1ns时间里得到响应。这样的后果是,负载还在嗷嗷待哺等待电流,稳压源却无法及时提供电流,总功率一定,电流增大了,于是电压就会被拉下来,造成了轨道塌陷,因此噪声就产生了。

如何解决呢?方法是并联不同容值的电容器。因为,稳压源需要10us才能反应过来,所以在0-10us的时间里也不能干等着,需要用恰当的电容来补充。比如按照50mohm的目标阻抗,可以计算出电容:

C=1/(2PIfZ)=31.831uf

而电容的最高频率同时可以计算出来,假设ESL为5nH,所以有f=Z/(2PI*ESL)=1.6MHz。

也就是说加入31.831uf的电容,可以提供100KHz到1.6MHz频段的去耦。另外,1/1.6MHz=0.625us,这样一来,0.625us到10us这段时间电容能够提供所需要的电流。10us之后,稳压源能够提高需要的稳定电流。

另外,加上一个大电容并不能满足要求,通常还会放一些小电容,例如15个0.22uf的电容,可以提供高至100MHz的去耦,这些小电容的最快反应时间是1/100MHz=1ns,因此,这些电流能够保证1us之后的电流需求。

此外,这个反应时间可能还不太够,一般需要将退耦频率提高到500MHz,也就是反应时间快到200ps,应该就安全了。计算方法,同上,不再赘述。感兴趣的可以了解一些,目标阻抗的计算,很有意思。

总结,从信号完整性的角度电容主要应用以下几个方面:

去耦电容(Decoupling Capacitors): 电子设备通常包括大量的数字和模拟电路,它们共享电源线路。快速的数字电路可能会引起电源线上的噪声和波动。

去耦电容位于电源线和地之间,用于吸收和平滑这些噪声。

正确选择和布置去耦电容对于维持电源稳定性和减少信号干扰至关重要。

滤波电容(Filtering Capacitors): 在模拟电路中,电容经常用作滤波器的一部分,用于降低或去除信号中的高频噪声。

这对于保持模拟信号的质量非常重要,特别是在音频、通信和传感器应用中。

传输线匹配(Transmission Line Matching): 在高速数字电路中,信号完整性涉及到确保信号在传输线上以恒定的速度传播。

电容可以用于匹配传输线的阻抗,以减小信号反射和波形失真,从而提高信号完整性。

时钟电容(Clock Decoupling Capacitors): 在数字系统中,时钟信号的稳定性和准确性对于整个系统的操作至关重要。电容可以用来去耦时钟信号,确保它们不受电源波动的影响,从而保持时钟的稳定性。

信号耦合(Signal Coupling): 电容还可以用于实现信号耦合,将信号从一个电路传递到另一个电路,而不直接连接它们。

这有助于隔离不同电路中的信号,防止相互干扰。

浙公网安备 33010602011771号

浙公网安备 33010602011771号