Advanced FPGA Design Architecture,Implementation and Optimization学习之高速度结构设计

1.1 High Throughput

拆开一个迭代环路会增加数据吞吐量,带来的代价是面积成比例的增加。通常,如果要求n次迭代环路的算法拆开后,流水线实现将呈n倍的流量性能(throughput performance)增加。

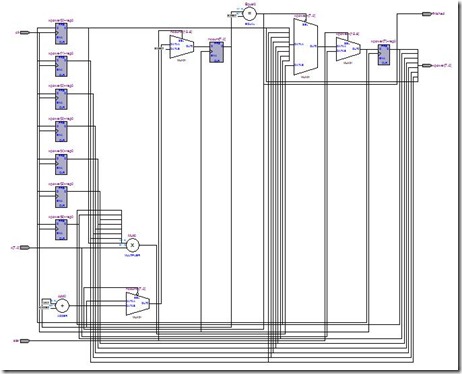

迭代算法

EXP1

module power3 ( input [7:0] x, input clk, input start, output reg [7:0] xpower, output finished ); reg [7:0] ncount; assign finished = (ncount == 8'd0); always @ (posedge clk) if(start) begin xpower <= x; ncount <= 8'd2; end else if(!finished) begin ncount <= ncount - 8'd1; xpower <= xpower *x; end endmodule

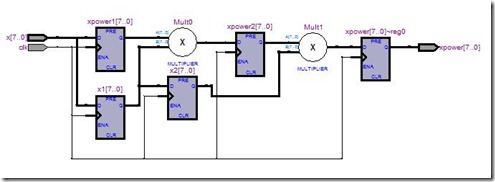

流水线算法

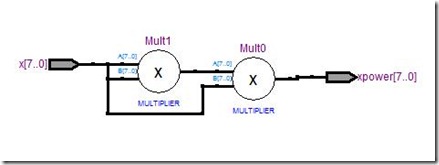

EXP2

module power3 ( output reg [7:0] xpower, input clk, input [7:0] x ); reg [7:0] xpower1,xpower2; reg [7:0] x1,x2; always @ (posedge clk) begin x1 <= x; xpower1 <= x; x2 <= x1; xpower2 <= xpower1*x1; xpower <= xpower2*x2; end endmodule

1.2 低时滞

低时滞设计是通过最小化中间处理过程的延时,来尽量快速地把数据从输入端传递到输出端的设计。通常,低时滞设计将要求并行性、去除流水线、缩短逻辑,可能减少设计中的流量或者降低最大时钟速度。

EXP1没有对迭代实现进行明显的时滞优化,因为每个接连的哦乘法器操作必须为下一步操作进行寄存。但是,EXP2的流水线实现有明显的路径来减少时滞。注意每个流水线级,每个乘法的积必须等待下一个时钟沿到来才传递到下一级。去除流水线寄存器可以使输入到输出的时序最小化。

EXP3

module power3 ( output [7:0] xpower, input [7:0] x ); reg [7:0] xpower1,xpower2; reg [7:0] x1,x2; assign xpower = xpower2*x2; always @ * begin x1 = x; xpower1 = x; end always @ * begin x2 = x1; xpower2 = xpower1*x1; end endmodule

可以通过移去流水线寄存器来减少时滞;相应的,带来的损失是增加寄存器之间的组合延时。

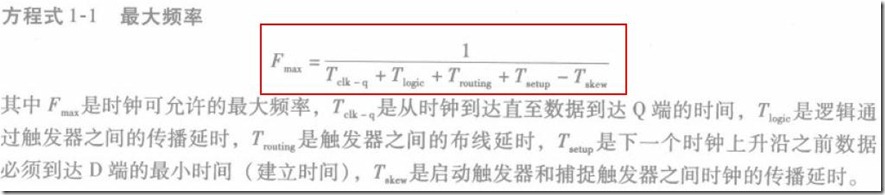

1.3 时序

时序是指一个设计的时钟速度,在设计中任何两个时序元件之间的最大延时将决定最大的时钟速度。

时序改进策略

1.添加中间的寄存器层次到关键路径,这个技术应该利用在高度流水线的设计,附加的时钟周期的时滞不违反设计的技术条件,整个功能将不受进一步增加的寄存器的影响。

把关键路径分成两个更小延时的路径,添加寄存器层次改进时序

2.重新组织关键路径,以致并行地实现逻辑结构,当通过一列串行的逻辑估值的一个函数可以分解和并行的估值时,就可以利用这个技术。

把一个逻辑功能分成大量可以并行估值的更小的功能,减少路径延时为子结构的最长延时。

3.展平逻辑结构,专门可以应用于因为特权编码而链接的逻辑。

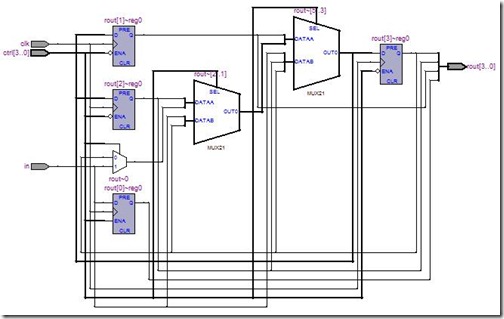

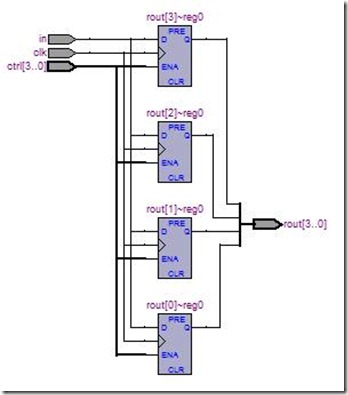

EXP4

module regwrite ( output reg [3:0] rout, input clk,in, input [3:0] ctrl ); always @ (posedge clk) if(ctrl[0]) rout[0] <= in; else if(ctrl[1]) rout[1] <= in; else if(ctrl[2]) rout[2] <= in; else if(ctrl[3]) rout[3] <= in; endmodule

如果控制线是来自另一个模块地址译码器的选通,则每个选通对其他的选通是相互排斥的,因为它们都代表唯一的地址。但是,这里已经仿照特权判决那样的编码。由于控制信号的特性,以上的代码将正确地仿照并行方式编码那样操作,但是综合工具未必能够足够智能的识别它,特别是当地址译码器发生在另一个寄存器层次后面。

为了除去特权,展平此逻辑,可以按照下面的方式编码:

EXP5

module regwtite ( output reg [3:0] rout, input clk,in, input [3:0] ctrl ); always @ (posedge clk) begin if(ctrl[0]) rout[0] <= in; if(ctrl[1]) rout[1] <= in; if(ctrl[2]) rout[2] <= in; if(ctrl[3]) rout[3] <= in; end endmodule

除去不需要的特权编码,展平逻辑,减少路径延时。

4.寄存器平衡。

从概念上讲,寄存器平衡是平等地重新分布寄存器之间的逻辑,减少任何两个寄存器之间最坏的延时。这个技术应该随时利用在关键路径和相邻路径之间逻辑的高度不平衡时。因为时钟速度只由最坏条件路径来决定,可以做小的改变而成功地重新平衡关键逻辑。

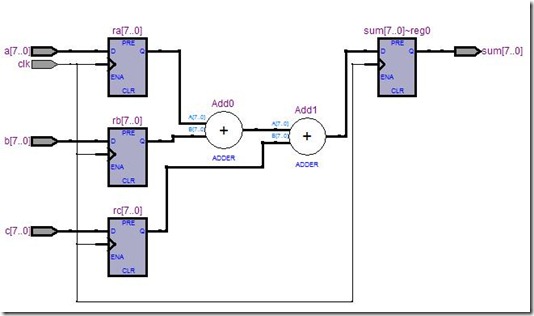

EXP6

module adder ( output reg [7:0] sum, input clk, input [7:0] a,b,c ); reg [7:0] ra,rb,rc; always @ (posedge clk) begin ra <= a; rb <= b; rc <= c; sum <= ra + rb + rc; end endmodule

如果通过加法器定义关键路径,在关键路径中的一些逻辑可以移回一级,所以平衡在两个寄存器级之间的逻辑负载。

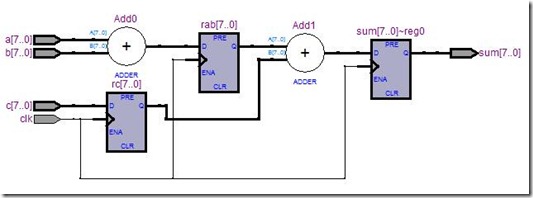

EXP7

module adder ( output reg [7:0] sum, input clk, input [7:0] a,b,c ); reg [7:0] rab,rc; always @ (posedge clk) begin rab <= a + b; rc <= c; sum <= rab + rc; end endmodule

从关键路径移动组合逻辑到相邻路径,寄存器平衡改善时序。

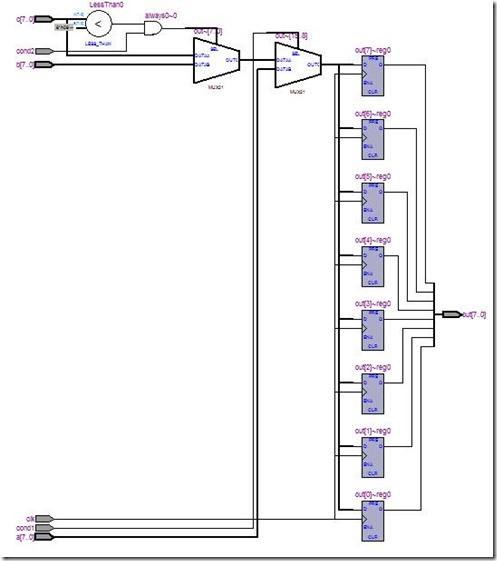

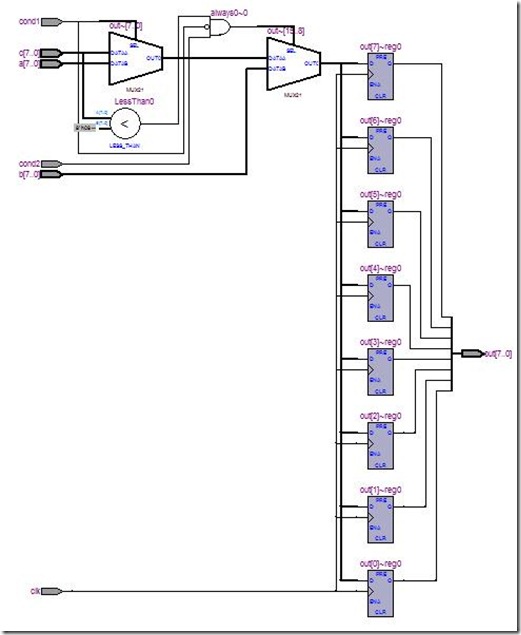

5.重新安排路径

在数据流中重新安排路径使关键路径最小化。当多个路径与关键路径组合时应该利用这个技术,组合逻辑路径可以重新安排以致关键路径可以移动到更接近目的的寄存器。利用这一策略,将只涉及任何给定的一组寄存器之间的逻辑路径。

EXP 8

module randomlogic ( output reg [7:0] out, input [7:0] a,b,c, input clk, input cond1,cond2 ); always @ (posedge clk) if(cond1) out <= a; else if(cond2 && (c < 8)) out <= b; else out <= c; endmodule

假设关键路径是在c和out之间,由一个比较器、一个门和一个MUX2-1串连组成,放在判决的MUX之前,假设条不互相排斥,可以修改代码重新安排比较器的长延时。

EXP 9

module randomlogic ( output reg [7:0] out, input [7:0] a,b,c, input clk, input cond1,cond2 ); wire condb = (cond2 & !cond1); always @ (posedge clk) if(condb && (c < 8)) out <= b; else if(cond1) out <= a; else out <= c; endmodule

可以重新安排与关键路径组合的路径来改善时序,方法是关键路径的一些逻辑放置到接近目的寄存器。