DSP EPWM学习笔记2 - EPWM相关寄存器设置问题解析

DSP EPWM学习笔记2 - EPWM相关寄存器设置问题解析

彭会锋

本篇主要针对不太熟悉的TZ 故障捕获 和 DB 死区产生两个子模块进行学习研究

感觉TI的寄存器命名还是有一定规律可循的

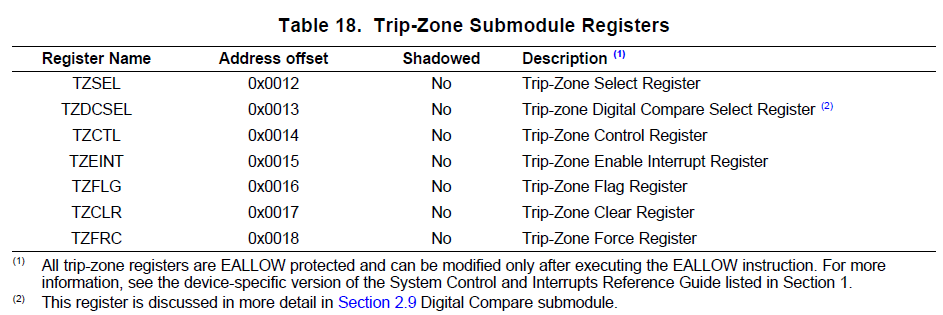

SEL主要用于选择位 CTL主要用于控制位 EINT主要用于使能中断 FLG是标志查询位 CLR中断标志清除位 FRC 软件强制使能设置位

1 TZ 故障捕获子模块

TZ子模块可以工作在Cycle-by-Cycle、One-Shot两种模式下,这两种状态的区别是:

- one-shot是永久起作用的,恢复它只有人工清除。

- 而Cycle-by-Cycle却是本周期有用,下一周期自动恢复

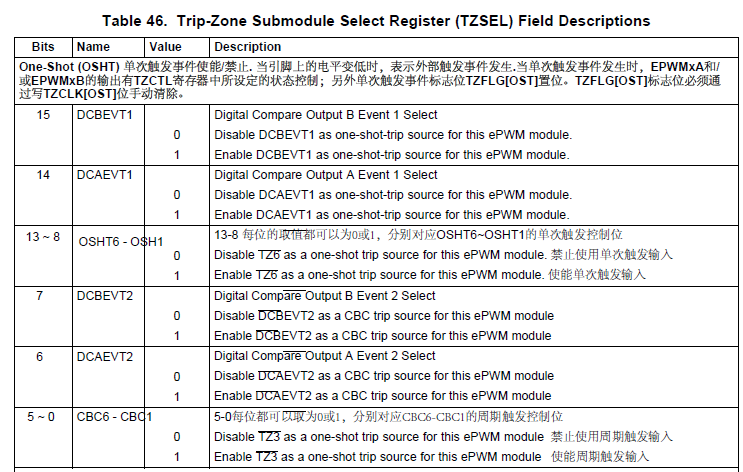

外部触发选择寄存器TZSEL 寄存器设置选项如下:

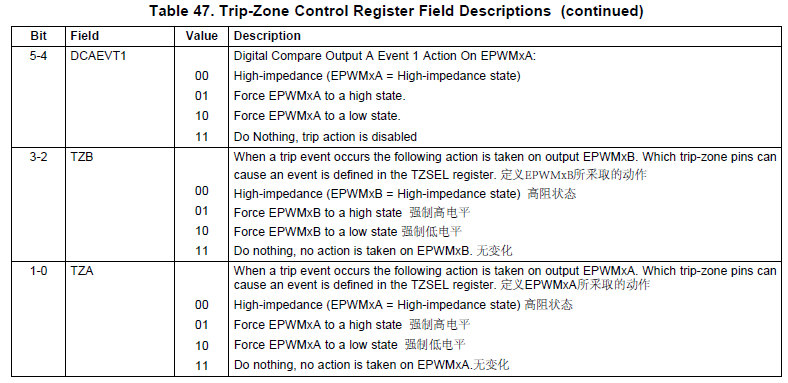

TZCTL主要设置TZA 和TZB寄存器即可,主要定义当外部触发事件发生时,定义EPWMxA和EPWMxB所采取的动作:

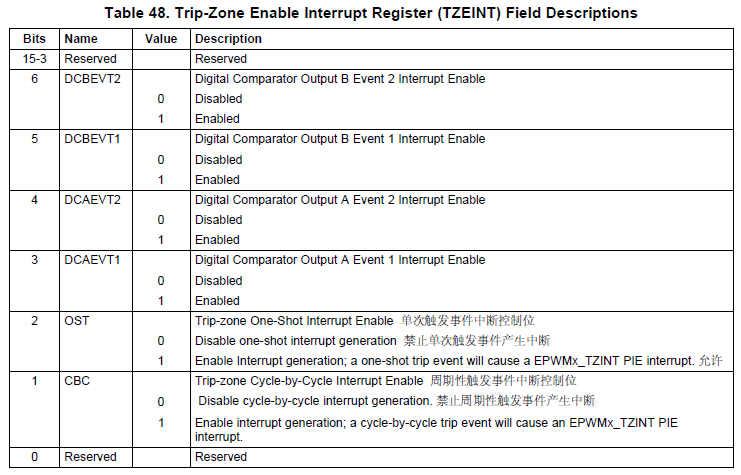

TZEINT 中断使能寄存器 控制周期触发和单次触发的中断标志使能

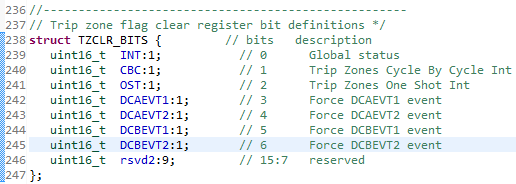

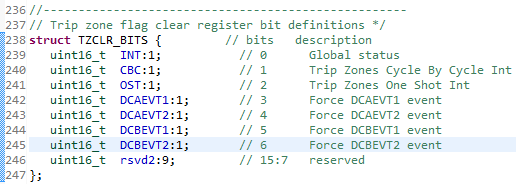

TZFLG 是外部触发标志寄存器 TZCLR外部触发清零寄存器 这两个理解起来比较简单,所以不再做过多说明,就是中断的时候查询标志位,然后中断发生了就把标志位清零即可!

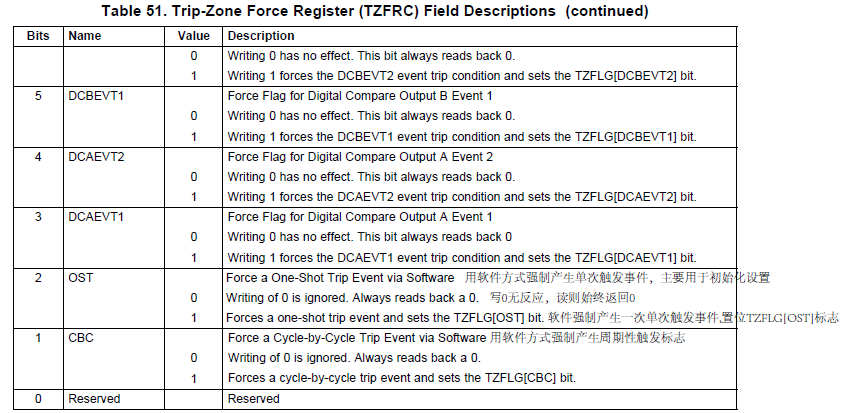

TZFRC 外部触发强制寄存器

TZ寄存器配置代码

EALLOW; EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_HI; // Forced Hi (EPWM1A = High state) EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_HI; // Forced Hi (EPWM1B = High state) EPwm1Regs.TZFRC.bit.OST = 1; // Forces a fault on the OST latch and sets the OSTFLG bit. EDIS;

2 DB 死区产生

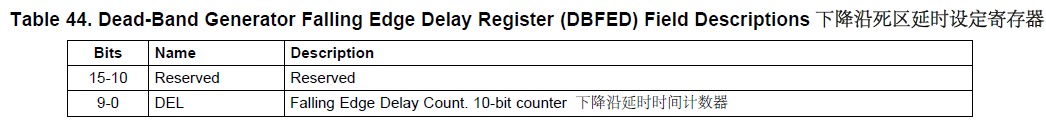

2.1 DB寄存器设置

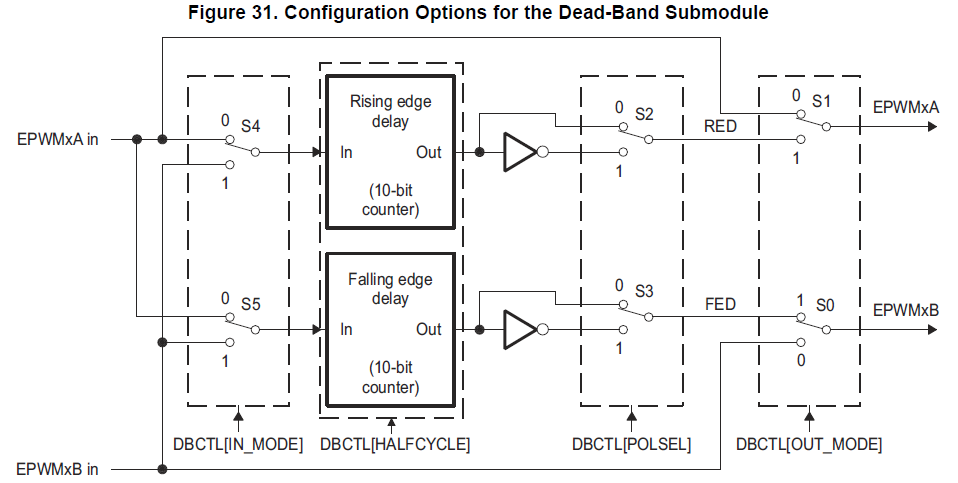

2.2 死区产生子模块内部结构

结合上图可以看出,DBCLT[IN_MODEL]就是选择哪个作为输入信号源进行延时控制;通过延时模块之后,实现上升沿和下降沿的延时功能;

然后有一个反相器模块,可以产生互补的输出信号,是否反转可以通过寄存器DBCTL[POLSEL]进行设置,感觉这个寄存器就是设置信号是否反转的,如果是1就反转,如果0就不反转,就这样子!

DBCTL[OUT_MODE]主要作用是选择那个信号进行输出,如果选择0,那么之前的延时的信号就被旁路掉了,整个DB模块就不起作用了,选择1才会产生死区功能;

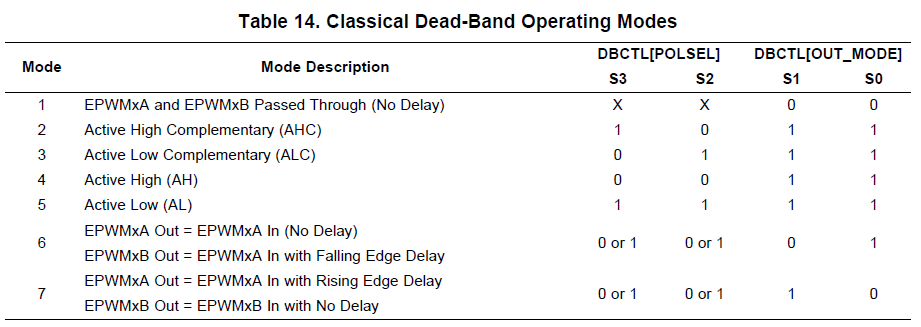

2.3 经典死区配置方案(感觉这里的后缀 C 就是互补的意思,没后缀则无互补,这个在2.4的波形图里面可以得到更好的体现)

2.4 加入死区延时的波形输出 (对比着2.2看2.3和2.4的图是最好明白寄存器配置的,也好理解输出波形是怎么样子的!)

2.5 寄存器配置代码

// DBCTL (Dead-Band Control) //========================== // OUT MODE bits #define DB_DISABLE 0x0 #define DBB_ENABLE 0x1 #define DBA_ENABLE 0x2 #define DB_FULL_ENABLE 0x3 // POLSEL bits #define DB_ACTV_HI 0x0 #define DB_ACTV_LOC 0x1 #define DB_ACTV_HIC 0x2 #define DB_ACTV_LO 0x3 // IN MODE #define DBA_ALL 0x0 #define DBB_RED_DBA_FED 0x1 #define DBA_RED_DBB_FED 0x2 #define DBB_ALL 0x3

// Active Low PWMs - Setup Deadband

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //这里基本上都是配置两个波形都是有延时才输出的,不会旁路掉延时波形

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_LO; //低电平有效,这里会对电平进行一个反转

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL; //选择 epwmxa作为信号源作为延时依据

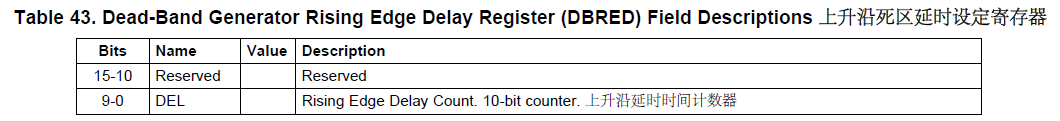

EPwm1Regs.DBRED = EPWM1_MIN_DB; //设置上升沿的延时

EPwm1Regs.DBFED = EPWM1_MIN_DB; //设置下降沿的延时

EPwm1_DB_Direction = DB_UP;

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· AI 智能体引爆开源社区「GitHub 热点速览」

· 三行代码完成国际化适配,妙~啊~

· .NET Core 中如何实现缓存的预热?