计算机组成结构必背点

一、计算机硬件组成

计算机的硬件基本系统由五大部分组成:运算器、控制器、存储器、输入设备(eg鼠标键盘)、输出设备(eg显示器);

存储器分为:内部存储器、外部存储器。 内部存储器即内存,容量小、速度快、临时存放数据;外部存储器即硬盘光盘等,容量大,速度慢,长期保存数据;

外设:输入设备、输出设备 合并成为外部设备,即外设;

主机:cpu+主存储器;

中央处理单元即CPU:运算器+控制器+寄存器组(32/64bit)+内存总线 等部件;

运算器功能:算术运算和逻辑运算;由算术逻辑单元ALU、累加寄存器AC(运算结果或源数据的存放区)、数据缓冲寄存器DR、状态条件寄存器PSW组成。

控制器功能:控制整个CPU工作,包括程序控制、时序控制、操作控制;

控制器组成:指令寄存器IR(暂存CPU执行指令)、程序计数器PC(存放指令执行地址)、地址寄存器AR(保存当前CPU所访问的内存地址)、指令译码器ID(分析指令操作码)

**从PC里取出指令存放地址,如0x000001,从主存里找到这个地址,按这个地址取出指令,存放到指令寄存器IR里,然后指令译码器ID分析指令。(PC--->IR---->ID)

CPU根据不同阶段决定取指令还是取数字:取指时取指令, 执行指令时取数据。

二、数据的进制转换

常见的进制:二进制(符号:0b,表示eg:0b0011)、八进制、十进制、十六进制(包含:0~9,a,b,c,d,e,f,符号:0x或H,表示eg:0x18F或18FH)

R进制转十进制:位权展开法。 eg:6进制数5043---》十进制=5*63+0*62 +4*61 +3*60 。从最低位开始,每一位乘以R的0,1,2,3...次方。

十进制转R进制:除余法。十进制数字 依次除以R,记录余数,直至商为0,。将所有余数从下往上排列成从左至右的顺序,即为转换后的R进制数。

示例:

特殊转换:二进制、八进制、十六进制转换。每3位二进制可以转换为1位八进制数值,每4位二进制可以转换为1位16进制数值。

eg:(0010 1101)2 转换成16进制: 0010=2 1101=1*23 +1*22+1*20=13(对应16进制的d)16进制即为 2d

三、数的编码方式

符号位,0表示正数,1表示负数,eg:+0(0 0000000),-0(1 0000000)

不同码制的特点:

| 码制 | 正数 | 负数 |

| 原码 | 正常二进制表示数,+0 | 正常二进制表示数,-0 |

| 反码 | 同原码 | 原码符号位外,取反 |

| 补码 | 同原码 | 反码末位+1 |

| 移码 | 补码符号位取反 | 补码符号位取反 |

不同字长的取值范围:

| 码制 | 定点整数 | 定点小数 | 备注 |

| 原码 | -(2n-1-1) ~ +(2n-1-1) | -(1-2-(n-1)) ~ +(1-2-(n-1)) |

整数:去掉符号位,实际数值位长为n-1,再减去-0、+0 小数:把整数范围整体除以2n-1 |

| 反码 | -(2n-1-1) ~ +(2n-1-1) | -(1-2-(n-1)) ~ +(1-2-(n-1)) |

原码符号位外,取反,其余同上 |

| 补码 | -2n-1 ~ +(2n-1-1) | -1 ~ +(1-2-(n-1)) | 反码末位+1,补码只有一个0 |

| 移码 | -2n-1 ~ +(2n-1-1) | -1 ~ +(1-2-(n-1)) | 补码符号位取反,移码也只有一个0 |

浮点数表示: N=F*2E F为尾数,为带符号的纯小数,影响数值精度;E为阶码,为带符号的纯整数,影响数值范围。

四、校验码

码距:从A码到B码转换所需要改变的位数。 码距越大,越有利于纠错和检错。

奇偶校验码:在编码中增加1位校验位来使编码中1的个数为奇数(奇校验)或偶数(偶校验)。奇偶校验只能检出1位错,无法纠错。

循环冗余校验码CRC:原始报文/多项式(eg:x4+x2+1,除数为10101),求得余数,最终结果为:数据位+校验位(即余数),计算方式为模二运算:相同为0,不同为1。

海明校验码:本质也是利用奇偶性来检错和纠错。方法是在数据位之间的确定位置上插入k个校验位,通过扩大码距来实现检错和纠错。

数据位为n位,校验位为k位,必须满足2k-1>=n+k。 eg:假设校验位k是3位,数据位n<=23-1-3 即数据位n<=4。

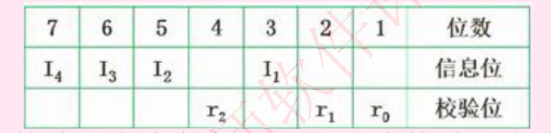

简易理解方式,数据所有位编号,在2的0、1、2......次方位插入校验数据,直到数据的最高位。

检错和纠错原理: 以数据1101为例

第7位=第1位+第2位+第4位、第6位=第2位+第4位、第5位=第1位+第4位、第3位=第1位+第2位===>根据位数编号和来判断,引用到哪一个校验位的,即为该位的被校验位

由上述位数编号可得,r2(第4位)校验的是I2、I3、I4 (第5、6、7位=0、1、1),r2的值== (与0、1、1异或运算的值)。===>校验位是由信息位异或来的

若为偶检验,r2应为0;若为奇校验,r2应为1;

若偶校验接收到的数据为1101101,如图排列后,校验位与信息位分别进行一下异或运算:

r2⊕I4⊕I3⊕I2 r2校验的位数为第5、6、7位,则 r2与这几位数一起进行异或运算,1⊕1⊕0⊕1=1(不满足偶校验结果应全为0)

r1⊕I4⊕I3⊕I1 r1校验的位数为第3、6、7位,则 r2与这几位数一起进行异或运算,0⊕1⊕0⊕1=0(满足偶校验结果应全为0)

r0⊕I4⊕I2⊕I1 r0校验的位数为第3、5、7位,则 r2与这几位数一起进行异或运算,1⊕1⊕1⊕1=0(满足偶校验结果应全为0)

将r2r1r0排列为二进制100,即指出第4位出错。纠错方法就是将1逆转为0。偶校验正确的接收数据为1100101。

五、计算机体系结构分类

SISD: 单指令流单数据流 一个控制器、一个处理器、一个主存模块,代表为单处理器系统;

SIMD:单指令流多数据流 一个控制器、多个处理器、多个主存模块,异步执行指令,代表为并行处理机、阵列处理机、超级向量处理机;

MISD:多指令流单数据流 多个控制器、一个处理器、多个主存模块,不可能存在的;

MIMD:多指令流多数据流 多个控制器、多个处理器、多个主存模块,作业、人、指令等各级全面并行,代表为多处理机系统、多计算器;

六、指令寻址方式

指令寻址方式:顺序寻址、跳跃寻址(不从程序计数器中给,跳跃后按新的指令地址开始顺序执行)

指令操作数寻址方式:

立即寻址(指令地址码字段就存操作数本身)

直接寻址(指令地址码字段存操作数在主存中的地址)

间接寻址(指令地址码字段指向的存储单元中,存储的是操作数地址)

寄存器寻址(指令地址码字段指向的是寄存器的编号)

七、流水线相关计算

流水线周期:指令分成不同执行段,执行时间最长的段为流水线周期

流水线执行时间:1条指令总执行时间+(总指令条数-1)*流水线周期

流水线吞吐率:总指令条数/流水线执行时间

流水线加速比:不使用流水线总执行时间/使用流水线总执行时间

超标量流水线技术:常规度为1,大于1就是超标量技术。当度为3时,相当于3条流水线并行执行,即取值、分析、执行每个阶段同时处理3条指令。

当题目提到度时,指令条数=总指令条数/度,然后再计算流水线执行时间。

浙公网安备 33010602011771号

浙公网安备 33010602011771号