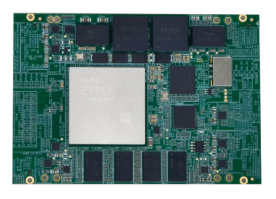

【TEC047】基于Xilinx XCZU47DR RFSOC的射频收发核心处理模块

TEC047是一款基于Xilinx的Zynq UltraSacle+ RFSoC Gen3系列FPGA XCZU47DR的射频收发核心模块,该模块将XCZU47DR芯片及其最小系统集成在了一个80*115mm的核心板上,可以作为一个紧凑的核心,进行功能的扩展,能够快速的搭建起一个多通道射频收发的信号处理平台,缩短用户的产品研发周期。

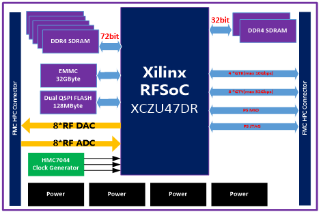

该核心板上,PS端支持1组72位DDR4 SDRAM,PL端支持1组32位DDR4 SDRAM,支持1片32GB的EMMC存储单元,支持2片QSPI Flash用于程序的加载,支持8路32G GTY引出到连接器,8路AD与8路DA以全差分的形式引出到连接器上。用户可以根据需求定义射频调理电路,支持直流、交流耦合、支持PA/LNA放大器调理电路,也可以支持选配射频前端。

该产品用于软件无线电、雷达与电子对抗等应用场景。

技术指标

1、板载 Xilinx Zynq UltraScale+ RFSoC 芯片:

1) 芯片型号:XCZU47DR-2FFVE1156I;

2)系统逻辑资源:930K;

3) 总分布式 RAM:13Mb,总块 RAM:38Mb;

4) DSP Slices:4272 个;

5)支持 8 路 14 位 ADC,最大采样率 5GSPS;

a 每个射频 ADC 支持 1 个 DDC;

b) 射频输入范围:1M~6GHz;

6)支持 8 路 14 位 DAC,最大采样率 9.85GSPS;

a) 射频输出范围:1M~6GHz;

b) 插值:2x/3x/4x/5x/6x/8x/10x/12x/16x/20x/24x/40x;

2、 模块主要资源:

1)PS 端支持 72 位 DDR4 SDRAM,速率 2400M;

2)PS 端支持 1 个 32GB eMMC 存储单元;

3) PS 端支持 2 片 512Mbit QSPI Flash 存储器;

4)PL 端支持 1 组 32 位 DDR4 SDRAM,速率 2400M;

3、模块对外互联接口:

1)接口连接器#1:8 路 ADC/8 路 DAC(差分信号)、PL IO;

2)接口连接器#2:8 路 GTY@max 32Gbps;

3) PS MIO、PS JTAG、4*GTR@10Gbps;

4、 物理与电气特征

1)模块尺寸:80 x 115mm;

2) 供电:4A max@+12V(±5%),常温功耗 50W;

3) 散热方式:风冷或导冷散热;

5、 环境特征

1) 工作温度:-40°~85°C、贮存温度:-55°~125°C(工业级);

2)工作湿度:5%~95%,非凝结;

软件支持

1、底层接口驱动程序:

1)裸跑下的各个接口测试程序;

2) Linux系统移植;

2、射频开发驱动程序:

3、 开发工具:Vivado 2022.1;

应用范围

1、MIMO无线电、5G基站、固定无线接入、测试测量;

2、雷达与电子对抗;

浙公网安备 33010602011771号

浙公网安备 33010602011771号