片内缓存加上位机的MIPI简单工程

本文梳理一种简单MIPI工程的实现方案

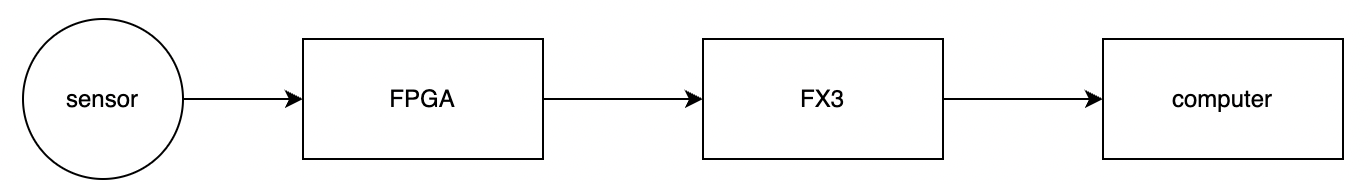

图像数据从一个mipi接口的摄像头输出,经fpga做mipi协议处理,缓存后发给fx3 usb接口芯片,最终送给上位机,如下图

包括图像格式转换,帧率适应等大量工作是在上位机实现,不在本文阐述范围内,这里主要介绍fpga中实现的mipi接口及数据缓存

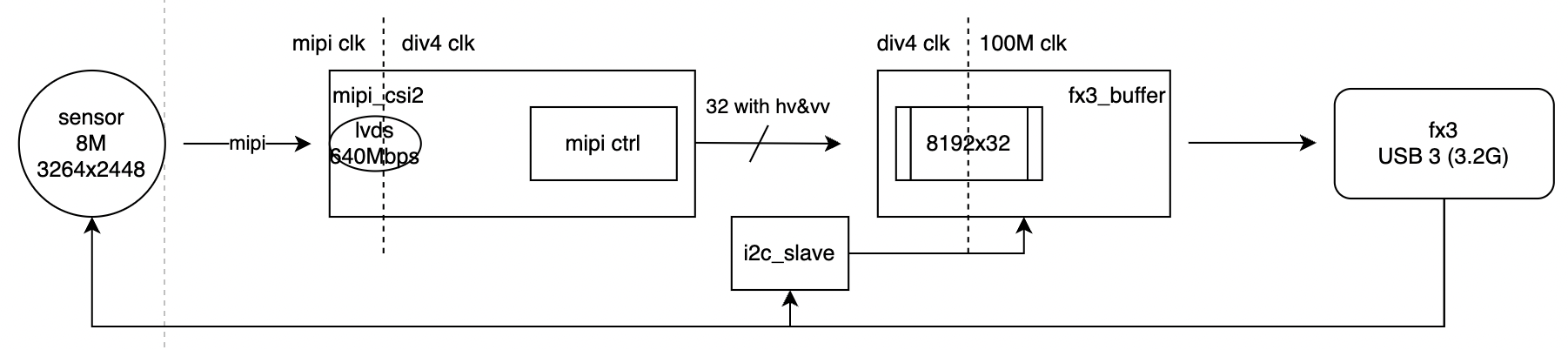

摄像头为一颗豪威8M像素ov8858,输出最大30fps 4 lane mipi,在fpga外部有mipi接口专用芯片,能将2线的mipi接口转成1路高速及1路低速信号送入fpga

fpga入口调用一个lvds ip将4路串行数据转成32比特并行数据,然后通过一个状态机检测mipi数据传输状态,当低速信号发生如下状态转跳

lp11->lp01->lp00

切换到高速信号上,在高速模式下,首先需要做的是数据同步,因为从lvds做串并转换的起始比特并不一定正确,具体的做法是:

将每lane转出来的8比特数据做移位,分别移位0-7,得倒8种结果与协议规定的同步头做比较,得到正确的并行数据

同步完成后,在状态机的控制下,按照帧格式输出数据到缓存模块

在缓存模块,例化了一个8k深度的fifo,实现两个功能:

>带宽适配

>异步处理

在fifo的写侧,需要控制3点:

>复位后,从一帧的起始开始写入

>防止写溢出

>在一帧数据最后添加padding,使一帧(包含padding)的数据大小为1KB的整数倍

防止溢出的实现方式为:在fifo剩余空间小于1行时,将当前行的数据写完后停止写入,并记录当前为第几行图像,等到下一帧图像对应下一行重新开始写入

数据传输要求为1KB整数倍大小是usb芯片fx3的要求

在读侧,当fifo中缓存数据大于1KB,启动一次突发传输即可,整体架构如下图所示:

这个系统一共有4个时钟域,mipi输入高速串行时钟,串转并后的并行时钟,与fx3对接的100MHz时钟以及i2c slave所使用的25MHz时钟

浙公网安备 33010602011771号

浙公网安备 33010602011771号