基于RAM的几何变换——镜像

基于RAM的几何变换——镜像

一、镜像基本概念

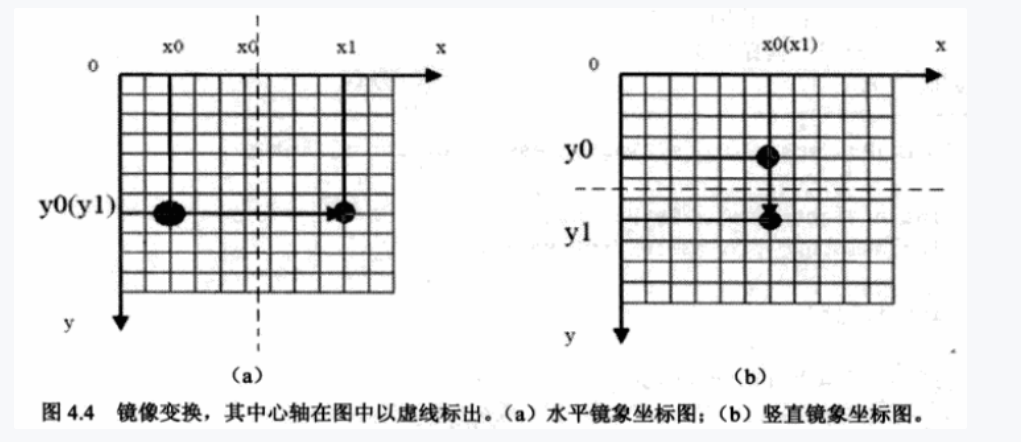

镜像变换可以分为水平镜像和竖直镜像,也就是我们所理解的x轴对称和y轴对称问题。可以预见的是,简单的打拍以及无法满足缓存了,要想实现水平镜像起码需要缓存一整行数据,要想实现垂直镜像起码要缓存一帧数据。这里我们可以直接思考帧缓存的手段,然后根据行号列号映射进行镜像处理。

对应公式:

// 水平镜像公式

(x1,y1) = (width-1-x1,y1)

// 垂直镜像公式

(x2,y2) = (x2,height-1-y1)

二、MATLAB实现

%--------公式法镜像-------------

clc;

clear all;

RGB = imread('jks.jpg');

[ROW,COL,N] = size(RGB);

% 定义三个0~255区间的三通道的图像矩阵,分别存储,H转、V转、HV转

H_mirror = uint8(zeros(ROW,COL,N));

V_mirror = uint8(zeros(ROW,COL,N));

HV_mirror = uint8(zeros(ROW,COL,N));

% 水平镜像

for i = 1:ROW

for j = 1:COL

for k = 1:N

x = i;

y = COL + 1 - j;

z = k;

H_mirror(x,y,z) = RGB(i,j,k);

end

end

end

%垂直镜像

for i = 1:ROW

for j = 1:COL

for k = 1:N

x = ROW + 1 - i;

y = j;

z = k;

V_mirror(x,y,z) = RGB(i,j,k);

end

end

end

%垂直镜像

for i = 1:ROW

for j = 1:COL

for k = 1:N

x = ROW + 1 - i;

y = COL + 1 - j;

z = k;

HV_mirror(x,y,z) = RGB(i,j,k);

end

end

end

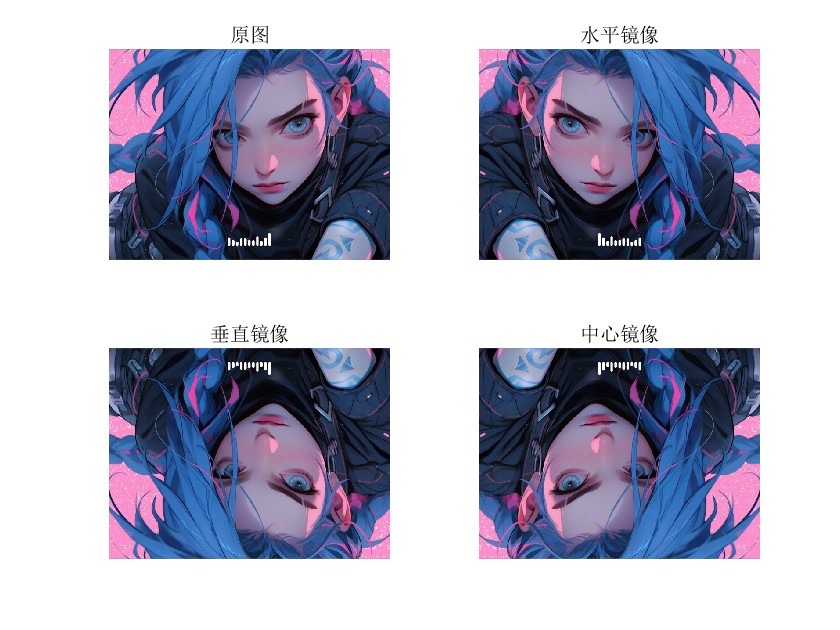

subplot(2,2,1),imshow(RGB); title('原图');

subplot(2,2,2),imshow(H_mirror); title('水平镜像');

subplot(2,2,3),imshow(V_mirror); title('垂直镜像');

subplot(2,2,4),imshow(V_mirror); title('中心镜像');

其中的简单思想就是利用三个简单的for循环来实现。

三、FPGA实现

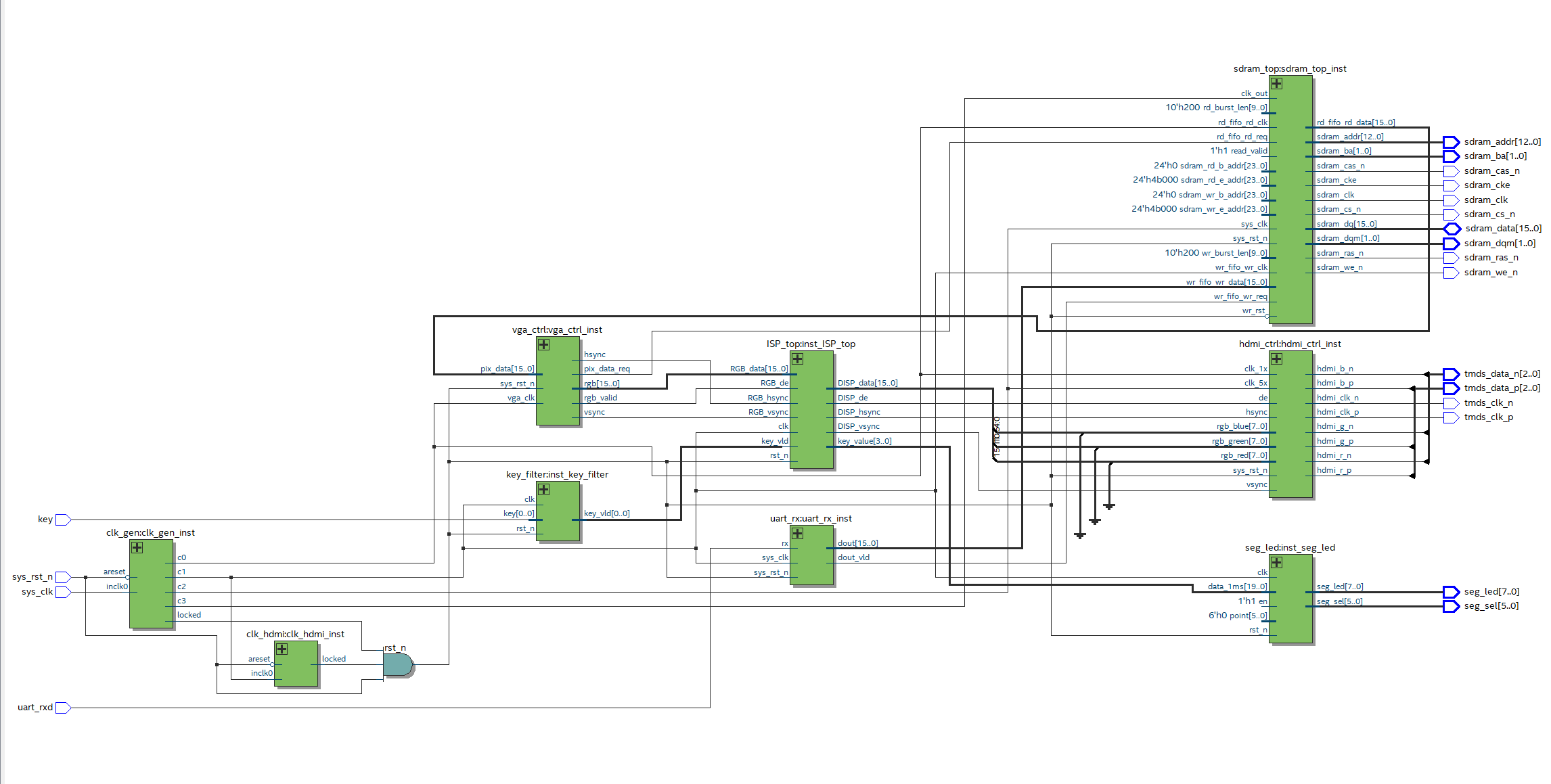

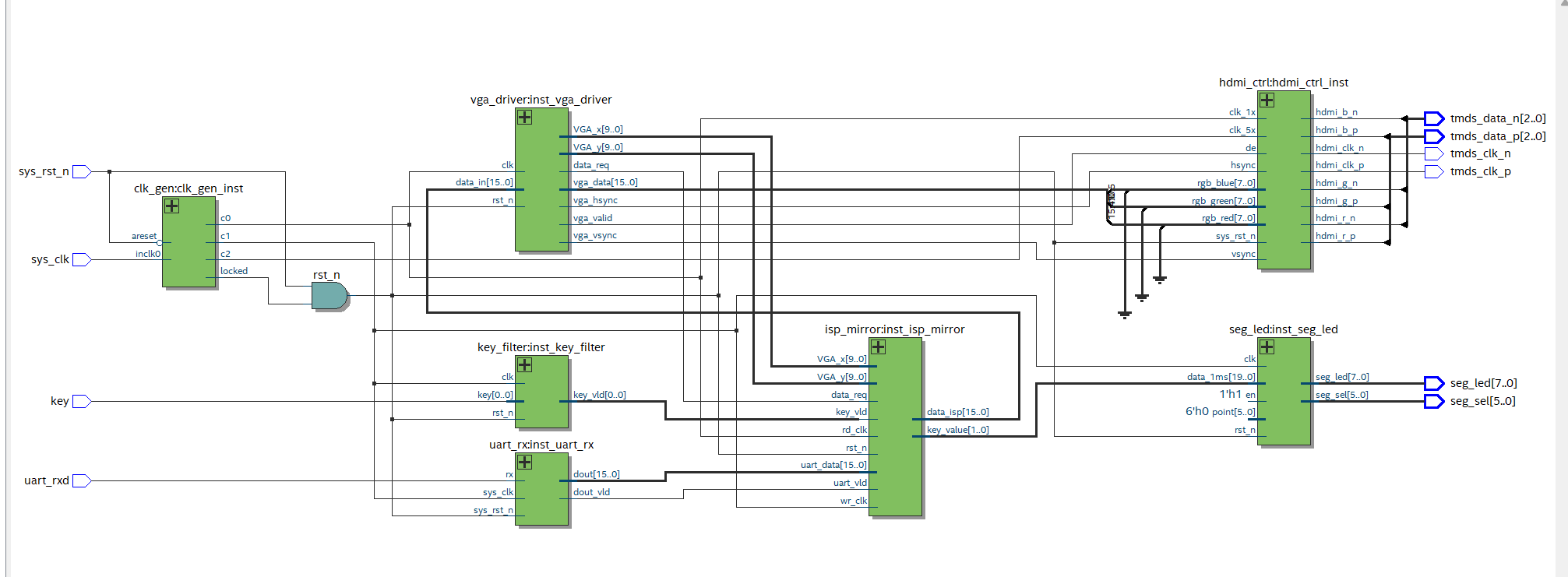

这里是我们之前图像处理工程的一个RTL视图,首先理清本节实验的重心,重心在于进行一些小幅度几何变换时,使用FPGA内部资源调用一个RAM完成帧图像的帧缓存,也就是替代我们的sdram模块

简单来讲,就是我们可以使用IP核调用一个具有基本功能的RAM来满足需求。

相比较之下,由于FIFO没有地址存取功能,而SDRAM以及DDR和DDR2的操作比较复杂,当我们需求更大分辨率图像信息的缓存时可以考虑SDRAM等等。

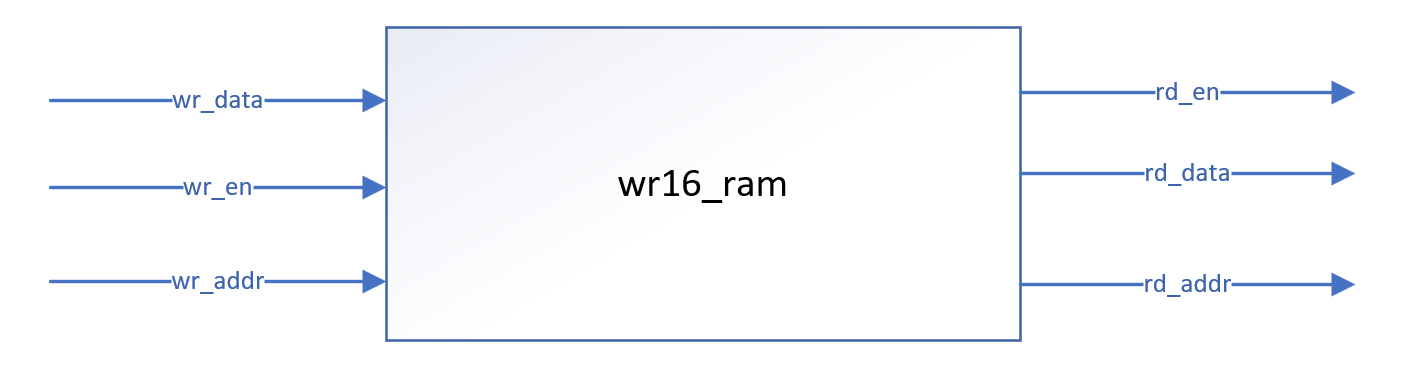

本节中参考了咸鱼FPGA中**使用二维数组代替RAM**的方法,这种方法不用生成IP核,更为简便

。

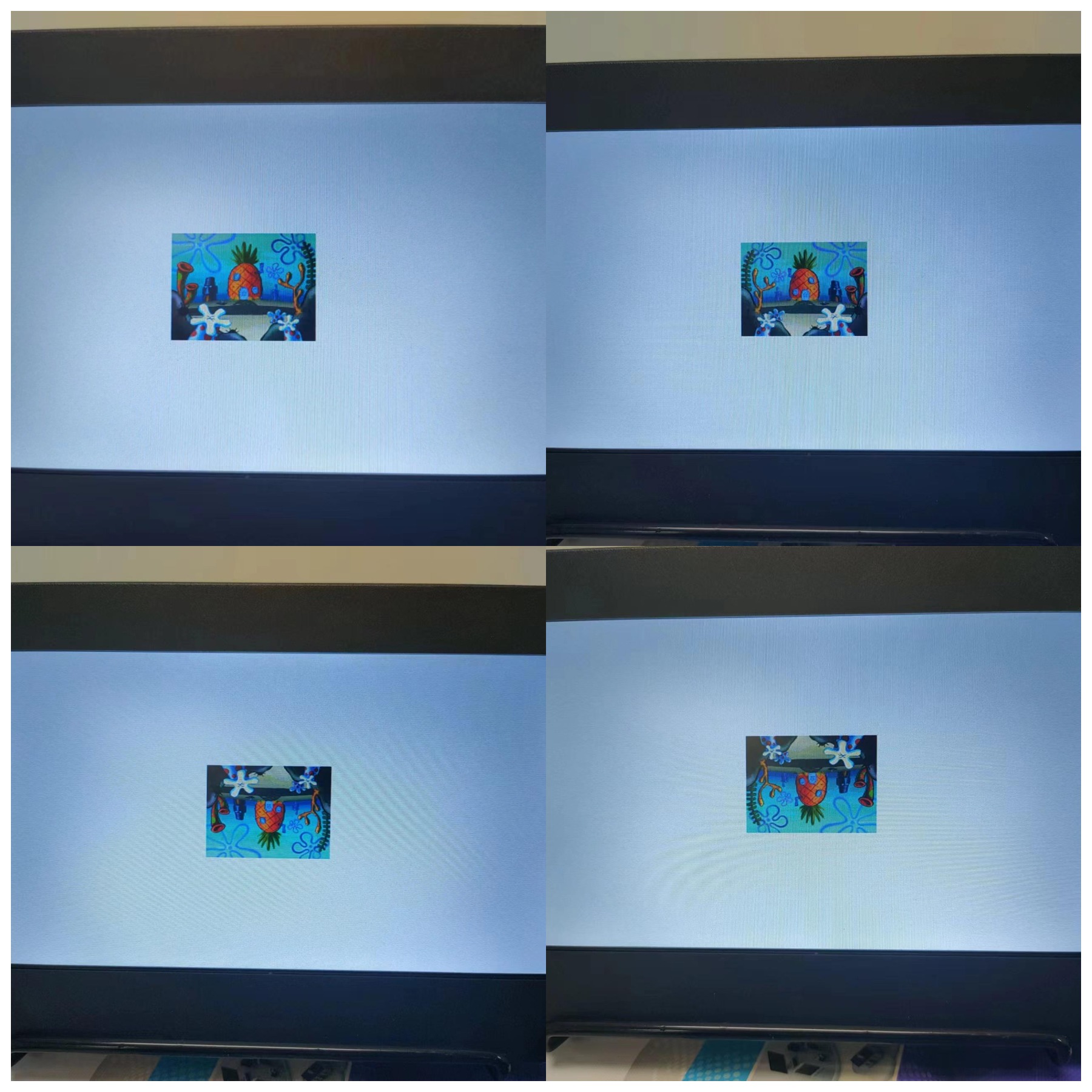

之前出现最大的问题可能是在vga驱动模块没有考虑好数据的流向与时序,导致这边HDMI不可以正常显示,在第二次代码编写过程中,优先保证vga时序的完整以及数据流的传输,逐步调整程序,使得显示屏从全白——四周白中间黑——四周白中间乱码——最后调通。

实验结果如上所示,已经可以完成正常显示。

四、出现的问题

1.使用 reg [15:0] buffer [COL*ROW - 1] 时候报错

Error (276003): Cannot convert all sets of registers into RAM megafunctions when creating nodes. The resulting number of registers remaining in design exceeds the number of registers in the device or the number specified by the assignment max_number_of_registers_from_uninferred_rams. This can cause longer compilation time or result in insufficient memory to complete Analysis and Synthesis

这里Intel给出的原因是因为Analysis & Synthesis部分无法将所有寄存器转换为RAM来实现所有的寄存器逻辑,设计中会保留大量寄存器而导致编译时间延长或者内存不足,因此无法完成分析综合部分。

按照Intel给出的操作我打开了Analysis & Synthesis的高级设置部分,但是我发现max_number_of_registers_from_uninferred_rams的默认值已经是无穷大,于是准备换着准备调用RAM的IP核

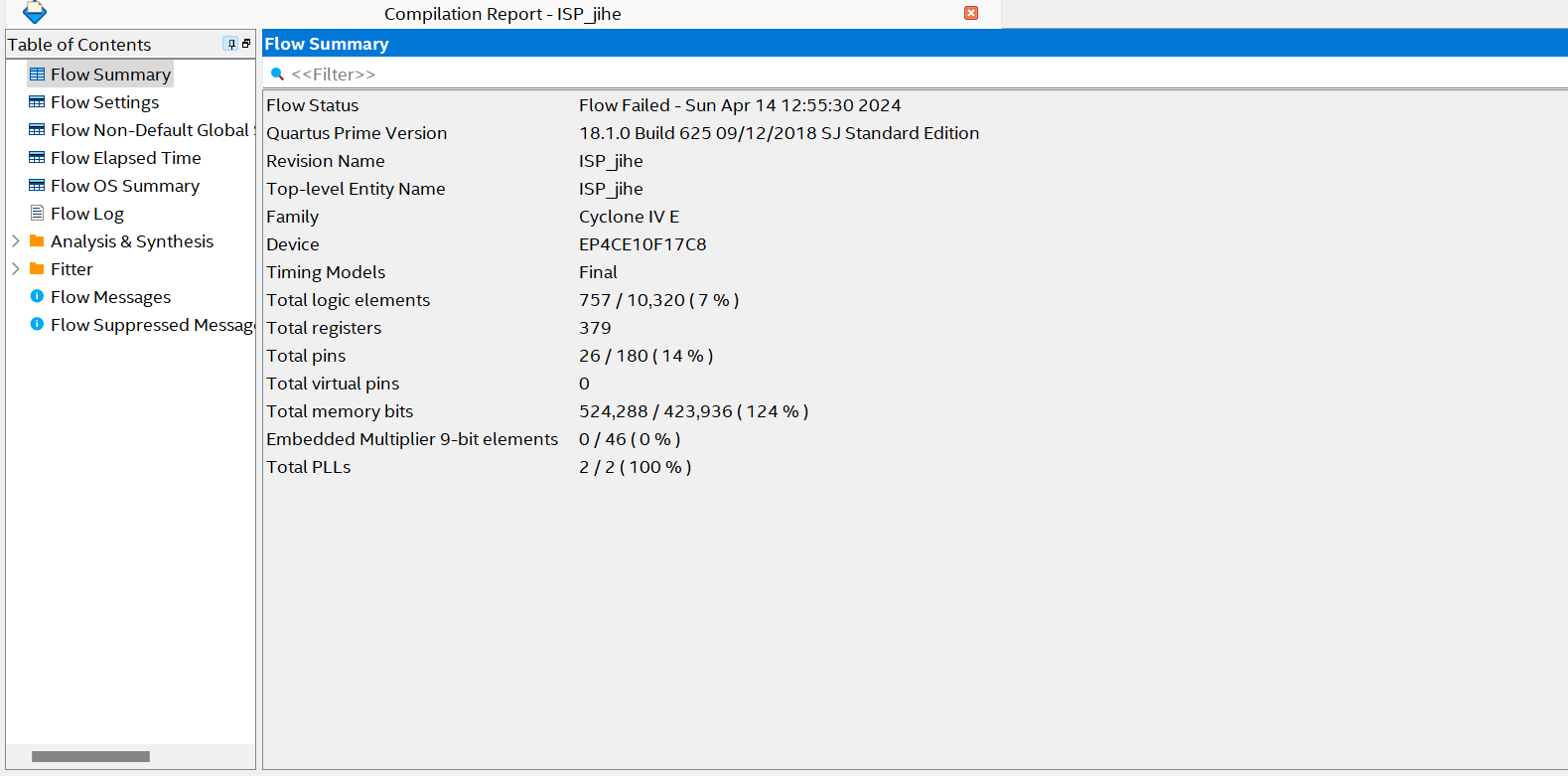

2.调用一个位宽16bit,位深32768的RAM时出错

Error (170048): Selected device has 46 RAM location(s) of type M9K. However, the current design needs more than 46 to successfully fit

可以看到,因为我们想要缓存一帧140x140的16bit位深的图片,由于140x140=19600,在IP核选择框里我选择了32768的位深,然后32768x16 = 524288要大于这款FPGA的总存储容量,所以在仿真时会报错。