7月16日 服务器宕机案例分析培训

完整文档下载链接:https://pan.baidu.com/s/1yucplbejLIiLm5neLlp7bw

提取码:我姓的拼音

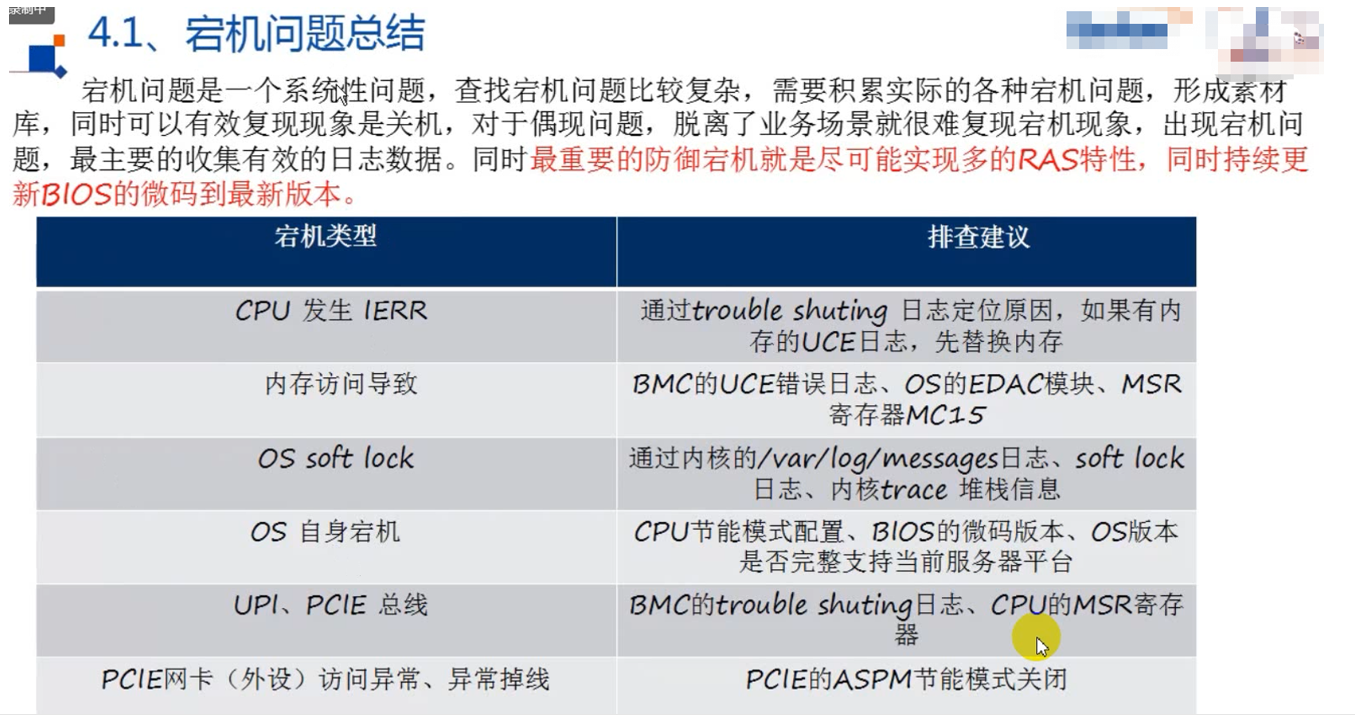

处理(宕机)问题最好的方法就是复现故障

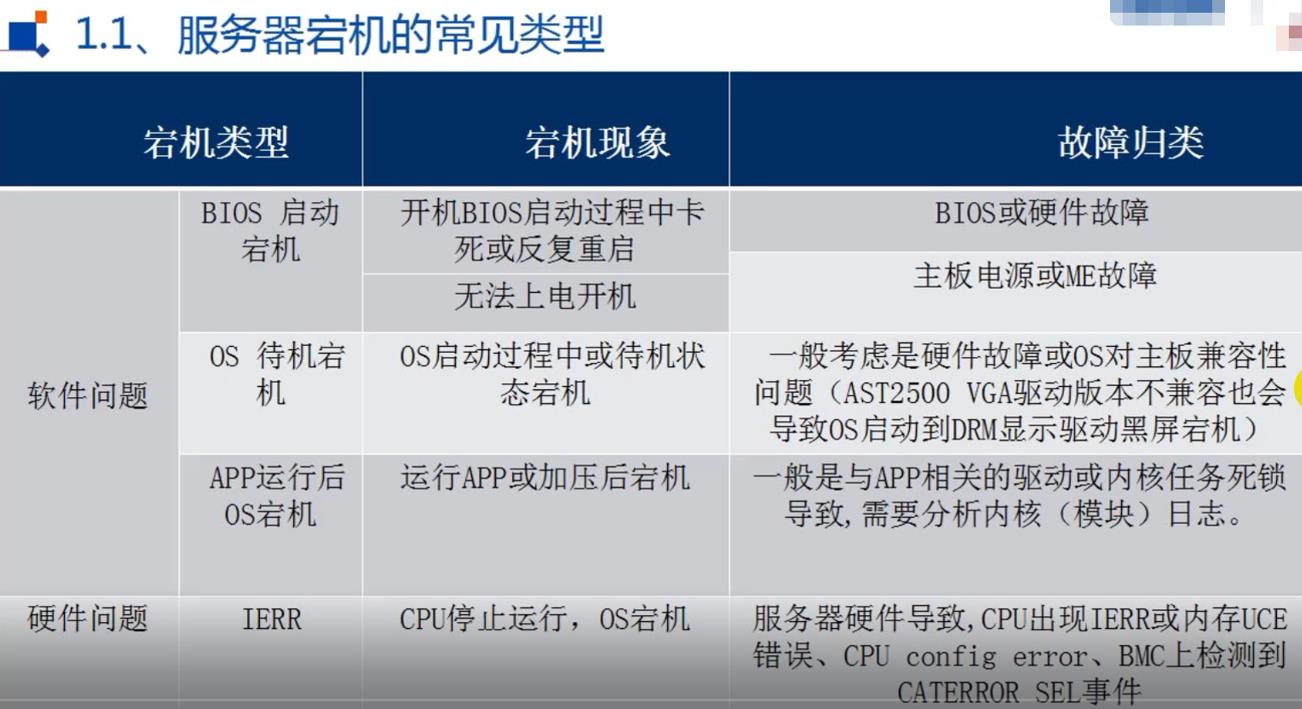

第一部分:服务器宕机分类

关于ME:

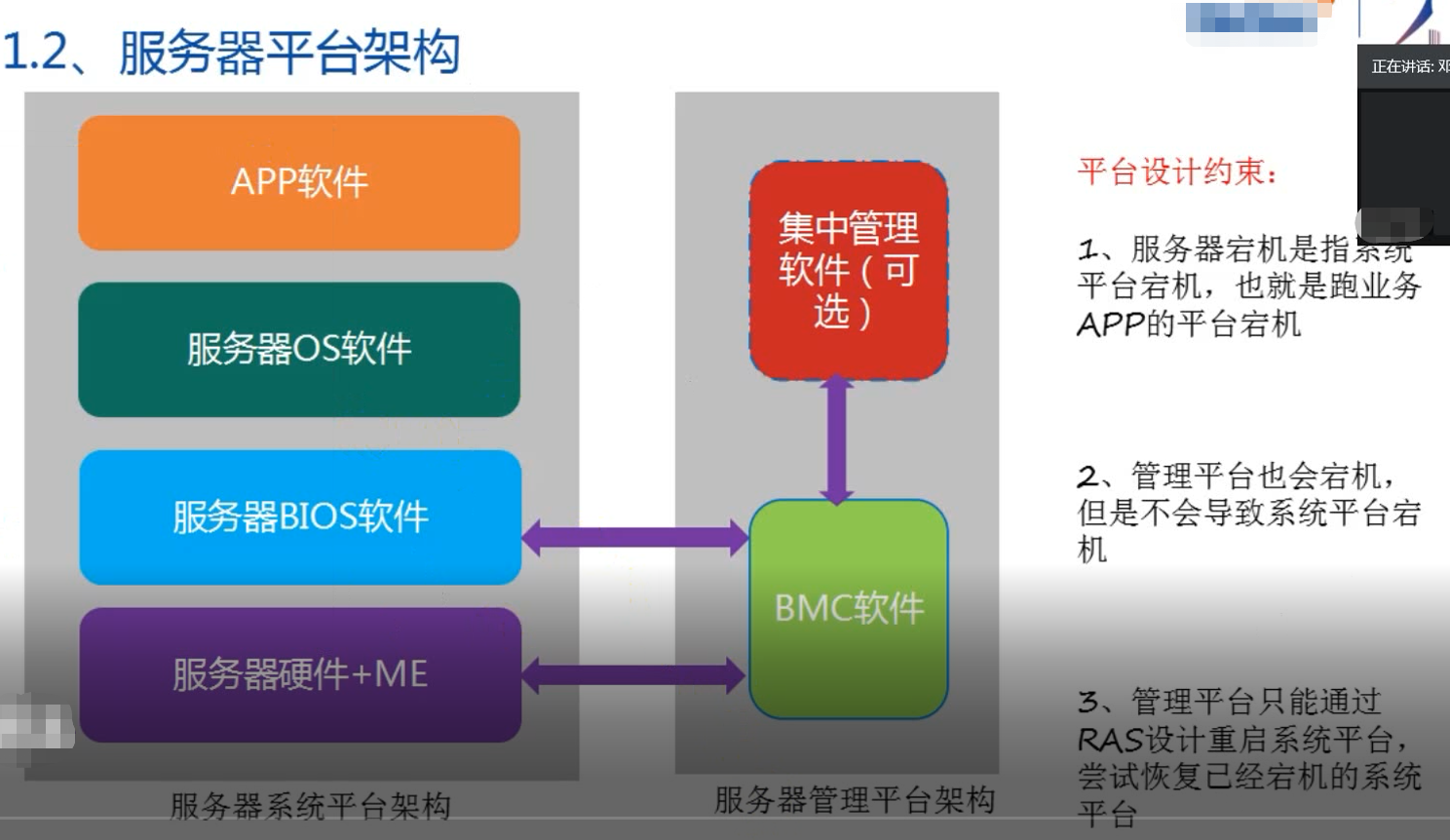

intel 为 PCH 开发一个程序(intel Management Engine)主要用于管理 PCH 与其他固件之间的协调沟通作用,以让系统达到最高性能和最协调的效用。ME 驱动一般会与 BIOS/EC 程序打包在一起,通过 Flash BIOS(快闪存储器)进行升级。ME 是一个有别于CPU的独立系统,本身其实就是一大堆固件代码实现的功能,比较关键的是 ME 里面有用于远程管理的功能,它可以在不受用户操控下远程管理企业计算机。

服务器的RAS性能:

RAS性能指的是机器的可靠性(Reliability)、可用性(Availability)和可服务性(Serviceability)。RAS能力主要看几个方面:System 级别的RAS特性、CPU RAS特性、内存RAS特性、I/O RAS特性等,RAS性能是个综合性指标。

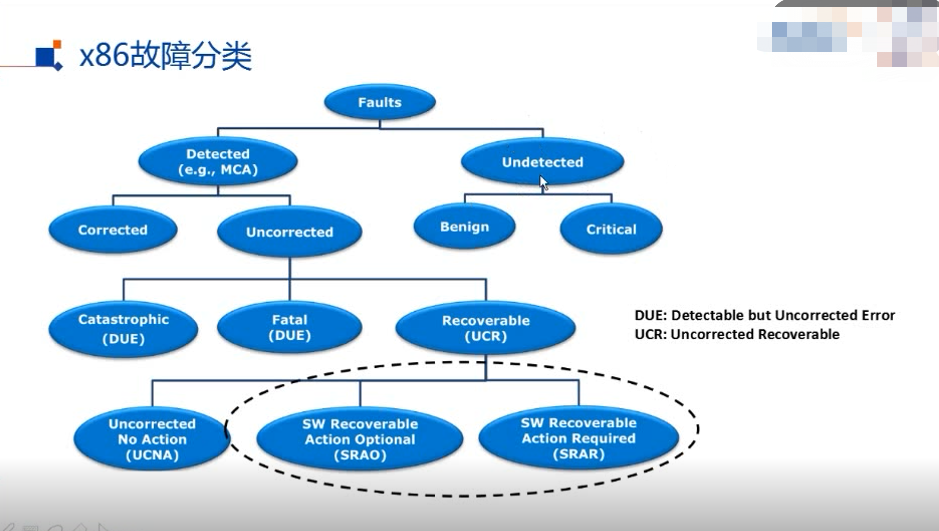

这个图来自某次intel的培训,是在讲X86平台故障分类

重点关注UCR:不可纠正但可恢复的。

第二部分:服务器硬件检测的原理

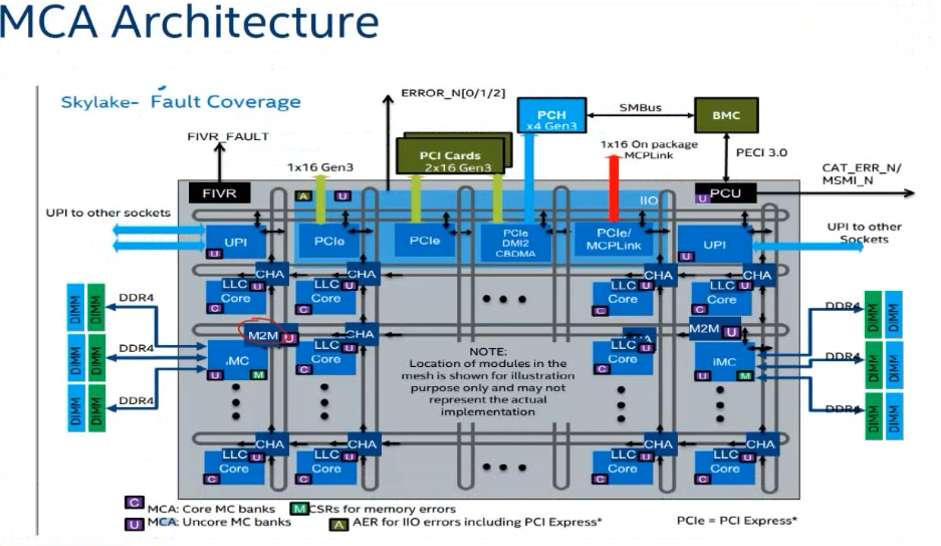

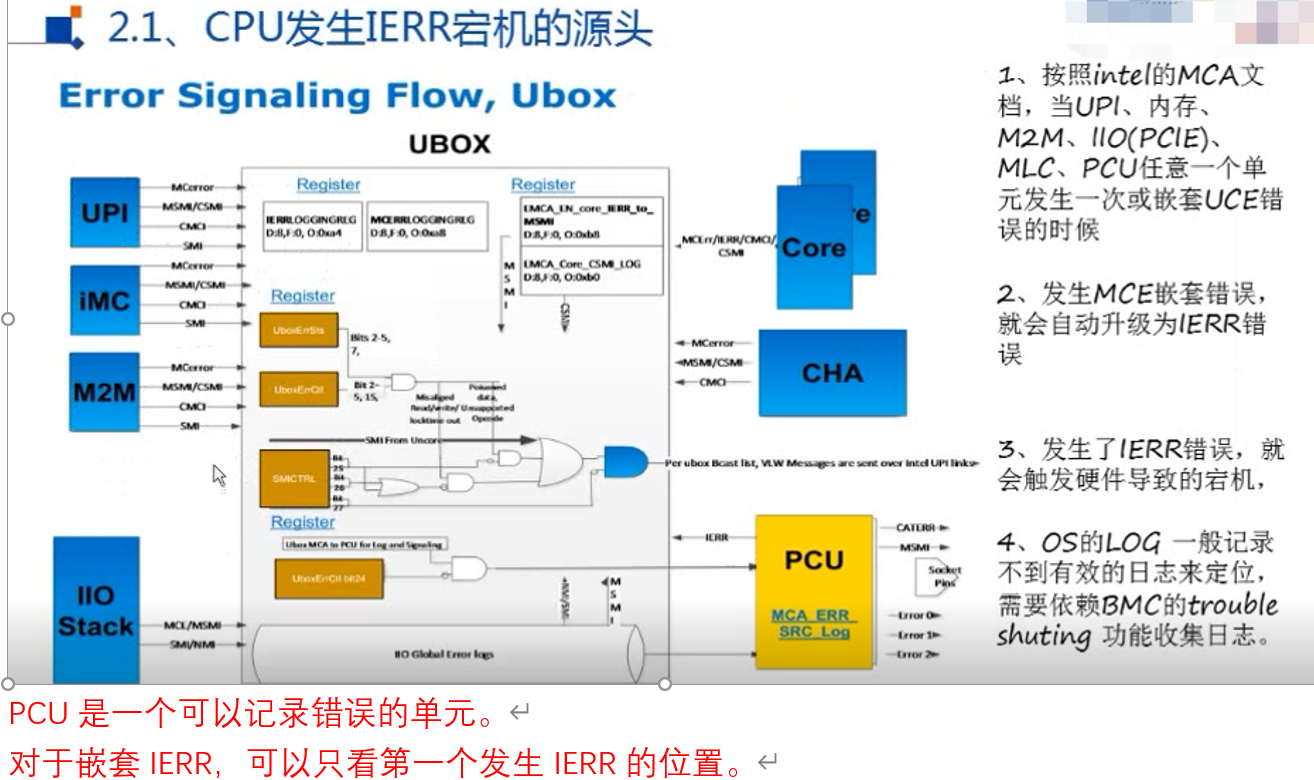

这是一个主板里面MCA的架构图,来源于芯片手册。

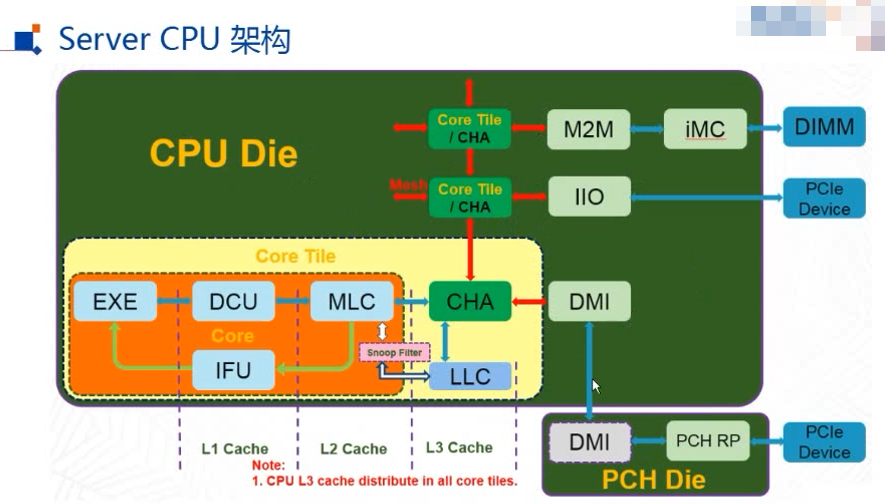

对内部,图上有很多core通过CHA(视频里他称做总线或者执行单元)连接起来。Core里面有L1,L2的cache,core之间有L3的cache。一个CPU有四IMC控制器(内存控制器),外面接DDR或者内存槽。IMC到CHA之间有一个M2M(它也是一个执行单元)。

对外部,主要是IIO(相应的是PCIe控制器),一个CPU一般有三个IIO。IIO是可配置的,可以配置成X16、X8、X4等,对应到主板上可以接各种外设和HBA卡。PCIe DMI可以接PCH(桥片),BMC可以通过SMBus访问桥片。BMC还通过PECI接口和CPU内部的PCU单元连接起来。BMC可以通过PECI接口去访问CPU内部的部分寄存器。UPI是用来实现多个CPU互联的,两路和两路以上的服务器才用到。下面的C、U、M、A表示在做故障处理时,图上C、U、M、A标记的位置含有寄存器,这些寄存器能够读取core的状态。

IIO:intel serial io driver 是Intel系列输入/输出驱动,是针对主板(芯片组)的驱动程序。

MCA:Machine Check Architecture,它用来检测硬件(这里的Machine表示的就是硬件)错误,比如系统总线错误、ECC错误等等。

PCH:集成南桥

PCU:CPU中的电源管家。PCU实际上是个单独的微控制器,有自己的执行代码,叫做pcode。在最开始pcode相对十分简单,就是按照操作系统的指示,将不用的内核关闭,进而尽量进入Package CState来节省电力。但是随着睿频和Speed Shift的引入,PCU开始管理整个CPU的Power Budget,即能耗的预算。

IMC:integrated memory controller集成内存控制器

这个图是在讲指令执行的流程,比如外部的一个PCIE设备怎么把数据传递到CPU当中,内存中的数据如何传递到CPU当中。 外设数据读到到内存上之后,内存数据可以到iMC(内存控制器),然后到M2M单元,M2M到CHA,一个CHA可以绑定一组core,CHA中数据就可以到达CPU内部。CHA可以到MLC cache,MLC(属于L2cache)可以到DCU、IFU(属于L1 cache),然后到达可执行单元。LLC是L3的cache,可以与L2的cache通信,同时可以通过CHA将数据传到外部去。

当CPU从外部读入数据时,如果L3cache CHA满了的话,CPU会先将cache数据读入到core当中去,写的时候也要把CHA数据先刷一遍,保证数据不能长时间存放老的数据。

IIO和PCH都可以连接自己的pcie设备,两者的区别是IIO的数量更多,速率更高。

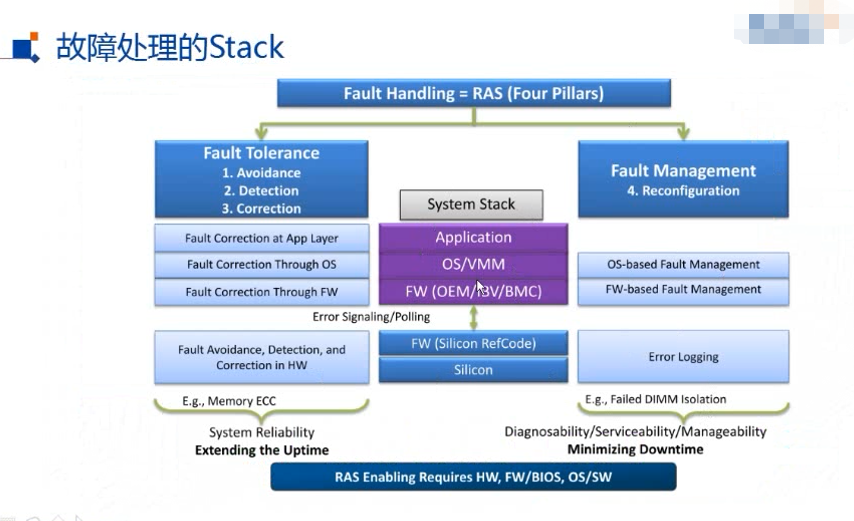

这个是故障处理的总体架构图。从分层来看,首先是硬件层:FW(Bios软件和ME),再往上是软件层的FW包括BMC,OEM等。再上面是操作系统和APP。处理现实故障比较复杂,需要判断是哪一层出了问题。首先看硬件层是否有问题,没问题就向上看下BIOS,Bios出问题的可能性一般很低,因为BIOS和用户层交互比较少,主要看操作系统和操作系统以上部分的日志。带外的东西还是主要通过sel日志来看。

第三部分:故障案例分析(省略)

浙公网安备 33010602011771号

浙公网安备 33010602011771号