嵌入式多核系统的在线分析

概述

尽管多核处理器比单核处理器提供更强大的处理能力,当时多核处理器存在难以检测和并发相关的错误。本文介绍了一种对多核处理器架构上程序时间测量的全新技术,这种技术通过在目标系统上运行,实现覆盖率的实时测量和复杂错误的分析。

现代汽车上的控制单元已经接管了越来越多的计算密集型任务,而且这种趋势还没有结束的迹象。随着复杂性的增加,错误发生的概率增加,而消除误差的效率越来越低。 不断增加的计算负载使得多核处理器的使用成为许多应用的必然。但是,从顺序处理到并行处理的转换可能会引入非常难以再现的错误,特别是如果代码从未打算用于并行执行。

毫无疑问,汽车电子行业需要在软件开发和测试方面特别努力,然而,只有能观察到错误的根本原因时,测试和调试环境才是有意义的。因此,可观察性是关键,与传统的单核系统相比,现代的多核架构给我们带来了特殊的挑战。这样的系统越集成,就越难以理解软件内部流程。这正是本文介绍的技术重点解决的问题所在。

经过充分验证的新技术

软件插装被广泛地应用于软件内部流程的监视,例如,为了测量代码块的执行时间或者测量覆盖率,一般采用代码插装技术自动在源代码里插入代码并记录程序的执行过程。然而,插装需要占用内存空间并影响程序运行的时间特性。幸运的是,有一种替代方案:几乎所有的现代处理器都有一个内嵌的跟踪单元(比如英特尔的Processor Trace),这个跟踪单元通过指定的接口(比如AGBT)或者标准接口(比如USB DCI、PCIe)进行通信。

图1: CEDARtools

这个跟踪单元提供了程序运行流程的信息且并不影响程序的运行。根据处理器架构和跟踪配置,还可以对程序的时序行为和内存访问进行重新构建,此外,许多跟踪单元使得轻量级硬件支持的插装成为可能,因此可以在发布代码中应用,(比如 PTWrite,MIPI STP)同样也可以用在对外设单元的跟踪 (内存控制器,通信单元)。

目前常用的嵌入式跟踪解决方案将宽带跟踪数据(几Gbit/s)存储在临时缓冲区内存中。在测试运行结束时,在PC上重新构建程序流程,并计算结构覆盖率。这个过程的限制是观察时间受缓冲区内存大小的限制,以及离线重建程序流所需的额外计算时间。

实时分析是对离线跟踪数据分析的进一步改进,需要解决两项技术难点,一是高压缩的跟踪数据流必须要经过处理,CPU的控制流必须要重新构造。这个运算能力必须能够适高速处理器CPUs (>1 GHz)且适合不同的操作系统。另一方面,产生的事件流必须经过处理,例如,通过记录跳转信息来计算结构覆盖率,或者通过使用在高级语言中配置的数据流处理器来动态监控大量的属性。

应用实例A:代码覆盖率

关键安全系统的标准(例如ISO26262)定义了测试过程的需求、所应用的测试技术,以及通过测量测试的结构覆盖率来验证这些测试的完整性。对于后者,必须要表明,根据应用的关键级别,所有的指令(语句覆盖了)、所有的跳转(分支覆盖率)或者所有的分支条件组合(MC/DC)在测试中都已经被调用了,一般来说,标准在很大程度上保持开放,在不同的测试级别(系统测试、集成测试、模块测试)验证对应的结构覆盖率。理想情况下,需求规格说明包含在测试中,这样结构覆盖率也可以对需求的质量做出证明。

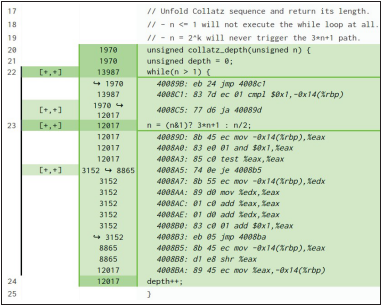

根据CAST-17意见书中所讨论的,基于目标码的结构覆盖率比基于源代码的结构覆盖率提供不同的信息,利用编译器产生的调试信息,测量出的目标码覆盖率可以映射到相应的源代码覆盖率,如图2所示。

图2:目标码覆盖率和源代码的映射

调试信息的分析可以在线实时进行,而不需要任何插装(因此不会影响目标系统的功能和性能),目标系统的测试覆盖率可以确定。图1所示就是这样的分析系统CEDARtools,利用FPGA进行实时分析。在集成和系统测试期间度量结构化测试覆盖率能够识别这些测试中的差距,并替代结构化单元测试。

应用案例B : 动态分析

静态分析是开发过程中的一个过程或测试方法。嵌入式系统的动态分析作为静态分析的补充显得越来越重要。而且,这种方法可以通过使用上述硬件实现.

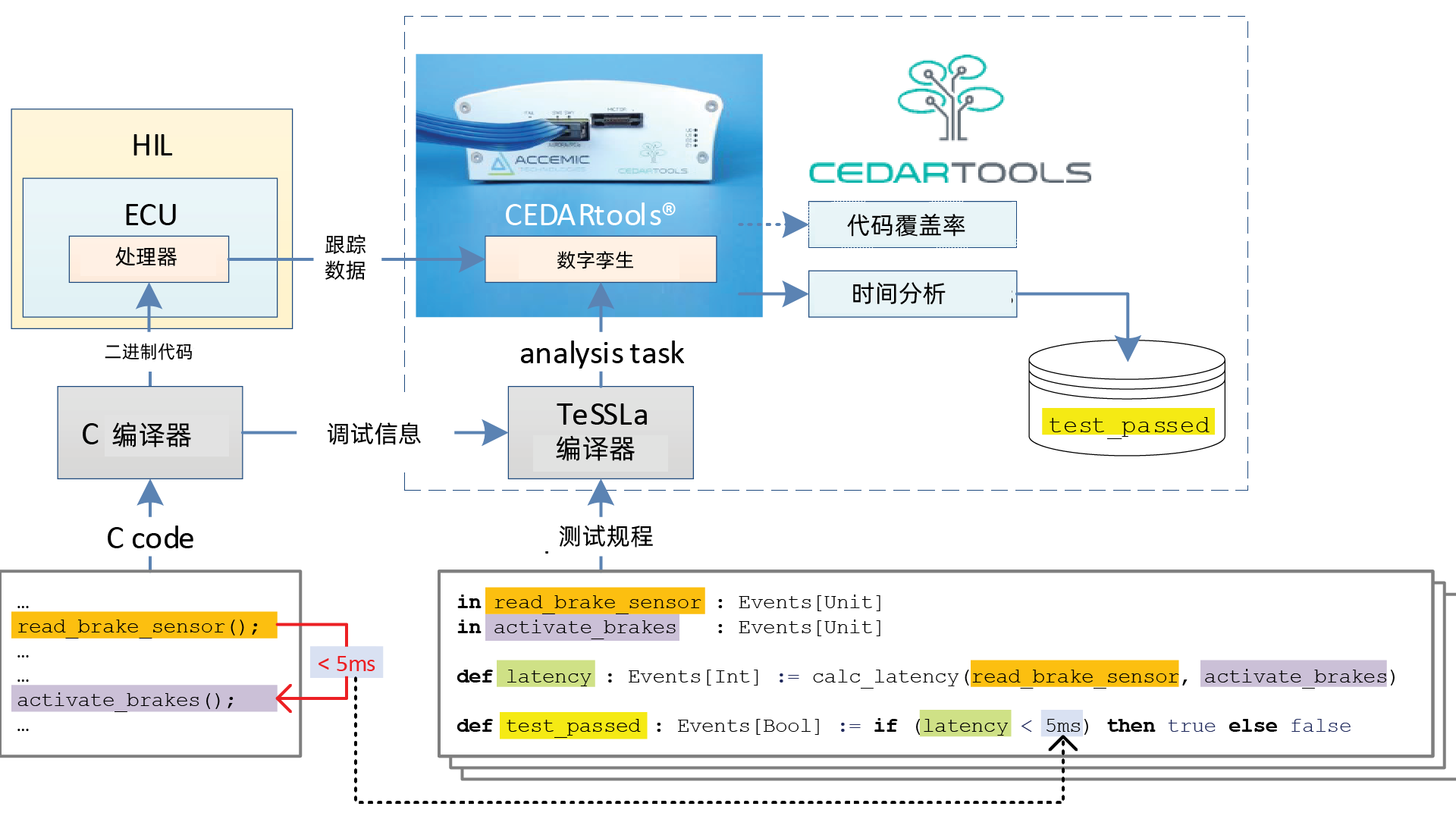

基于这个目的,在持续重建控制流的过程中对指令地址进行标记,在执行这些指令时,特定的事件会自动注入到发出的事件流中,然后可以在线分析事件流中的特定属性。所使用的时间处理单元可以利用一种高级语言配置 (www.tessla.io),多种时间属性(例如,由AUTOSAR TIMEX 或者Amalthea定义) 可以并行监视。FPGA只需要参数化事件处理单元,不需要单独合成逻辑结构,因此,高级语言属性描述可以在几秒钟完成,如图3所示。

图3 使用CEDARtools® 进行动态分析

动态分析也是调试的强大工具,特别是对于复杂的非确定性错误模式。根据发生的概率和应用领域的不同,寻找这些缺陷可能会需要付出巨大成本和开销。

设计的考虑

安全规范中已经规定了适当的预防措施,在电子控制单元(ECU)的测试期间和发布后都要具备的全面可观察性。跟踪接口应该在测试阶段和生产车辆的特定ECU版本中可用。此外,对于生产前和生产后车辆的测试,必须确保从ECU到分析仪(通常位于车内)的跟踪数据的无干扰传输。

结论

随着嵌入式系统复杂性的提高,产品发布后缺陷的数量不断增加,需要应用新的测试方法。这些方法包括结构测试覆盖率的度量,以及在完全集成的系统中运行时分析的自动执行。由于有了这项新技术,现在采用CEDARtools就可以进行这种分析,而且确保不会影响软件的运行时行为。

此外,即使在发布系统之后,它也允许有效地分析复杂错误的原因。为了能够使用这种测试分析技术,需要允许对由处理器输出的跟踪数据进行宽带宽访问。

附加信息1: 动态软件架构

汽车软件的重要性持续加大,这一趋势很可能会继续下去。特别是在高度自动化的驾驶领域,许多创新都是基于软件的。与上市时间的压力相结合,OEM厂商在验证他们的系统时面临着各种各样的挑战。除了不断增加的软件体系结构的复杂性之外,遗留组件的集成以及多核平台上的联合调度都是特别棘手的问题。

LET 概念(逻辑执行时间)提供了一个框架来应对这些挑战。但是,它依赖于一个重要的前提条件:必须确保每个任务在指定的时间窗口内安全地处理。静态分析目前不能提供足够的精度。因此,还需要使用测量方法来检查是否达到了最后期限。不需要软件插装的方法在这个环境中非常有趣,因为这种方法度量了真实的软件状态。

为了简化设计过程,LET概念通过只查看读写访问的时间,从给定平台上的物理执行时间中抽象出来。只要满足最后期限,就不考虑实际执行时间。

附加信息2:CEDATtools

CEDRAtools是 Accemic Technologies开发的用以对复杂嵌入式系统分析的工具,它解决了缓冲区大小受限的问题,目前汽车行业和航空航天行业主要的开发商都在评估和使用这个系统。

这个工具不采用跟踪数据存储事后离线分析技术,而是利用先进的硬件实时对上Gbit的数据进行分析,可以实现:

● 对一个或多个CPU的控制流和数据流进行重建,这是一个相当苛刻的任务,因为跟踪数据是由处理器以高度压缩的形式输出。

● 对生成的事件流进行高度可配置的实时分析(例如指令命中、数据访问、任务更改,最多100个事件/s),同时对多种复杂属性进行调查(效应链的最小和最大运行时间、统计、序列、值范围的检查等)。

● 连续实时测量结构测试覆盖率,不需要在长时间内收集大量的原始跟踪数据,以便以后在耗时的过程中进行评估,而是使用预定义的高级语言属性动态地分析跟踪数据。这可以在几分钟、几小时甚至几天内完成。但是,不需要分发原始数据:使用复杂触发器,可以精确地定义哪些原始数据和事件与分析相关,并存储在现有的跟踪缓冲区(4 GByte)中。

支持的处理器*:

- Arm® Cortex®-A, -R, -M

- Infineon Aurix™ TC2xx, TC3xx

- Power Architecture® (including NXP QorIQ® P-/T-Series)

- Intel® Atom® (among others E39x0)

支持的跟踪接口*:

- 高速串行接口 (Aurora): NEXUS, HSSTP, AGBT

- 标准接口: PCIe, USB

- 并行接口:Mictor, NEXUS

*部分还在开发中

这项工作是由EU H2020 project 732016 "COEMS" 和BMBF project "ARAMiS 2" (FKZ 01IS16025)基金成立的项目。“CoCoSI”研究项目(BMBF KMU Innovativ, FKZ 01IS19044)与项目合作伙伴Accemic Technologies、Fraunhofer IESE、Heicon和Intel对集成系统中结构测试覆盖率的测量进行了深入研究。

尽管多核处理器比单核处理器提供更强大的处理能力,当时多核处理器存在难以检测和并发相关的错误。本文介绍了一种对多核处理器架构上程序时间测量的全新技术,这种技术通过在目标系统上运行,实现覆盖率的实时测量和复杂错误的分析。

尽管多核处理器比单核处理器提供更强大的处理能力,当时多核处理器存在难以检测和并发相关的错误。本文介绍了一种对多核处理器架构上程序时间测量的全新技术,这种技术通过在目标系统上运行,实现覆盖率的实时测量和复杂错误的分析。