ICC - Floorplan

- 参考

- 在Floorplan之前,需要首先阅读一下IP和Stdcel的文档,观察是否有特别的要求,因为Floorplan的很多工作是跟stdcel和macro的设计风格有关,跟tf也有关。

1. 实现流程

-

(1)定义大小和形状

- 可以在手册中查找create_floorplan指令的相关选项配置。

create_floorplan -left_io2core 10...

- 可以在手册中查找create_floorplan指令的相关选项配置。

-

(2)Macro Cell 摆放

- 注意事项

- macro的摆放需要考虑timing、congestion以及IR Drop。

- 注意signal pin的方向,以及PG pin的分布。

- 注意Macro之间的连接关系,Hierarchy分析以及DataFlow分析。

- Macro的堆叠需要考虑congestion、timing、si的影响。

- 留一些空间给decap插入,用于减小Dynamic IR-Drop。

- 也要留一些空间处理走线较长的信号线,留有空间,可以插入buffer。

- 对于一些大型的设计,可以使用指令首先让工具摆放,作为一个初始参考。指令如下,可以选择多个选项。

- 其中 -no_hierarchy_gravity 为指定不按照module的hierarchy分块。

create_fp_placement -timing_driven -congestion_driven...

- 其中 -no_hierarchy_gravity 为指定不按照module的hierarchy分块。

- 一般都是手动摆放macro,摆放好了之后可以导出脚本,方便下一次直接使用。

- 摆放完之后要固定住,防止后面操作更改。

- 注意事项

-

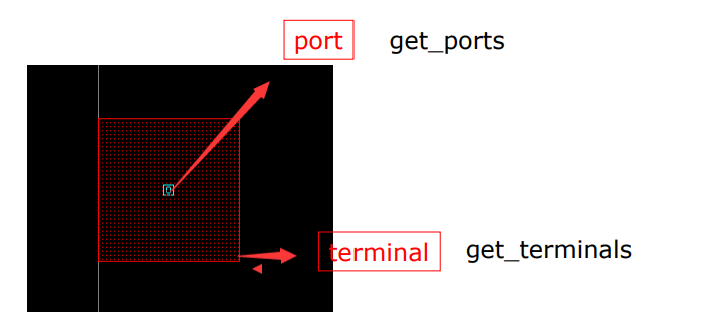

(3)Ports/Terminals的摆放

- port是逻辑存在的端口,而terminal是port的物理层实现。

- 注意port的金属层选择,不同金属层有不同的方向,选择合适的金属层让port接口“顺着放”。

- 也可以使用脚本让工具自动摆放,人为可以添加约束。

place_fp_pins -block_level

-

(4)EndCap Cell(Boundary Cell)

- 放在Row的边界,主要为了满足DRC,保护处于边界位置的stdcell;以及match stdcell environment。

-

(5)Tap Cell

- N 阱和P 衬底形成了一个PN结,为了避免这个PN结被正向偏置(Forwad Bias),形成Latch-Up效应,从而损坏整个芯片。最容易的办法是把N-Well连接到最高电压上,同时把P-Substrate连接到最低电压上。

- 而tap cell的目的就是这个,但是tap cell的作用范围有限,所以需要间隔一定距离就放置一个,具体的数据可以看Foundry给的文档。

- 也可以在标准单元设计时,集成well tie,这种情况就不需要单独的tap cell了。

- 可以使用下面语句添加tap cell。

add_tap_cell_array

-

(6)PG Network

- 目的:给所有的Macro和StdCell供上电。

- 评估标准:IR Drop。

- 摆放注意点

- 查看stdcell的metal layer及其方向。

- 查看macro的PG Pin的使用和方向。

- 注意Top给整个block的供电方案,连接关系(Via)。

- 从Top给底层金属供电,通过一层一层的Via孔打下去,这个从Top到底层金属的过程也有电压降的问题,但是如果Via孔打的多,电阻变小(具体公式可上网查),电压降就会减小。

- 注意Macro之间的channel的供电方案。

- 实现流程

- (a)Logically Connect PG Pins with PG Nets

- (b)设置Macro Rings

- (c)设置PG Strap

- pitch within group:一组VDD和VSS之间的间距,建议两者不要间隔太近,因为两者都要向下打Via,可能会导致Route阻塞。

- 建议strap细但密,还是考虑到strap太宽,打多个via,导致走线不好走。

- (d)Preroute Macros

- 对于Macro的pins需要preroute instances连接到电源网络上。

- (e)Preroute Rail

- 使用指令preroute_standard_cells布置Rail 供电网络给Stdcell的供电。

- 在Floorplan阶段可以使用下面指令快速将stdcell摆进去,然后检查供电网络是否布置出错或遗漏。

create fp placement -effort low - 在Placement阶段可以使用下面指令将Floorplan阶段placement的StdCell remove掉;重新布置。

remove_placement

- (f)Verify PG Connection

- 使用下面指令检查是否存在未供上电的cell/区域。

verify_pg_nets

- 使用下面指令检查是否存在未供上电的cell/区域。

- 注意:可以通过下面指令指定选择layer范围(M4到M1之间的金属层)进行Via连接。上面介绍的多个步骤中可能会使用到。

set_preroute_drc_strategy -max_layer M4 -min_layer M1

-

(7)额外的物理约束

- stdcell的摆放区域设定:例如靠近Core的边缘没必要摆放(硬性要求),部分区域指定部分stdcell可以摆(软性,自己定义的要求)。

- create_placement_blockage:不允许在指定区域摆放指定cell。

- create_bounds:在指定区域摆放指定cell。

- create_route_guide / create_routing_blockage

- 在Floorplan就指定Route相关设置的原因是,可能会虚拟走线计算时序等信息,所以需要提前把Route相关设置好。

- stdcell的摆放区域设定:例如靠近Core的边缘没必要摆放(硬性要求),部分区域指定部分stdcell可以摆(软性,自己定义的要求)。

-

(8)Write Floorplan

- 目的是将Floorplan信息指定部分写出DEF等文件,可以给DCT使用,做连线延时估计。

浙公网安备 33010602011771号

浙公网安备 33010602011771号