数字逻辑综合 DC 相关理解(四)

- 参考

- 《专用集成电路设计实用教程》

1. 多时钟同步设计 时序约束

-

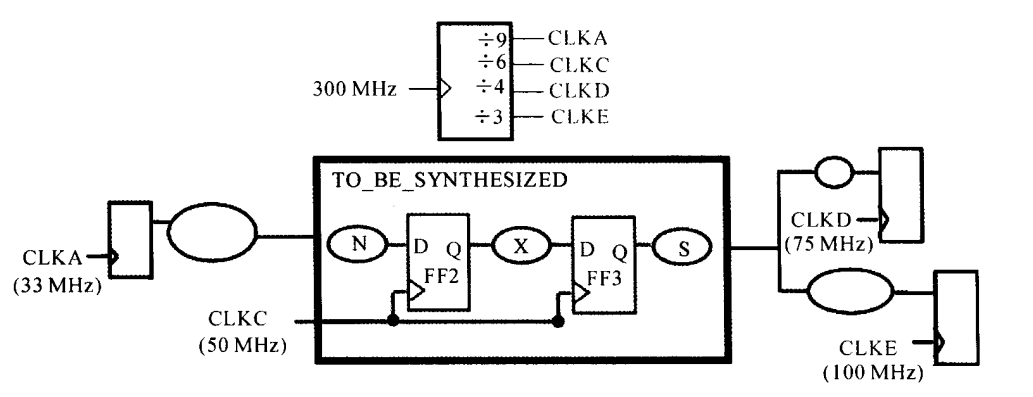

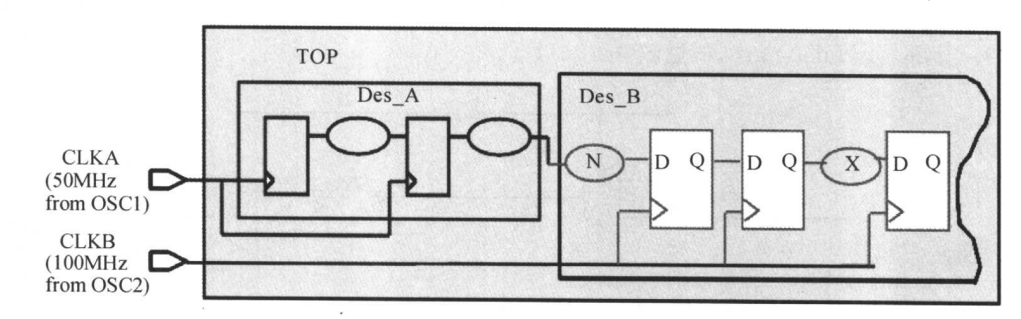

以下图为例,所有的时钟都来自同一个时钟源,所以是它们是同步设计。

- 可以看到要综合的模块输入只有CLKC,其他的时钟只作用于综合模块端口,我们需要对端口加以约束。

- 首先约束作为综合模块的主时钟CLKC,约束语句如下。

create_clock -p 20 [get_ports CLKC]

-

虚拟时钟

-

考虑到CLKA\CLKD\CLKE在要综合的设计中没有对应的输入端口,因此需要设置虚拟时钟。

-

虚拟时钟在设计里并不驱动触发任何寄存器,主要用于说明相对主时钟I/O端口的延迟。

-

输入端

- 由于虚拟时钟没有对应的输入端口,所以定义中没有源端口和引脚;另外还需要定义input_delay,约束如下。

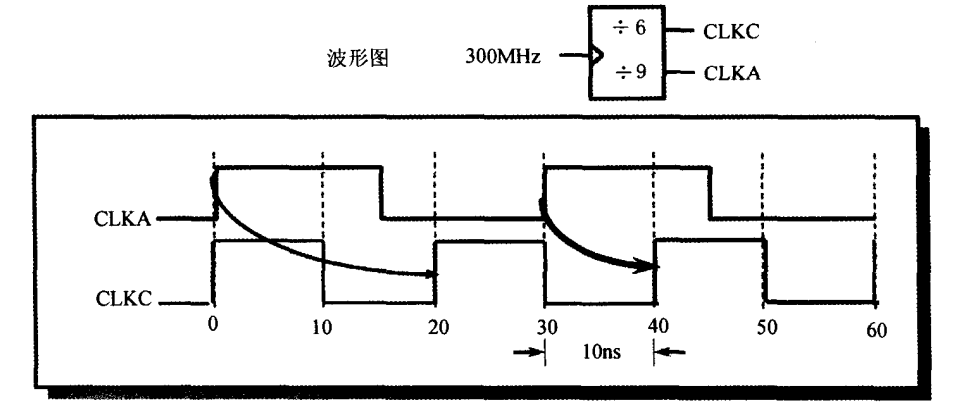

create_clock -period 30 -name CLKA set_input_delay 5.5 -clock CLKA -max [get_ports IN1]

- 时序图如下,所以可以计算需要满足$ t_N < 20-5.5-t_{setup}$ 以及 \(t_N < 10-5.5-t_{setup}\)。

- 由于虚拟时钟没有对应的输入端口,所以定义中没有源端口和引脚;另外还需要定义input_delay,约束如下。

-

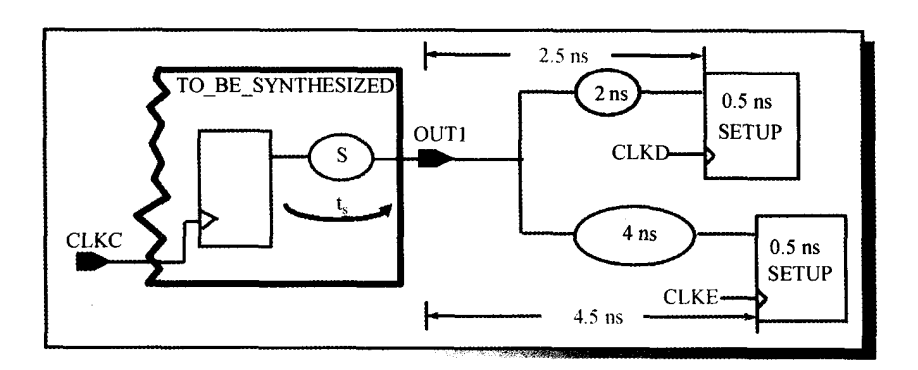

输出端

- 考虑到输出端有两个虚拟时钟,所以要加两个约束。

- 注:第二个命令中需要加上 -add_delay 选项。如果不加,第二条命令会覆盖第一条命令。

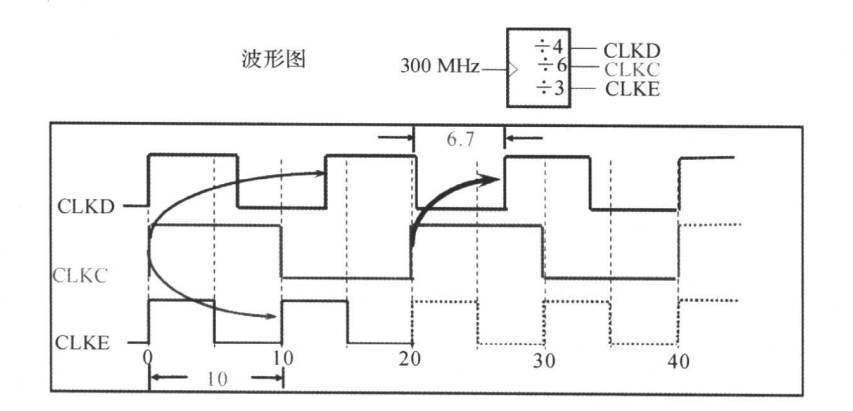

create_clock -period [expr 1.0/75*1000] -name CLKD #要用1.0而不是1 create_clock -period 10 -name CLKE create_clock -period 20 [get_ports CLKC] set_output_delay -max 2.5 -clock CLKD [get_ports OUT1] set_output_delay -max 4.5 -clock CLKE -add_delay [get_ports OUT1]

- 时序图如下,所以可以计算需要满足$ t_S < 10-4.5$ 以及 \(t_S < 6.7-2.5\)。

-

2. 异步设计的时序约束

- 需要考虑异步带来的亚稳态问题,可以考虑在设计中使用一些同步电路处理。

- 对于穿越异步边界的任何路径,我们都必须禁止对这些路径做时序综合,因为相位关系并不是确定的,对这些路径去做时间约束没有意义。

- set_false_path

-

我们可以使用 set_false_path 为跨时钟域路径作解除时序约束。指令如下。

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB] set_false_path -from [get_clocks CLKB] -to [get_clocks CLKA]

-

除了上面介绍的功能,还可以用来约束逻辑上不存在的路径,举例如下。

- 设计中难免会出现一些物理上连接的通路,但信号永远不会从这条路径走。可以使用指令report_timing_requirments命令报告出设计中所有的例外。

-

3. 多时钟周期的时序约束

-

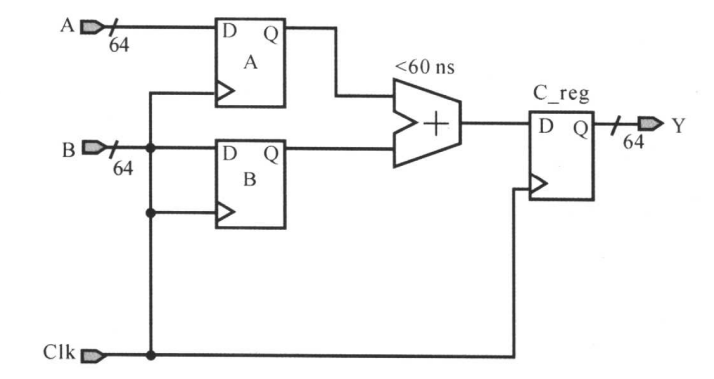

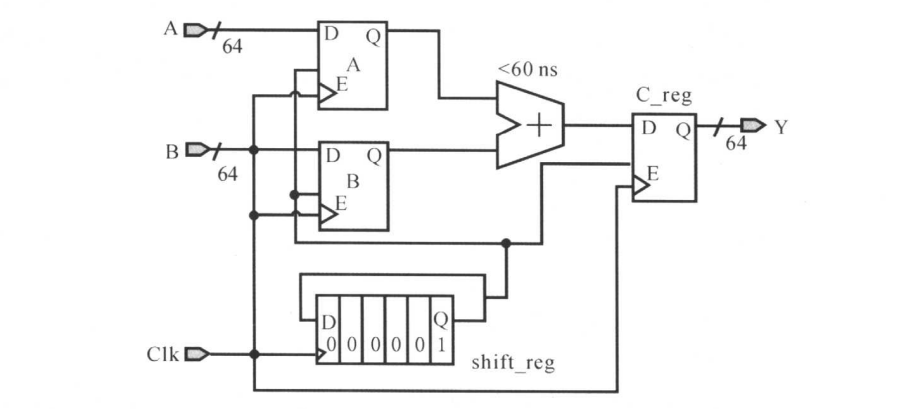

以下图电路为例,时钟周期定义为10ns,加法器延迟为6个时钟周期,那么我们需要对其进行多时钟周期的时序约束。

set_multicycle_path 6 -setup -to [get_pins C_reg[*]/D]

-

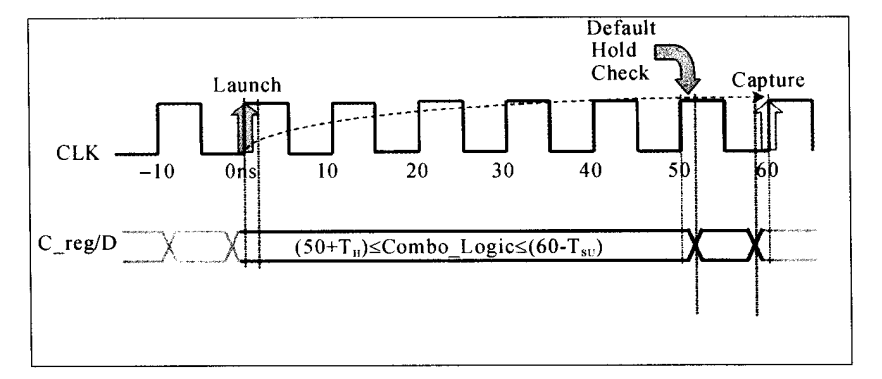

建立时间分析

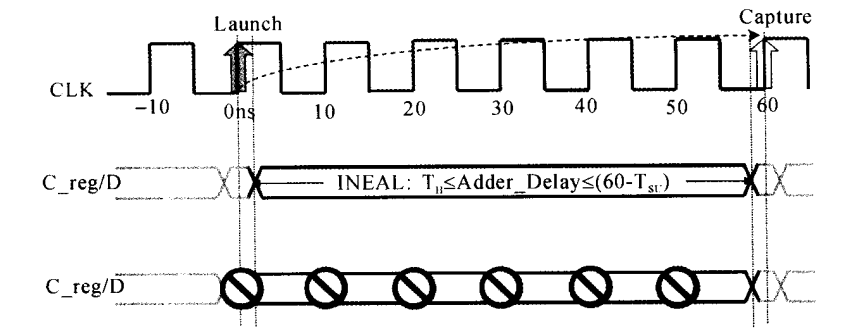

- 时序图如下,DC只在第6个上升沿做建立时间的分析,此时加法器允许的最大延迟为$ T_{delay} < 60-T_{setup}-T_{uncertainty}-T_{clk2q} $.

-

保持时间分析

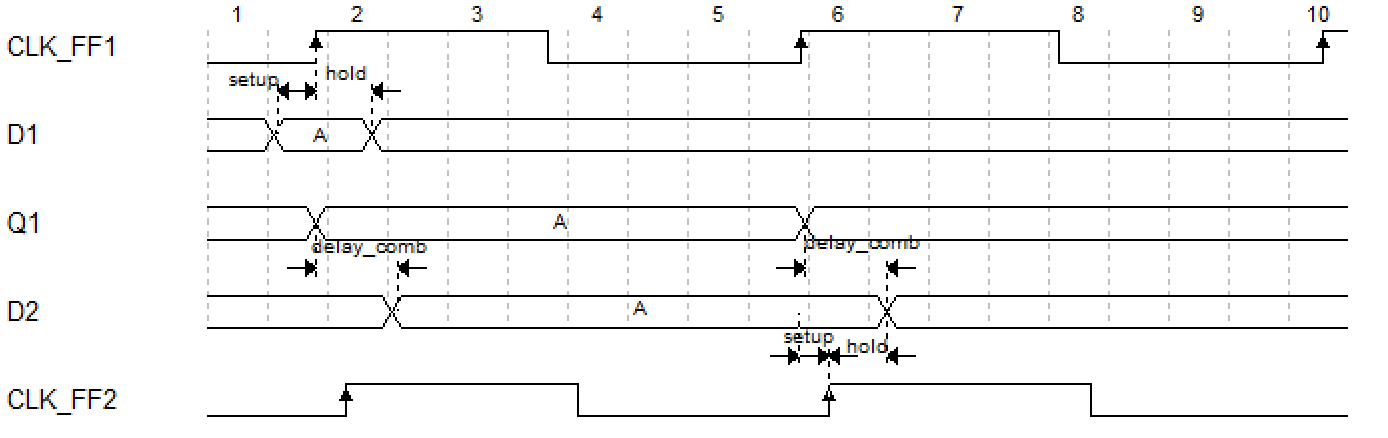

- 对于单周期的保持时间分析,时序图绘制如下,图中可以看到,对于FF2来说,想要采到正确的A值,那么组合逻辑延时需要满足 $ t_{delay-comb} > t_{hold} + t_{skew}$.

- 同理,对于多周期的保持时间分析,时序图如下,需要保证加法器的延迟至少要 $ 50+t_{hold}+t_{uncertainty}$.

- 对于单周期的保持时间分析,时序图绘制如下,图中可以看到,对于FF2来说,想要采到正确的A值,那么组合逻辑延时需要满足 $ t_{delay-comb} > t_{hold} + t_{skew}$.

-

对于既要综合出一条路径延时满足建立时间60ns又要满足保持时间50ns,实际上是没有必要的,这样会增加电路的复杂度。

- 在保持时间分析给出的时序图可以看到,在CLK_FF1第一个采样的上升沿就分析保持时间,限定组合逻辑延迟。因此对于多周期也是同样道理,可以在0ns时分析保持时间。约束语句如下。

set_multicycle_path 5 -hold -to [get_pins C_reg[*]/D] # 简化后,指令为: set_multicycle_path 0 -hold -to [get_pins C_reg[*]/D] -

根据前面的介绍和计算,我们可以设计相应的时钟使能电路,使得最后一级寄存器可以在期望的时钟进行采样接收正确的数据。

-

4. 门控时钟的约束

- 关于门控时钟相关内容可以看这篇博客。

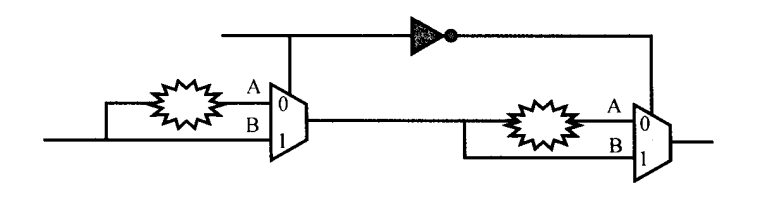

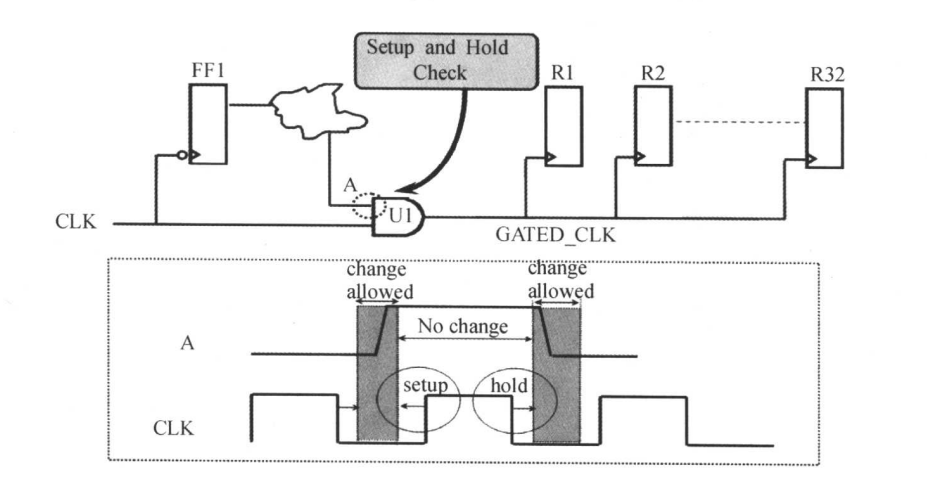

- 考虑到不带锁存器的门控时钟可能会出现毛刺的情况,所以下面的分析都是基于带锁存器的。

- 带锁存器的门控时钟的时序约束如下所示。需要A信号在时钟上升和下降沿分别满足setup和hold的时间约束。

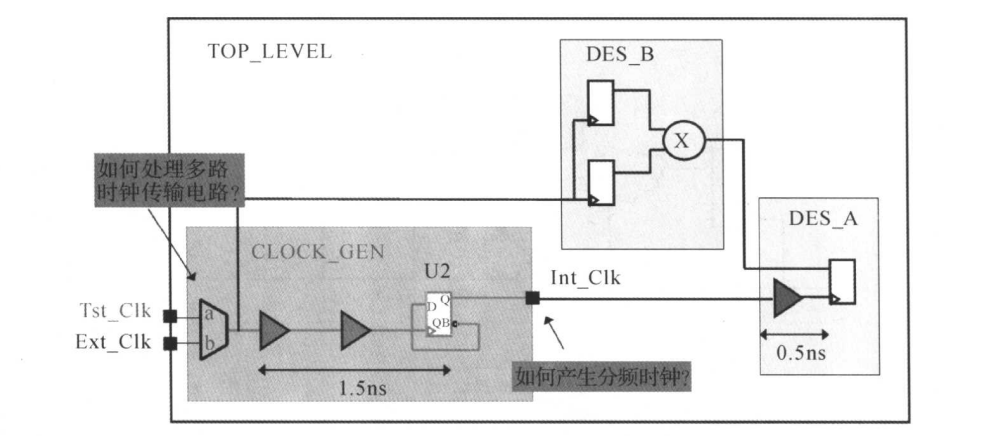

5. 分频电路和多路传输电路的时钟约束

- 注意,在模块划分时,需要注意将时钟电路和核心功能电路划分成不同模块。

- 不仅可以对时钟逻辑更好的控制和分析,而且简化了其他模块的输入时钟约束。

- 多路传输

- 上图中,CLOCK_GEN是通过多路时钟MUX选出的,如果我们不加约束去指定,那么DC会自己选择一个。

- 我们可以加约束如下,去掉引脚a到引脚y的时间弧,此时DC认为选择了Ext_Clk.

set_disable_timing CLOCK_GEN/U1 -from a -to y

- 分频电路

- DC并不能推导出分频时钟的波形,时钟信号可以通过任何的组合逻辑电路,但是终止于寄存器。因为DC并不知道寄存器的输出是时钟还是非时钟信号。

- 建议的定义分频时钟脚本:

create_clock -period 50 [get_ports Ext_Clk] create_generated_clock -name Int_Clk \ -source [get_pins CLOCK_GEN/U2/CP] -divide_by 2 \ [get_pins CLOCK_GEN/U2/Q] set_clock_latency -source 1.5 [get_clocks Int_Clk] set_clock_latency 0.5 [get_clocks Int_Clk] - 注意:对于CTS综合之后,我们不需要使用set_clock_latency为时钟建模,使用下面脚本。

set_propagated_clock [list [all_clocks] [get_generated_clock *]]

浙公网安备 33010602011771号

浙公网安备 33010602011771号