低功耗设计

- 参考

1. 功耗源

- 浪涌

- 浪涌电流也称为启动电流,指器件上电时产生最大瞬时输入电流。浪涌功耗主要由浪涌电流引起的。

- 静态功耗

- 电路中晶体管漏电流导致的功耗。

- 工艺进步,供电电压越来越低,单元的阈值电压也越来越小;导致漏电流越来越大,静态功耗占比越来越大。

- 动态功耗

- 主要分为翻转功耗和短路功耗。

- 翻转功耗

- 对输出负载电容进行充放电引起的,

- 计算公式:$ P_{dynamic} = S*C_L*V_{dd}^{2}*f_{clk}$

- 其中,$ C_L$为门寄生电容,$S$为输出的平均翻转次数。

- 可以看到,功耗和供电电压是平方函数的关系。

- 降低翻转功耗

- 降低电压:但是低电压会导致设计时序变差,导致难以满足时序要求。

- 减小负载电容大小。

- 降低信号翻转率。

- 短路功耗

- 考虑到信号翻转不可能瞬时完成,PMOS和NMOS不可能总是一个截止另一个导通,两者存在都导通的情况,那么此时VDD和GND之间便有了通路,形成了短路电流。

- 计算公式:$ P_{short} = t_{sc}*V_{dd}*I_{peak}*f_{clock}$

- 其中$t_{sc}$是短路电流持续时间,$I_{peak}$是总的短路电流。

- 一般短路功耗占比较小,可以忽略。

2. 低功耗电路设计和优化

2.1 门控时钟

- 可以在基于DC的Power Compiler中执行下面指令插入门控时钟。

insert_clock_gating - 门控时钟减少了时钟的开关行为,节省了功耗。

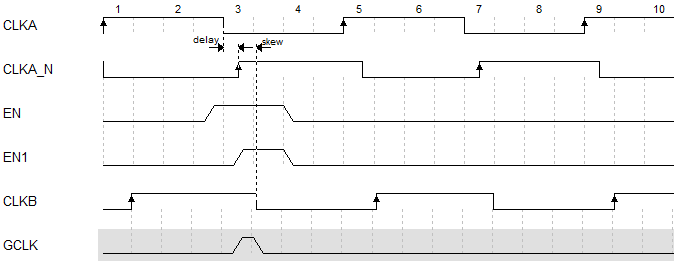

- 门控时钟分类

- 离散和集成

- 离散的是Power Compiler用工艺库中的锁存器和其它逻辑门搭的。

- 集成的是工艺库中一个门控单元,是库商创作的。

- 是否带锁存器

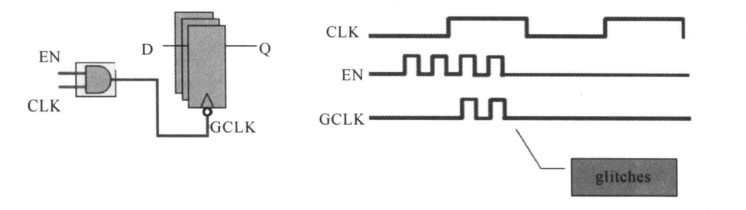

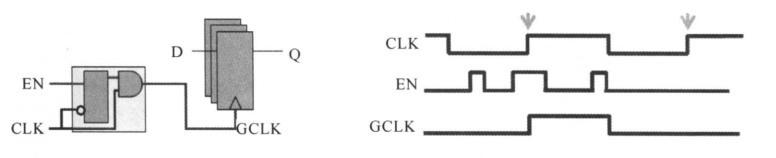

-

带锁存器的门控时钟可以一定程度上过滤毛刺。

-

但是当clock skew太大时,输出还是会有毛刺。

-

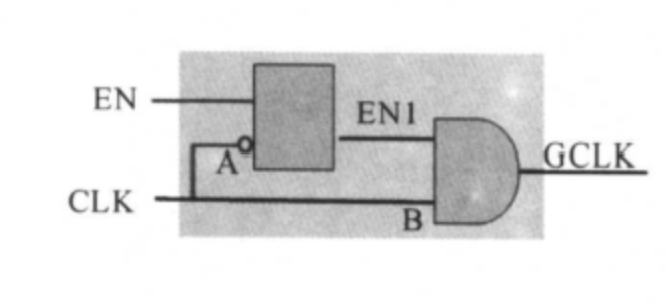

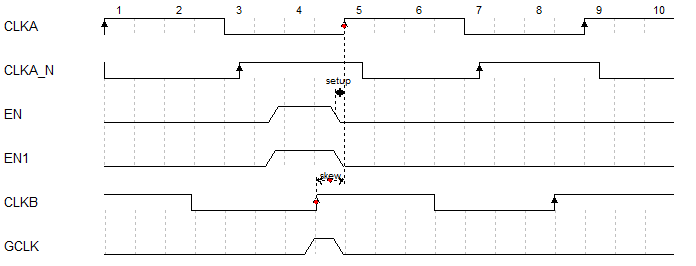

第一个波形中:delay为CLKA和CLKA_N之间的时间差,skew为CLKA和CLKB之间的时间差,且到A的时钟快于到B的时钟;当delay<skew时,会出现毛刺。波形图如下所示。

-

第二个波形中:到B的时钟快于到A的时钟,如下图所示,也会产生毛刺。

-

-

可以通过两种方式管理Clock Skew,使门控单元输出没有毛刺。

- 使用集成的门控单元,前面介绍了这个单元取自工艺库,已经对skew做了控制。

- 若使用离散的门控单元,在做布局时可以将门控单元和锁存器摆放靠近一些。

-

- 离散和集成

- 门控时钟单元的扇出越大,到达寄存器的延迟就越大。所以需要控制门控时钟单元的扇出大小。

2.2 操作数分离

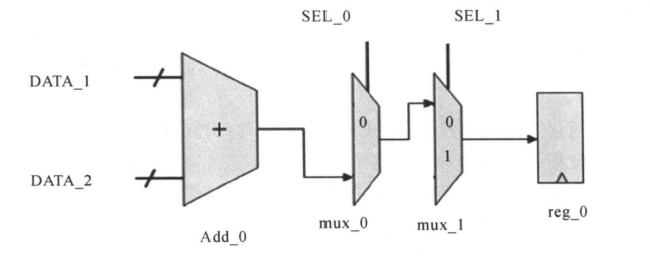

- 首先观察下图,当SEL_0和SEL_1为某些值时,加法器的运算结果对于输出没有影响,所以此时可以让加法器不工作,来降低功耗。

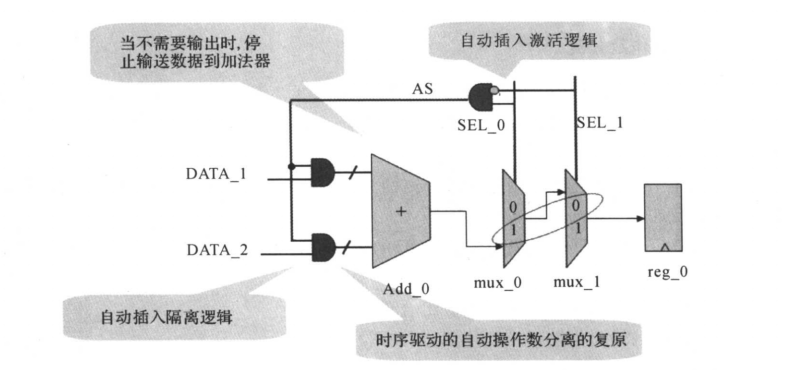

- 可以添加下面的电路,实现未选中加法器输出时,加法器不工作。

- 添加的隔离逻辑可能会让时序变差。

2.3 门级电路的功耗优化

2.3.1 优化对象及优先级

- 门级电路的功耗优化是对已经映射到网表进行功耗的优化。

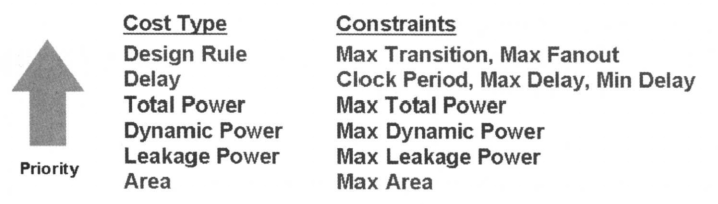

- 逻辑综合的优化策略是存在优先级的,如下图所示。

- 优化首先满足更高优先级的约束,进行低优先级约束的优化不能以牺牲更高优先级的约束。

2.3.2 多阈值电压优化漏电功耗

- 阈值电压越高的单元,漏电功耗越低,但门延迟越长。

- 阈值电压越低的单元,漏电功耗越高,但门延迟越短。

- 可以对关键路径使用低阈值电压的单元,改善时序。非关键路径使用高阈值电压的单元,以降低静态功耗。

2.3.3 动态功耗优化

- 读入含有开关行为的SAIF文件,用于约束动态功耗的优化。

- SAIF:用于仿真器和功率工具之间交换信息的ASCII文件。

- 更多关于SAIF/VCD分析功耗的方法在后面会详细介绍。

- 高翻转率信号,尽可能降低其负载电容,可以从以下几个方式入手

- 对于高频连线,在不影响时序的前提下,更换门单元,降低其负载,有助于降低其功耗。

- 缩短高翻转率net长度,降低net电容。

- 将高翻转率连线靠近输出端(可以通过因式分解重组逻辑实现)。

- 将高翻转率的连线连接到电容值小的引脚上。

- 插入buffer,减少门输出负载,并使buffer后级电路转移时间变小。

- 更详细内容可以看《专用集成电路设计实用教程》。

2.3.4 多个供电电压

- 对工作频率高的模块,使用供电电压高的电源。对工作频率低的模块,使用供电电压低的电源。

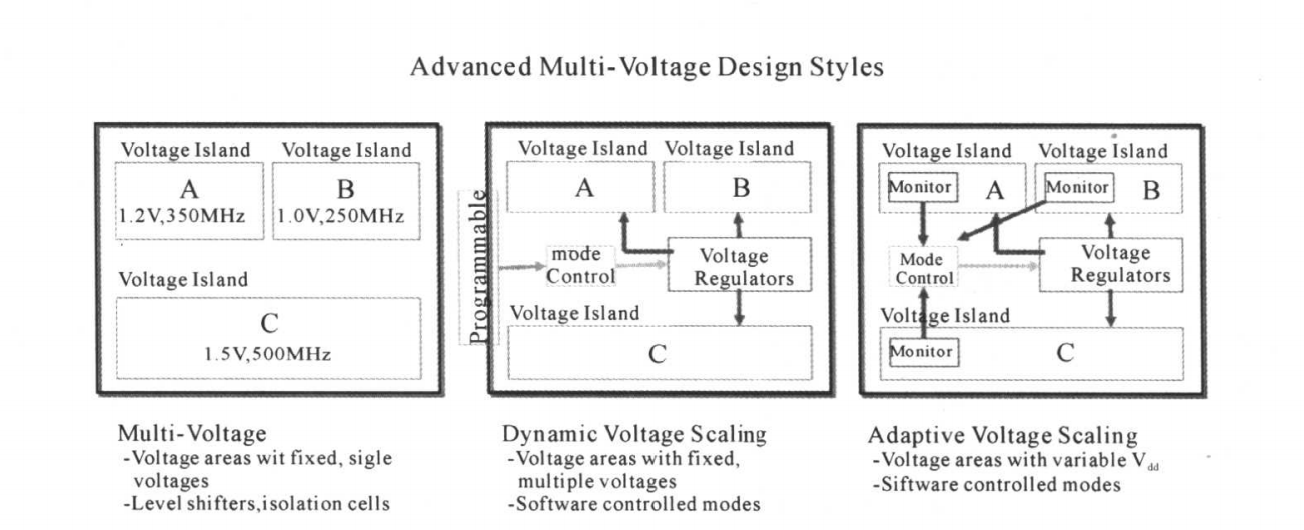

- 主要有下面三种设计风格。

- 图1:各电压区域有固定的单一电压。

- 图2:软件控制各个区域选用哪种电压,但各个电压区域仍有固定电压。

- 图3,采用自适应方式,各电压区域有可变的电压,软件控制选用电压。

2.3.5 电源门控

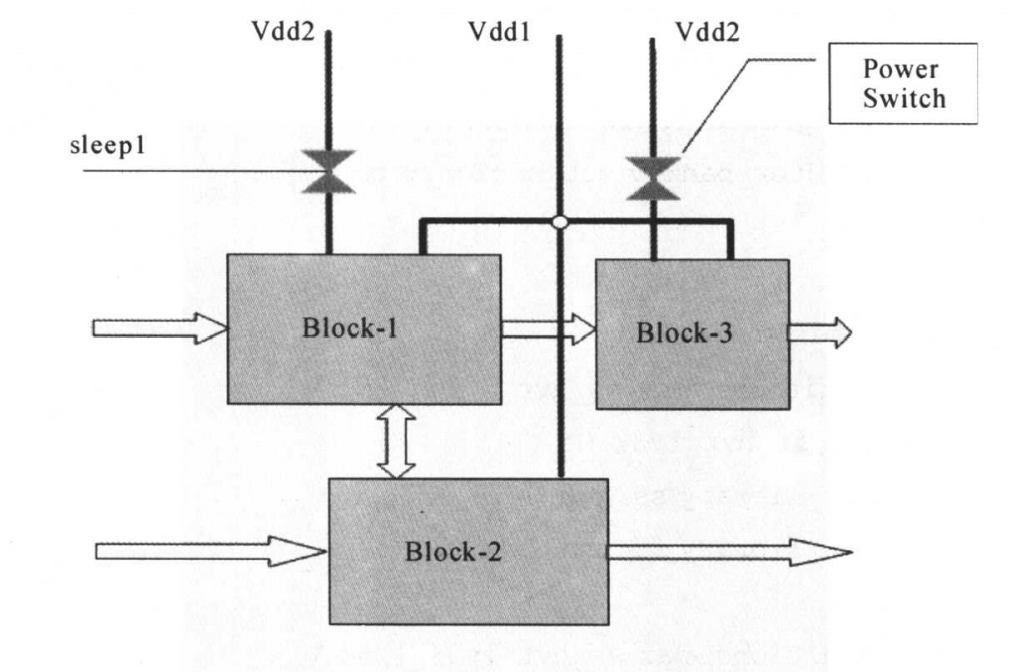

- 如下图所示,当一个模块一段时间不工作,可以关掉它的供电电源。

- 断电后,模块进入睡眠模式,只有静态功耗,较小。

- 唤醒时,为了让模块尽快恢复工作模式,需要保持断电前的状态,可以使用寄存器来记忆状态。

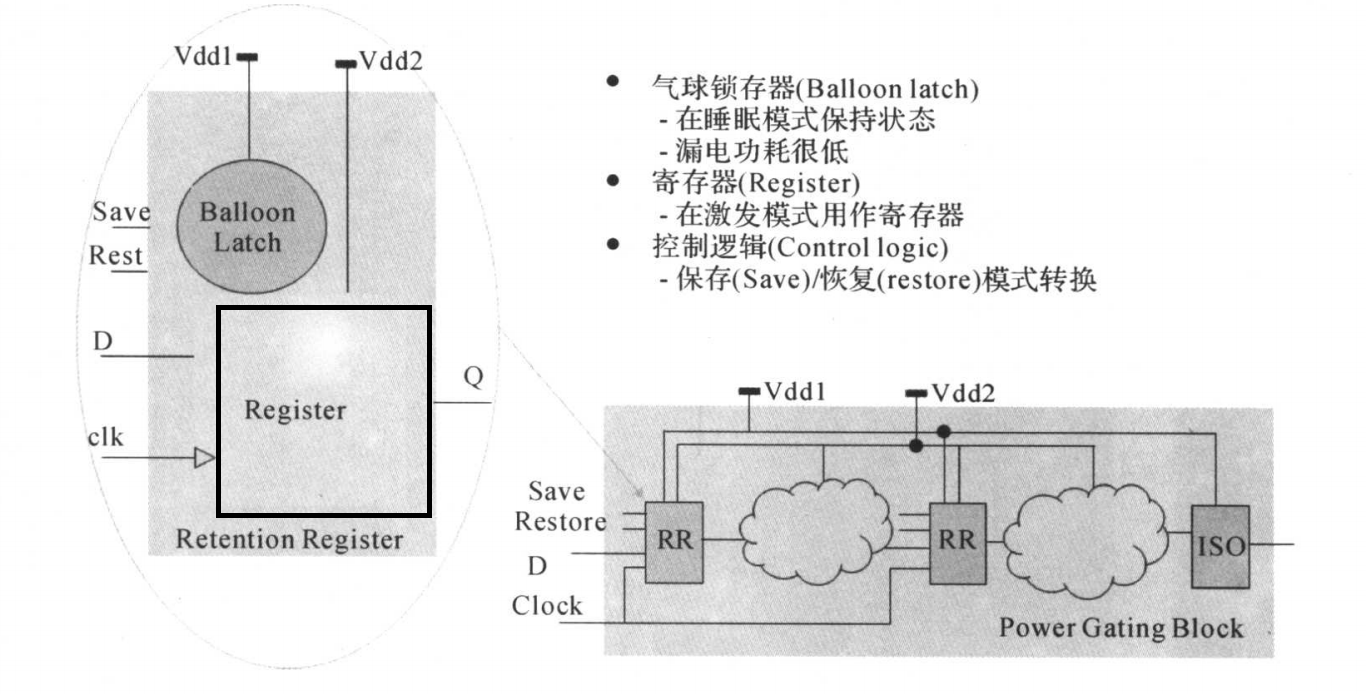

- 实现电路如下所示。

- 睡眠模式

- 寄存器的电源Vdd2被切断,它的漏电功耗极小,此时只有锁存器处于工作状态,寄存器的值保存在锁存器里,由于锁存器是用高阈值电压晶体管组成的,所以漏电功耗很低。

- 唤醒模式

- Restore信号被激活时,寄存器的电源Vdd2被加上,保留在锁存器里的值被载入到寄存器。

- 注意:电源门控模块的输出端需要用隔离单元。

- 因为在睡眠模式时,模块的输出为一个不确定值。为了保证在睡眠模式下,下一级的输入不会悬空,插入隔离单元,提供一个1或者0的输出,使下一级的输入为确定的逻辑值。

- 睡眠模式

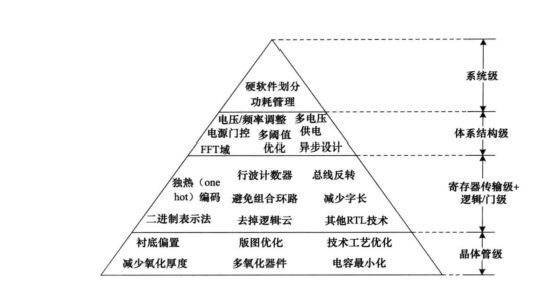

3.各个设计层次降低功耗

- 不同设计层次有不同低功耗的设计方法,如下图所示。层次越高,对功耗的降低越有效。

浙公网安备 33010602011771号

浙公网安备 33010602011771号