前端 Verilog HDL优化

1. if - else

1.1 if-else 硬件结构映射及优化

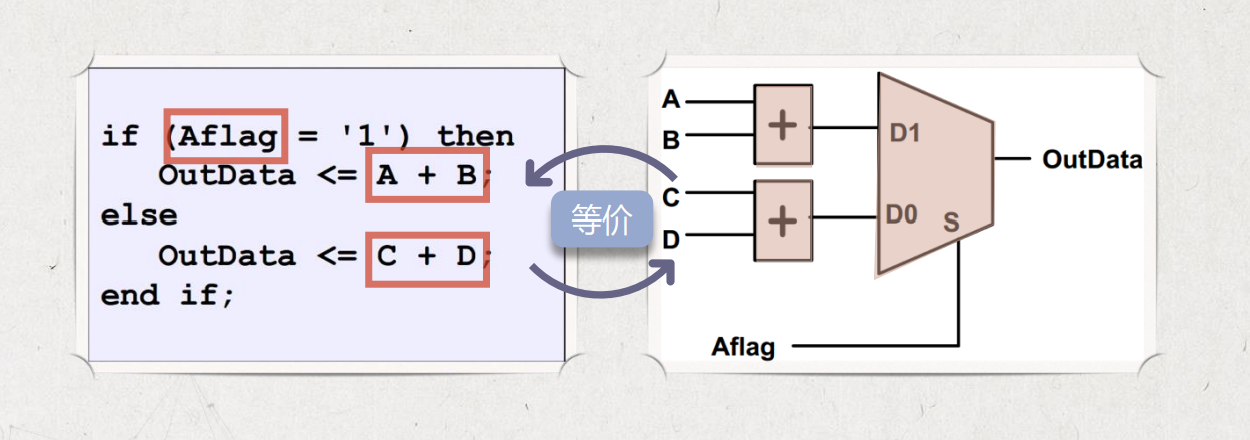

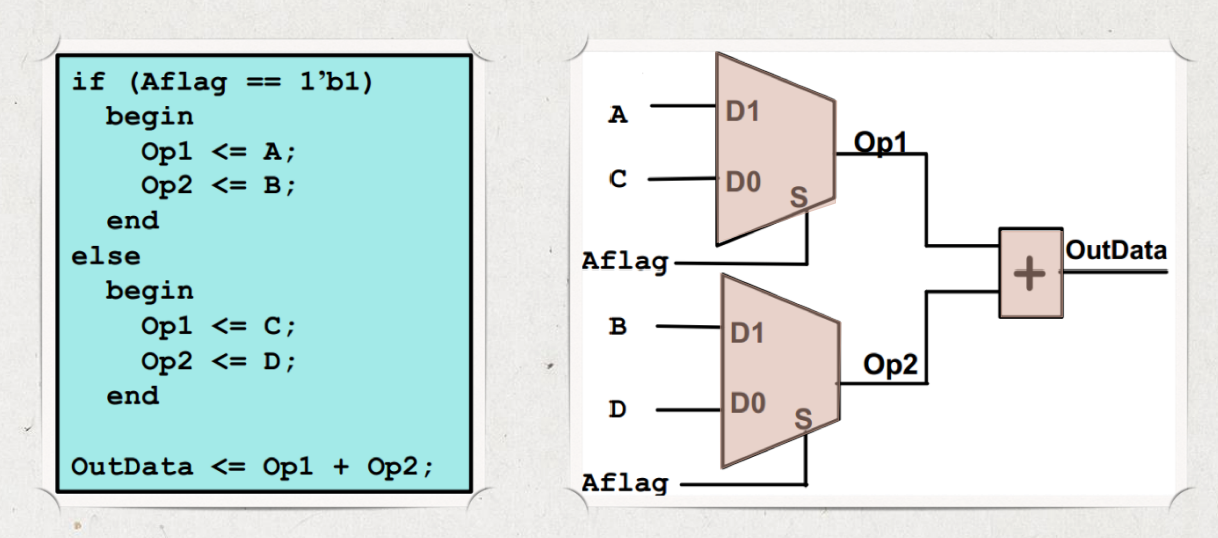

- 上下两个代码实现的是同一个功能,上面是先加后选,后下面则是先选后加。

- 但是下面减少了一个加法器,减小了硬件的面积。

1.2 if/case 优先级判断

-

if - else是有优先级的判断结构。

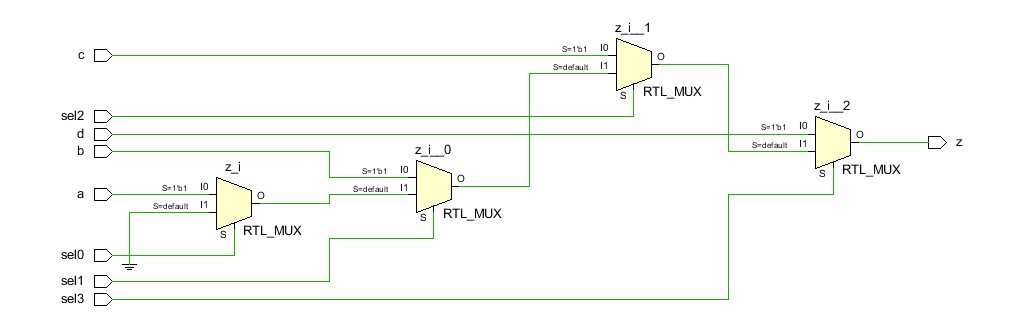

always@(a or b or c or d or sel0 or sel1 or sel2 or sel3) begin if(sel3) z = d; else if(sel2) z = c; else if(sel1) z = b; else if(sel0) z = a; else z = 0; end- 第一个if具有最高的优先级,vivado综合出的电路如下所示。

- 第一个if具有最高的优先级,vivado综合出的电路如下所示。

-

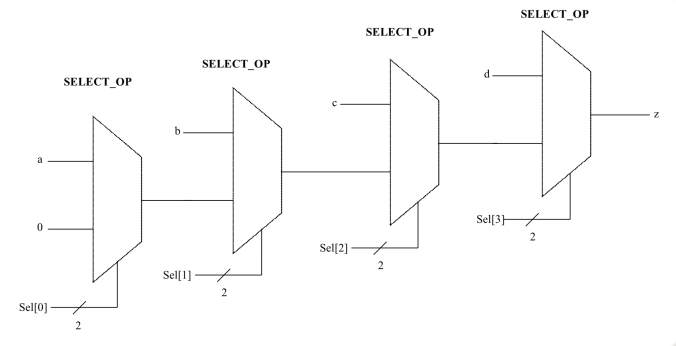

对于多if语句,无else,电路如下所示,具有优先级的判断结构。

- 下图可以看到,最后一级的选择信号具有最高的优先级。

- 对于某些设计,有些信号要求先到达,如关键使能信号、选择信号等。有些信号要求后到达,如慢速信号,有效时间长的信号。

- 此时可以将最高优先级(如sel[3])给最迟到达的关键信号;可以一定程度上避免毛刺的出现。

- 但考虑到if-else结构也可以实现该功能,所以在设计中尽量避免使用多if语句结构。

- 与前面介绍的if-else类型相同。

always @(a or b or c or d or sel0 or sel1 or se12 or se13) begin z=0; if (sel0) z=a; if (sel1) z=b; if (se12) z=c; if (se13) z=d; end

- case 无优先级判断

- 这篇博客中介绍在Quartus下实践发现,如果分支包含所有的取值情况时,且互相不重复,那么各个分支的优先级是一样的。如果分支存在重复情况,那么前面分支的优先级更高。

- 可以使用下面的原语告诉综合器,设置为并行结构无优先级。

//synopsis paralle_case

2. 优化策略

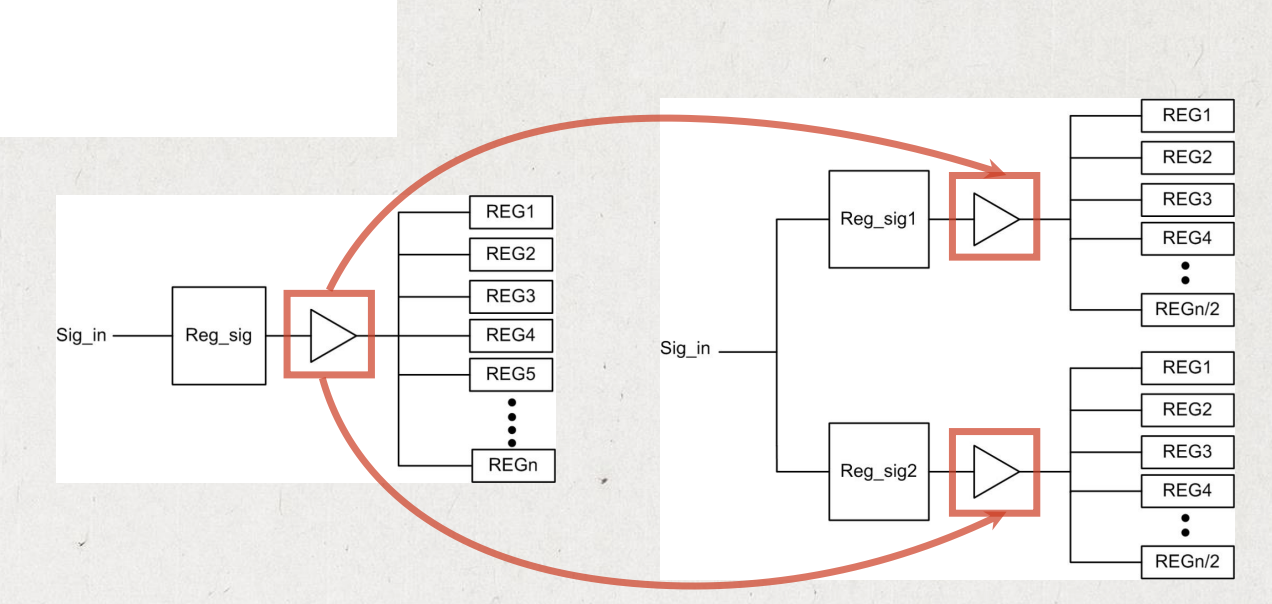

2.1 逻辑复制

- 通过逻辑复制,降低扇出,减少该信号的传播延迟。

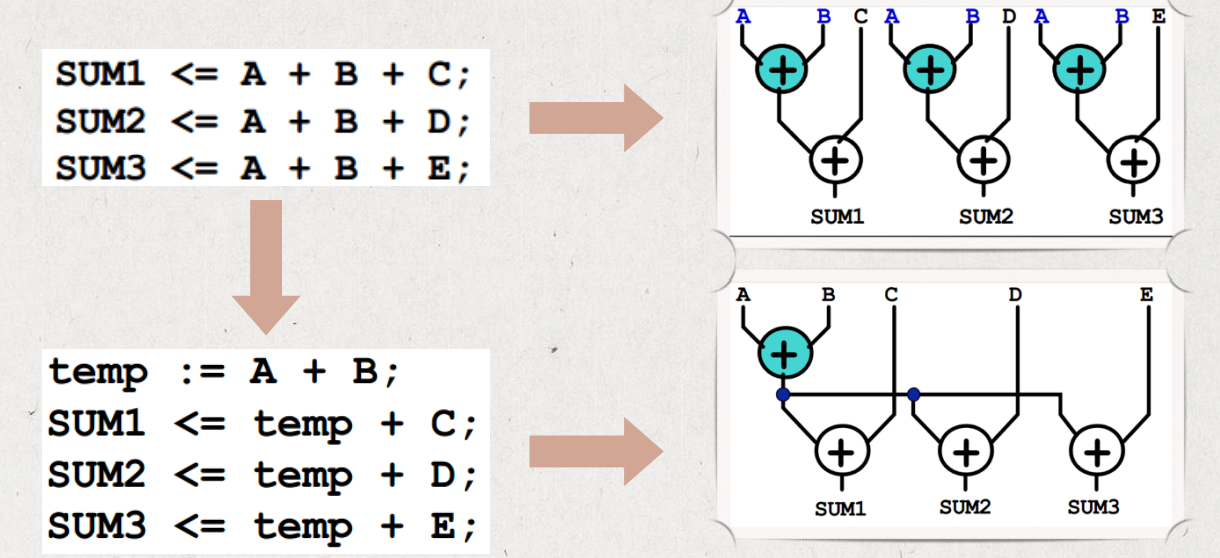

2.2 资源共享

- 共同运算单元可以资源共享,节省面积。

- 尽管逻辑综合工具也会在综合过程中采用资源共享的方式进行优化,但是综合策略是有限的;因此在编写RTL时,也需要尽量考虑共享,而不是将这项工作完全留给综合工具。

2.3 判断是否信号所有bit都需要参与操作

- 对于一些逻辑操作,可能只需要信号其中的几bit,这样可以节省部分资源。

- 例如:访问一RAM的地址有8比特,而写入操作时从0开始,每隔32个地址写入一个值,地址的产生可以有两种写法。

addr <= addr + 32; //或采用下面方式 addr[7:5]<=addr[7:5]+1; addr[4:0]<=addr[4:0]+0;

2.4 在RTL编码考虑功耗

- 低功耗的设计见这篇博客.

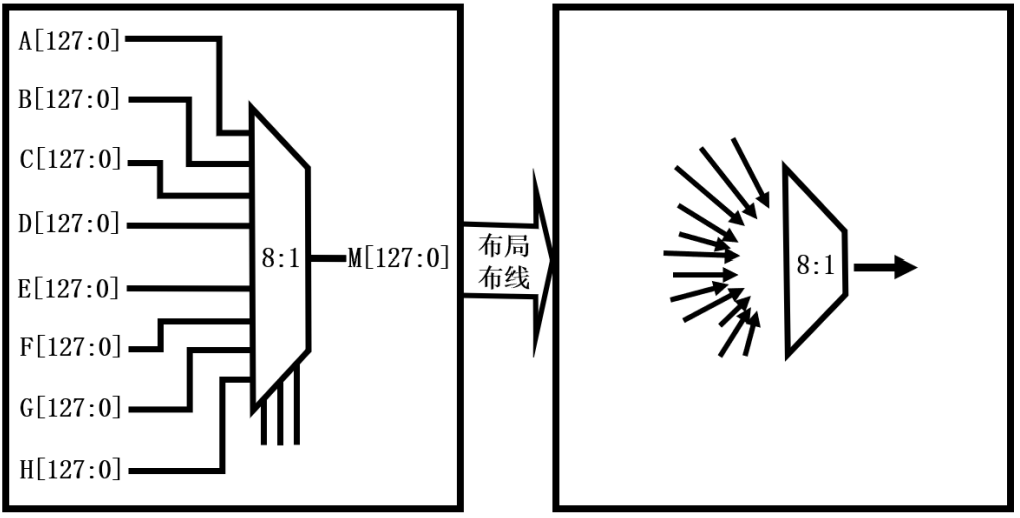

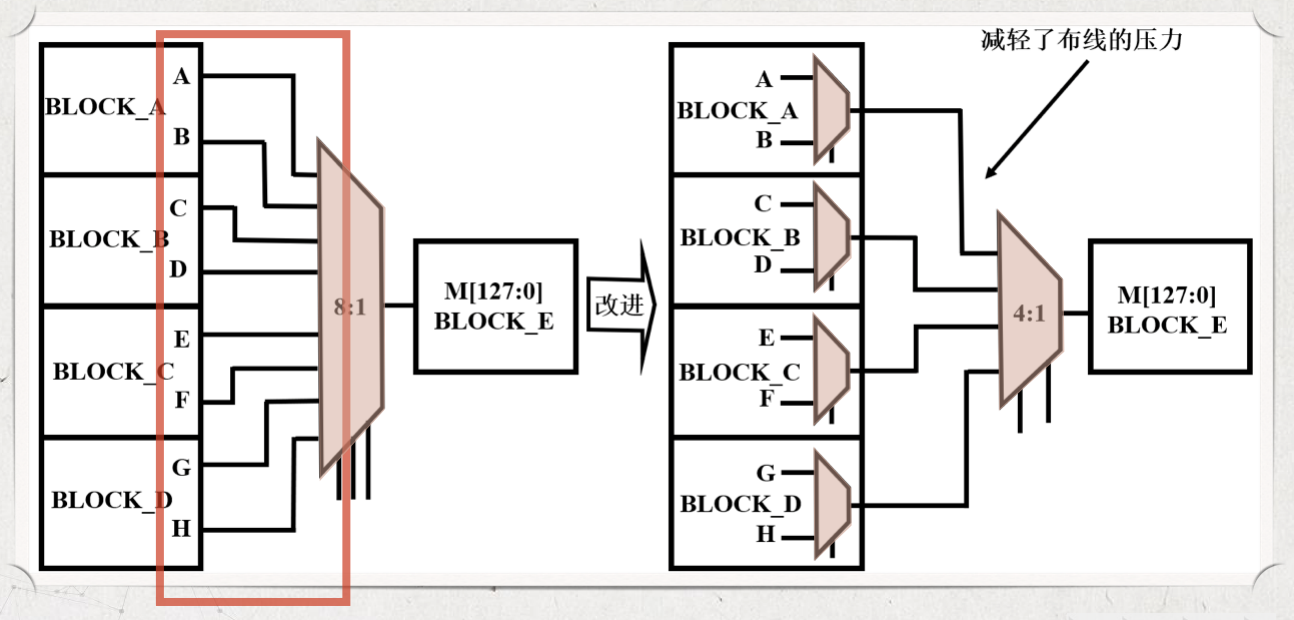

2.5 在RTL编码考虑布线

-

定义热点:是指在一定面积内占用大量布线资源。

-

例如,大扇入MUX。

- 可以将大扇入MUX分解成多个小扇入的MUX。

3. 面积换速度

3.1 串并转换

- 假设输入数据流速率是450Mbit/s,而FPGA数据处理速度最大是150Mbit/s。可以通过复制3个子模块,进行并行处理,处理完成之后再进行“并串转换”。以输出速率为450Mbit/s输出。

3.2 乒乓操作

- 可以看这篇博客.

3.3 流水线

- 可以看这篇博客.

浙公网安备 33010602011771号

浙公网安备 33010602011771号