I2S 协议

- 参考

- NXP 《I2S bus specification》

- NXP 《I2S在Kinetis上的应用 》

- https://www.python100.com/html/R62183SDTAU0.html

- https://blog.51cto.com/u_15459030/5225825

- I2C相关内容见tag.

1. I2S概述

1.1 为什么需要I2S

- I2S是I2C的变种,全称:InterIc-Sound. 专门为传输音频数据而设计的。

- I2S 相较于I2C和SPI有以下优点

- 更低的延迟:由于I2S数据传输是连续的,不需要等待ACK信号的回复,I2S只需要使用WS和SCK信号进行数据的同步;响应速度更快。

- 更高的精度:I2C一次可以传输8位的数据,但是I2S可以传输16/24位的数据,对于高精度的音频设备,I2S能够满足要求。

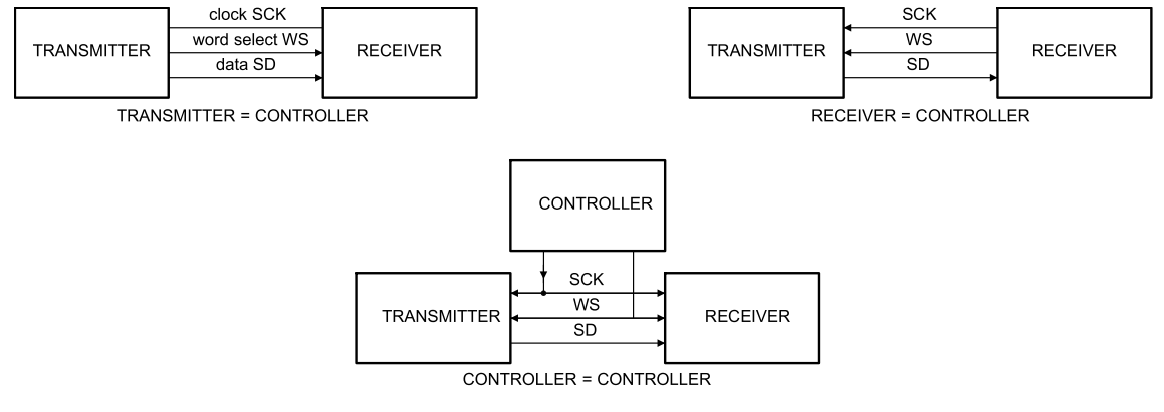

1.2 I2S 三条总线

- 之前介绍I2C有两条总线:SCL/SDA。而I2S有三条总线如下。

- SCK(Continuous Serial Clock):串行时钟,也称为位时钟BCLK。

- SCK的时钟频率 = 声道数 * 采样频率 * 采样位数。

- WS(Word Select):字段(声道)选择信号,也称为帧时钟LRCK。

- 其频率等于采样频率。

- 在I2S模式下:WS=1,表示传递的是右声道数据。WS=0,表示传递的是左声道数据。后面有介绍,其它模式不同。

- SD(Serial Data):串行数据。

- SCK(Continuous Serial Clock):串行时钟,也称为位时钟BCLK。

- 控制器(Controller)产生SCK信号和WS信号,控制器可以是Transmitter也可以是Receiver,也可以是单独设计的控制模块。

1.3 I2S的三种操作模式

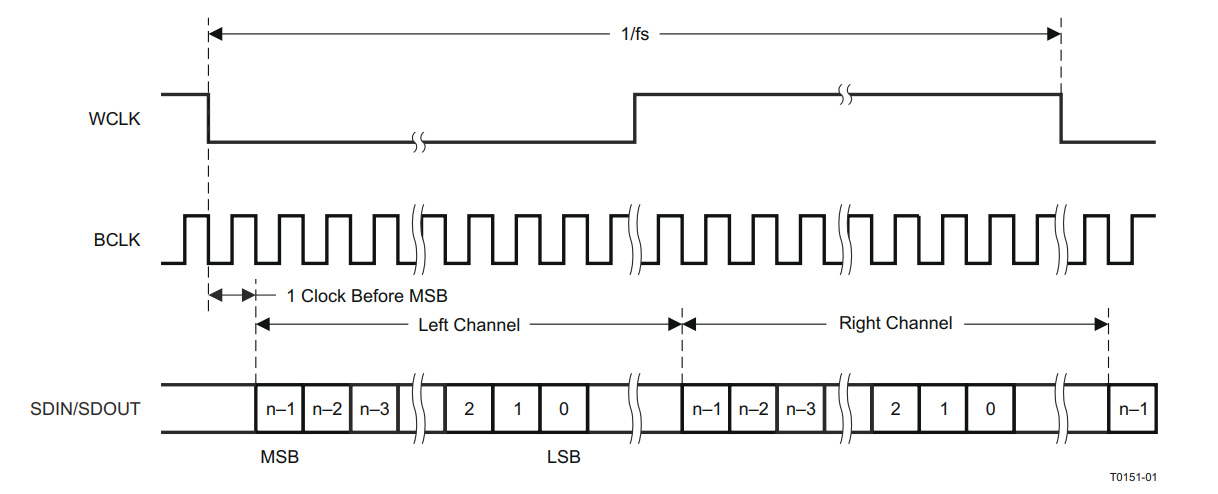

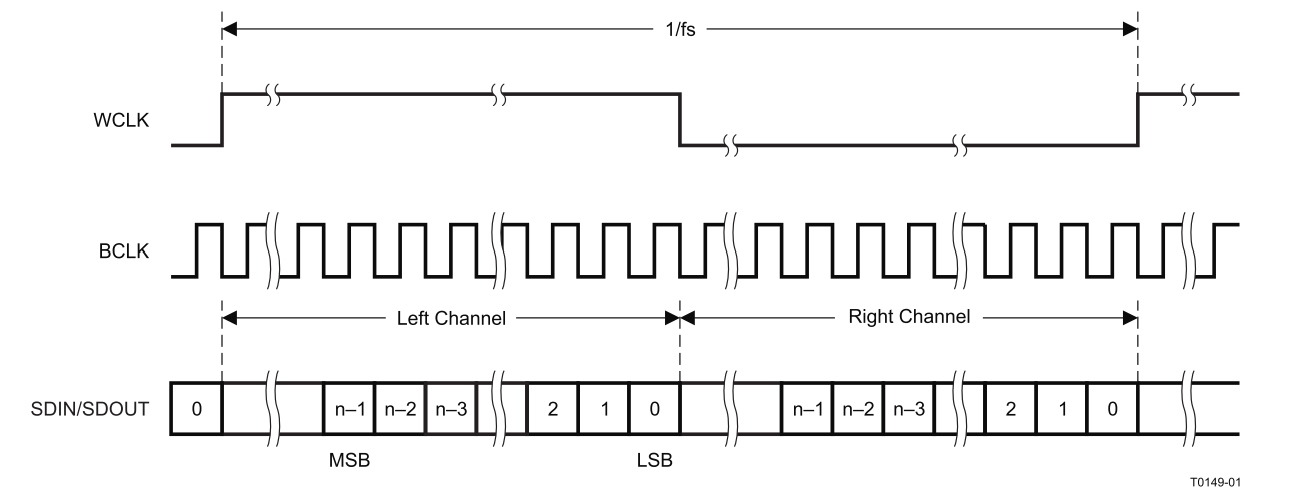

- 图片来自TI的TLV320AIC3104的数据表,其中WCLK为LRCLK信号,BCLK为SCK信号。

- 无论哪种模式,串行数据都是以二进制补码进行传输的,且先传输MSB,LSB的位置取决于I2S的位宽,长会被截断,短会被补零。

- 根据下面的波形可以看到:I2S模式,WS=0->左,WS=1->右;而左对齐和右对齐和I2S模式规定相反。

- 不同的模式决定了解码方式也不同。

- 根据SD和WCLK情况可分为三种模式:

- I2S模式

- 在WCLK下降沿之后的一个BCLK周期的上升沿采到的数据有效。

- WCLK在BCLK下降沿变化,发送方在BCLK下降沿改变数据,而接收方在BCLK上升沿采样数据。

- 左对齐模式

- 相较于I2S模式,没有延迟一个BCLK周期。

- 不需要关心数据的长度,只会对LSB进行处理,截取/补零;但是MSB不会有问题。

- 发送方在BCLK下降沿改变数据,而接收方在BCLK上升沿采样数据。

- 右对齐模式

- 不足:接收设备需要事先知道传输数据的长度,否则可能会导致MSB被截断

- 不足:接收设备需要事先知道传输数据的长度,否则可能会导致MSB被截断

- I2S模式

- 对于I2S模式和左对齐模式,可以允许发送端和接收端数据长度不同,因为接收端和发送端可以进行相应的截断和补0.

- 为了保证数据音频信号的正确传输,发送端和接收端最好使用相同的数据格式和长度。

2. I2S 应用

- 注意:这里只讨论I2S模式,不讨论左对齐/右对齐模式。

- 讨论基于DMA和中断的乒乓缓冲区方案,旨在降低用于处理音频数据流的CPU开销。

- 为什么需要该方案

- 采样率一般会在8KHz-48KHz之间,甚至可以更高。如果使用CPU去处理每个中断,那么系统效率会非常低。

- 另外大部分的音频算法会累积音频流中的数据形成缓冲数据块,之后再对缓存数据块进行处理。

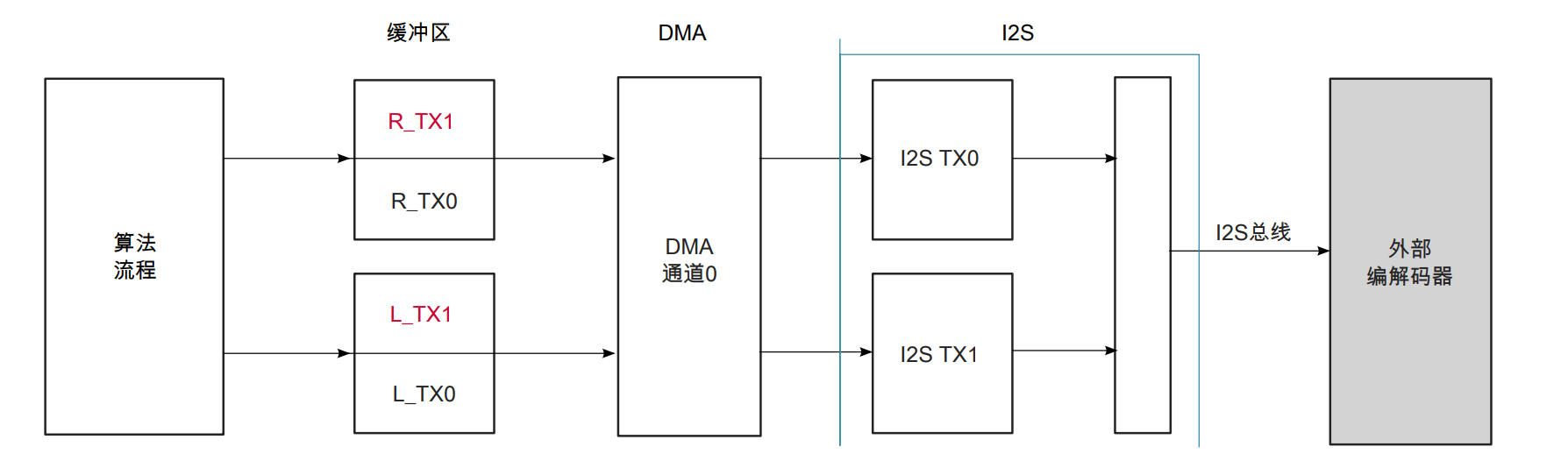

2.1 方案概述

- 具体方案结构框图如下图所示。

- 其中R和L分别代表右通道/左通道。每个通道都有用于乒乓操作的两个缓冲区(红色和黑色)。

- 乒乓相关知识可以看这篇博客。

- 我对框图的工作模式理解是

- 前面介绍,缓冲区被划分为四块;我们这里看红色和黑色两部分。红色部分我们使用DMA将其传送到I2S TX模块。

- 根据要求假设N为缓冲区中采样数据数量,DMA传送了N个采样数据之后,DMA会向CPU发起一个中断。

- 中断期间,CPU执行音频解码算法之后获得的输出数据,并将输出数据填充到缓冲区。

- 可以看到存在一个乒乓的工作模式:

- T1:中断:CPU计算完成,将数据送到缓冲区R_TX0。与此同时DMA在搬移R_TX1的数据。

- T2:DMA搬移结束后再次触发中断,此时DMA继续搬移R_TX0中的数据。CPU完成计算,并将数据送到缓冲区R_TX1中。

- 依次类推,形成乒乓的工作模式。

- 前面介绍,缓冲区被划分为四块;我们这里看红色和黑色两部分。红色部分我们使用DMA将其传送到I2S TX模块。

- 注意:考虑到音频信号具有较强的实时性要求,因此,所有计算都必须在下个中断发生之前完成,否则会导致系统故障。

- 其中R和L分别代表右通道/左通道。每个通道都有用于乒乓操作的两个缓冲区(红色和黑色)。

2.2 I2S 的 FIFO 特性

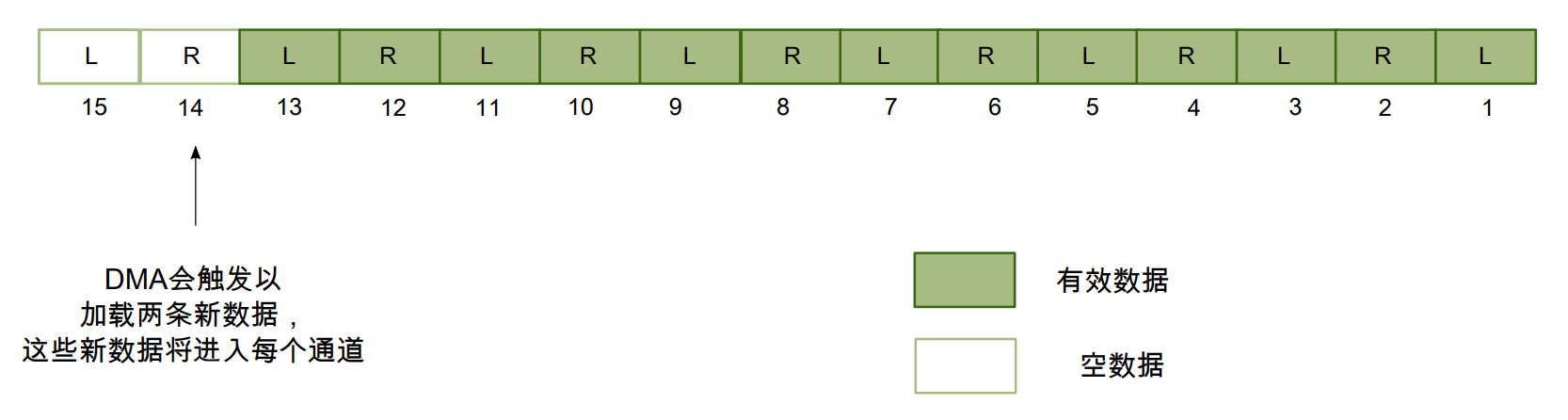

- I2S 的 FIFO 从DMA中读数据,FIFO中的数据会交替发送到左右通道;判断依据可选择FIFO中是否存在空数据。

- 如下图所示,当FIFO的空数据计数为2时,就会让DMA加载一条数据进入左通道,一条数据进入右通道。

- 如下图所示,当FIFO的空数据计数为2时,就会让DMA加载一条数据进入左通道,一条数据进入右通道。

2.3 DMA 和中断 配置

- 2.1节中有介绍到DMA和中断CPU处理之间的乒乓工作模式。下面会依据实例详细介绍。

- 下图可以看到,共有四个数据块,每个数据块有四个采样,每个采样都有四个字节。

- DMA的访问顺序是左右通道交叉,如:0x00,0x20,0x04,0x24...

- 乒乓操作实现

- 当DMA读取地址经过0x00,0x20...到达0x2c时,TX0内的所有数据都已经发送完毕,发起一个中断。

- 随后,CPU进行算法计算,并将数据填充到BLOCK0和BLOCK2中;与此同时,DMA处理BLOCK1和BLOCK3。

- 当DMA到达地址0x3c时,会发起另一个中断。

- 随后,CPU进行算法计算,并将数据填充到BLOCK1和BLOCK3中;与此同时,DMA处理BLOCK0和BLOCK2。

浙公网安备 33010602011771号

浙公网安备 33010602011771号