Glitch free 时钟切换技术

- 参考

1. 应用场景

- 异步电路,纯组合逻辑。

- 使用组合逻辑进行不同时钟切换。

2. 解决方案

2.1 相关时钟源毛刺保护

- 相关时钟源:同源时钟,存在整数倍数频率关系的时钟。

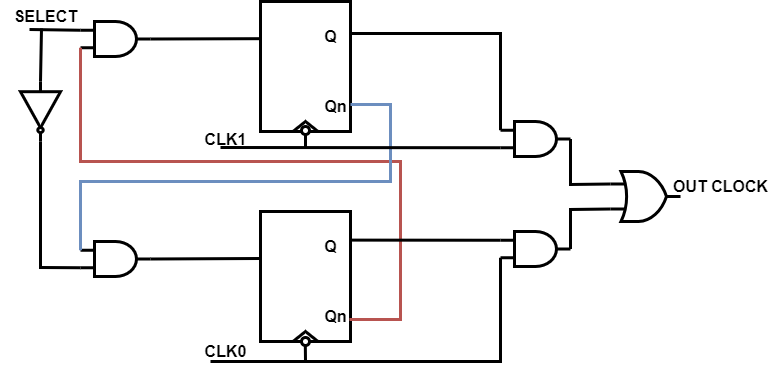

- 采用下降沿采样控制信号SELECT信号的原因

- Q只会CLK下降沿发生变化,而此时CLK时钟为0,两者相与一定为0,在CLK时钟为高电平时,才会将Q的值同步到OUT_CLOCK处。

- 个人认为Q端输出和CLK做与操作部分和门控时钟原理一样,可以看这篇文章。

- 简单说,对于AND门,如果控制信号在时钟上升沿变化,那么会导致时钟被截断。

- 对于用NAND Gate或者AND Gate实现的门控时钟,控制信号只能在时钟的低电平处进行跳变;对于用OR Gate或者NOR Gate实现的门控时钟,控制信号只能在时钟的高电平处跳变。

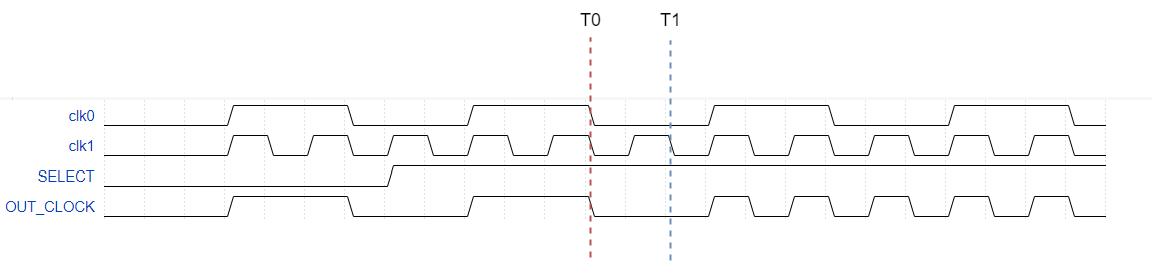

- 具体分析如下波形所示。

- SELECT初始值为0,此时由于上面寄存器DFF1输入值为0,所以DFF1的Qn输出值为1,那么下面寄存器DFF2的输入值为1,输出Q值为1;根据电路可以推出:输出OUT_CLOCK等于CLK0。

- 当SELECT信号被拉高,但在T0时DFF2寄存器才检测到SELECT信号被拉高,输出端Q一直等于0.此时下面电路相当于被关闭。

- 在T0之后的clk1的第一个下降沿,也就是T1时刻,DFF1输出端Q被拉高为1,此时输出OUT_CLOCK等于CLK1。

- 完成两个时钟的切换,且没有毛刺。

- 需要注意,DFF0和DFF1寄存器复位初始值都应该为0.

2.2 不相关时钟源毛刺保护

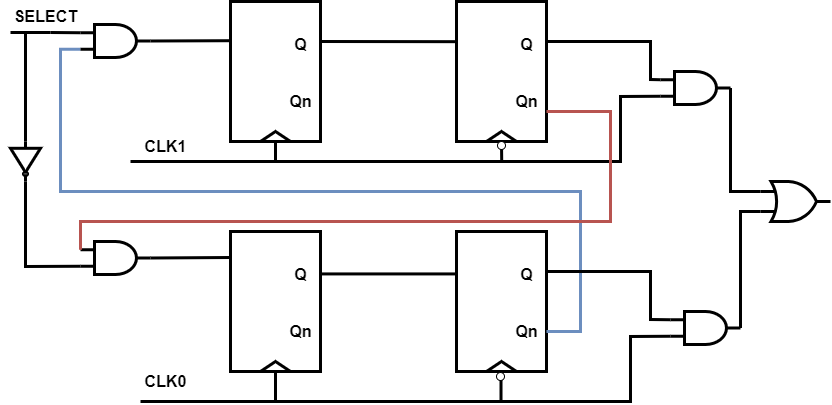

- 2.1中介绍的电路并不适用处理异步信号。下图与上图只增加了一级两个上升沿的DFF,来避免出现亚稳态。

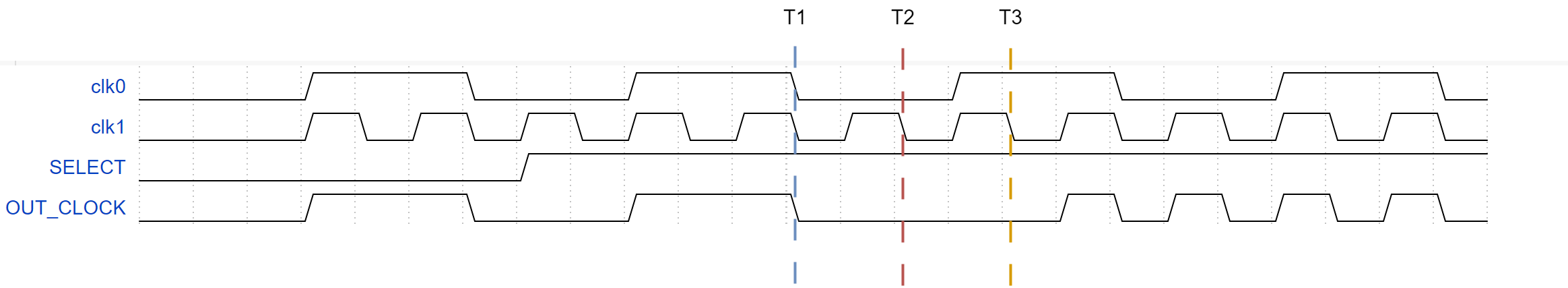

- 其它原理与2.1节完全相同,仿真波形如下图所示。

浙公网安备 33010602011771号

浙公网安备 33010602011771号