跨时钟域处理

- 参考

1. 多级寄存器串联打拍

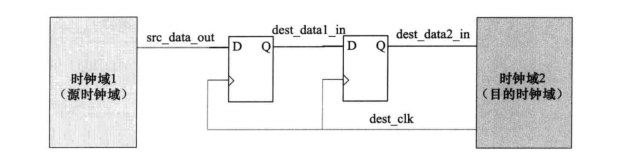

- 电路结构如下所示,由两个或多个触发器串联起来。

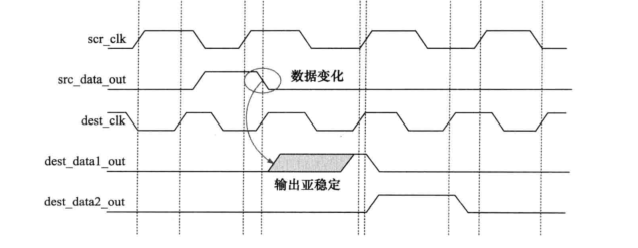

- 波形图如下所示,在dest_clk上升沿检测时,src_data_out数据信号正发生变化,此时无法确定采样的是1还是0,出现亚稳态。但是第二个寄存器可以采样到稳定的值。

- 这种寄存器打拍的方式只能降低亚稳态出现的概率,并不能直接去亚稳态。对于时钟频率高的设计可能信号从亚稳态进入稳定状态不止一个周期,就需要多加几级同步寄存器。

- 缺点:会增加电路整体的延时。

2. 脉冲同步器(快时钟域到慢时钟域)

- 使用场景

- 适用于不同时钟域之间只传输脉冲信号,使用异步FIFO过于浪费。

- 如果快时钟域信号长度过于窄,那么慢时钟域采样时可能出现丢失信号的情况。

- 实现

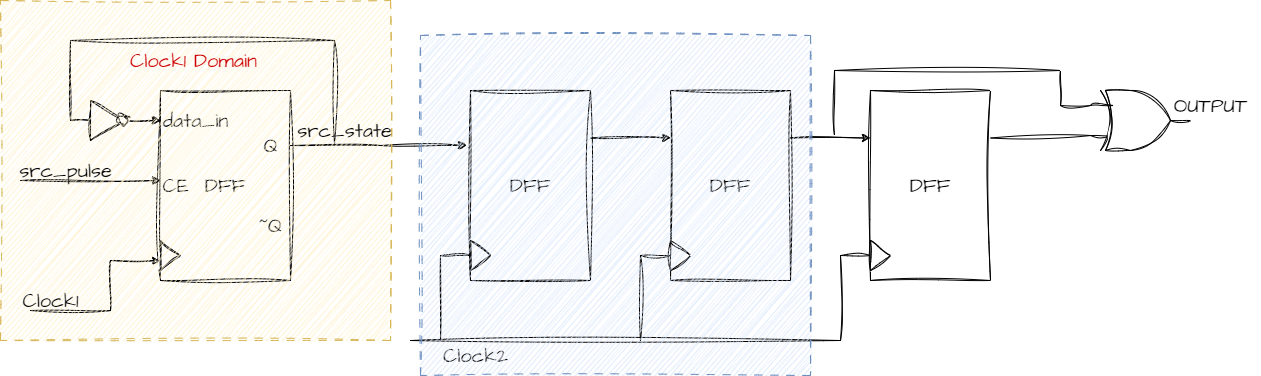

- 实现电路结构如下所示。

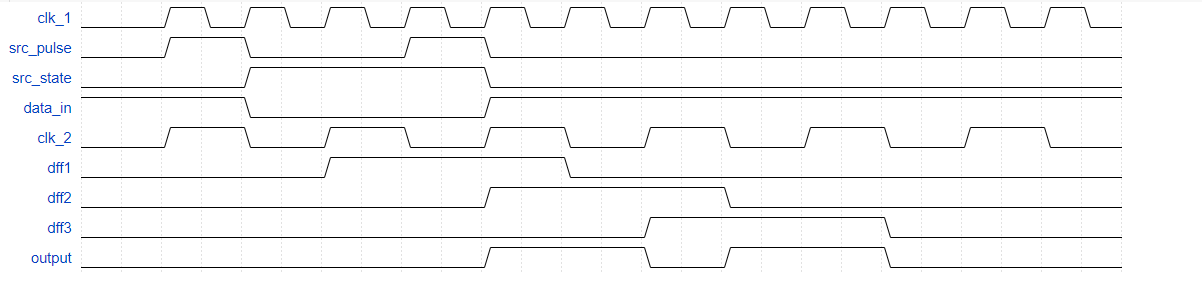

- 波形图如下所示。

- 首先将快时钟域的脉冲展宽为电平信号。

- 主要通过黄色框中的电路实现:src_pulse作为触发器的时钟使能信号,src_state拉了一个反馈路回到触发器的输入,可以在第二个脉冲到来将触发器的输出src_state拉低。

always@(posedge src_clk or negedge src_rst_n)begin if(src_rst_n==0) src_state <= 0; else if(src_pulse) src_state <= ~src_state; end - 将src_state的输出在慢时钟域打三拍分别得到dff1、dff2、dff3,并将dff2和dff3进行异或运算得到输出,完成将两个脉冲信号从快时钟域传到慢时钟域。

- 实现电路结构如下所示。

- 存在的问题

3. 握手机制

3.1 脉冲的握手同步

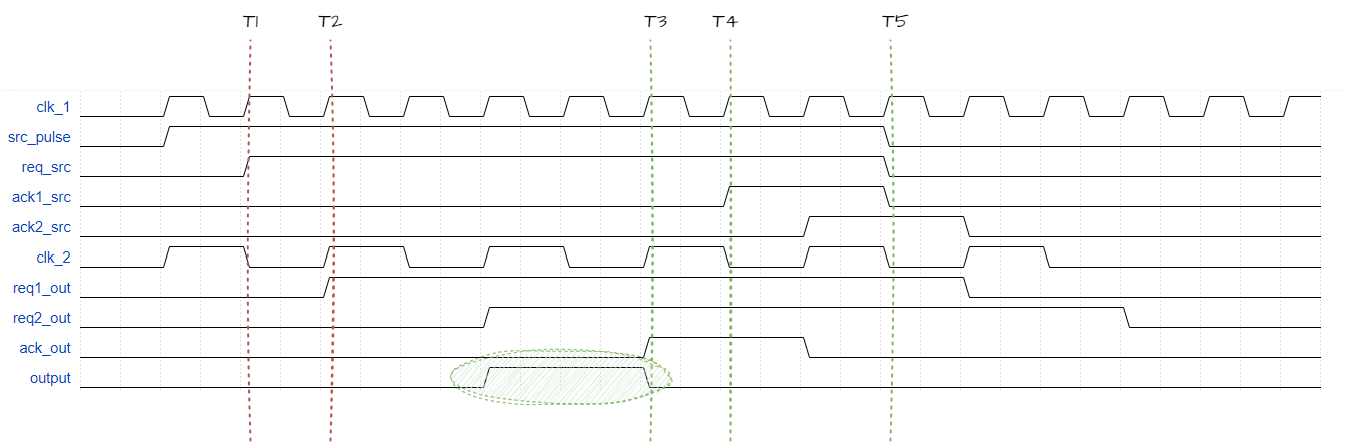

- 握手过程

- 在T1处,上升沿检测到src_pulse被拉高,那么将请求信号req_src也拉高。

- 在T2处,慢时钟域采样到快时钟域发送的req_src信号,并打一拍(跨时钟域打一拍稳定一下),先后获得req1_out和req2_out信号。

- 在T3处,慢时钟域采样到req2_out信号被拉高,返回快时钟域一个回复信号ack_out信号(我认为该信号只需要持续一个周期就可以)。

- 在T4处,快时钟域采样到慢时钟域发送的ack_out信号,并打一拍,先后获得ack1_src和ack2_src信号。

- 在T5处,快时钟域采样到ack2_src信号被拉高,说明当前快时钟域->慢时钟域的传输已经完成,可以将req信号和src_pulse信号拉低了。

- src_pulse在传输过程中一直拉高是为了保证在T1-T5期间没有别的脉冲信号传输,如果增加了其它处理来保证,src_pulse也可以只拉高一个周期。

- 绿色椭圆为同步过来的信号,对req2_out和ack_out信号做上升沿检测+异或可以把这段提取出来。

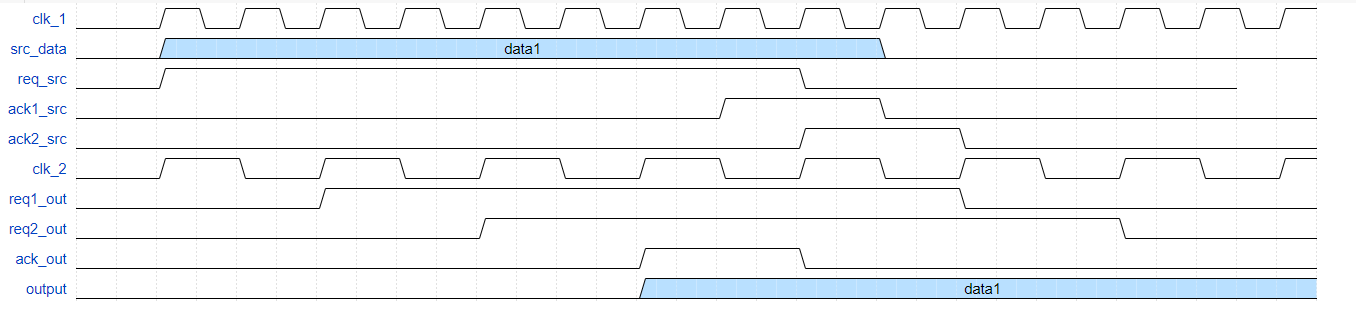

3.2 信号的握手同步

- 与脉冲的握手同步相类似,只是req信号和data信号是同时被送到总线上的。

4. 闭环结绳法

- 结绳+握手 详细讲解可以看这篇文章。

- 只适合少量慢速的数据传输。

5. 异步FIFO设计

- 异步FIFO的相关内容可以看这篇博客.

浙公网安备 33010602011771号

浙公网安备 33010602011771号