1. 用来作什么

- HLS(High Level Synthesis)

- Xilinx推出的可以直接使用C/C++/SystemC对Xilinx系列的FPGA进行编程,提高抽象等级,减少开发时间。

- 数字IC设计过程中不同的抽象等级:

- 这里引申一下行为级和RTL级的区别

- RTL级:寄存器传输级,使用寄存器这一级别的描述方式来描述,要求可综合,

- 行为级:通过行为语句描述电路要实现的功能,而不涉及具体结构,不考虑电路实现。

- HLS在系统级对电路算法进行描述,然后由Vivado HLS编译器将C代码综合成HDL描述,之后再进行逻辑综合,得到的网表可以直接映射到FPGA的器件上。

2. HLS 综合过程

- 分析,处理基于C的代码,加上用户所给出的指令和约束,来创建RTL描述,综合结束后得到Verilog/VHDL编写的RTL设计文档。

- 综合得到的RTL模型,可以放到HLS中进行C/RTL的协同仿真,Vivado HLS会自动产生一个测试集,进一步验证RTL设计的正确性。

3. 验证之后的打包

- 使用Vivado HLS的IP打包功能,那么HLS设计可以以IP核的形式被用到其它Xilinx工具中。

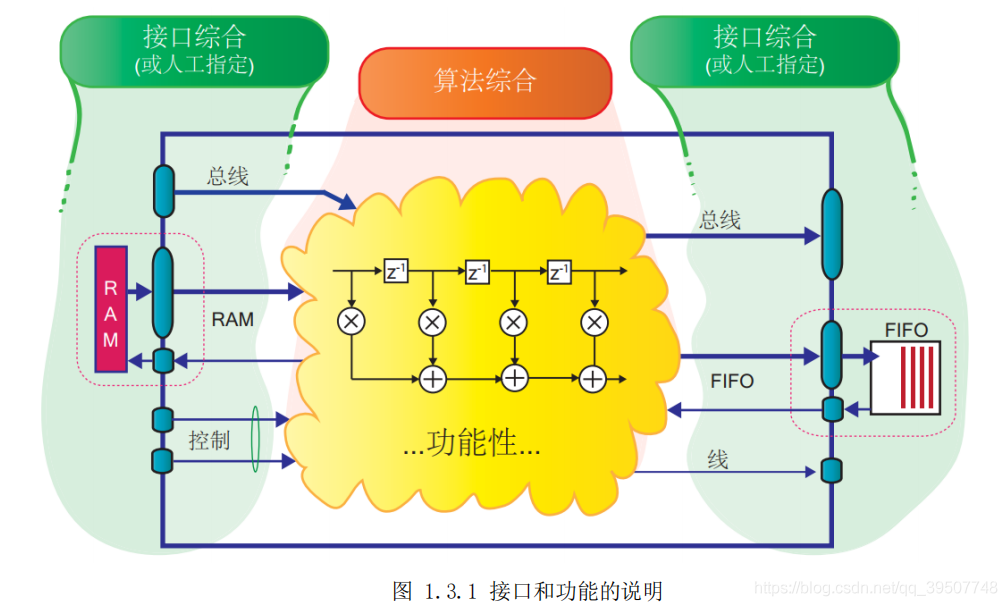

4. 接口综合 & 算法综合

- 做HLS时,设计者需要注意 接口综合以及算法综合。

- 接口综合

- 指接口类型及接口使用的协议,通过工具接口综合获取代码中参数、返回值(类型、位宽、方向)以及端口行为(协议)得到,也可以自己为接口选择协议。

- 算法综合

- 从代码中推断出各种运算操作,转换成RTL语句。主要包括以下三个阶段

- (1)解析出数据通路和控制元件

- (2)调度和绑定

- 调度是把由 C 代码解释得到的 RTL 语句翻译成一组运算。

- 绑定是调度好了的运算和目标芯片上的实际资源联系起来的过程。资源的功能和时序特性可能会影响调度,所以绑定得到的信息还会反馈给调度。

- (3)优化

- 设计者对设计的某些指标以及资源的利用情况加以限制(如时钟),对设计进行优化。

- 施加指令,映射到代码的某些特征上,比如可以指定HLS如何处理C识别出来的循环或数组。

5. HLS库

posted @

2023-06-14 15:22

可达达鸭

阅读(

440)

评论()

收藏

举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号