AMBA4 AXI 突发传输

1. AXI 中的突发传输

1.1 4KB 地址边界

- 单次突发传输的地址不能跨越 4KB 地址边界。

- 与AHB 中突发传输的 1KB 地址边界类似。

- page的地址空间单位为4KB对齐,为了防止一次burst传输访问了两个slave。

- 具体相关解释可以看另一篇博客,或是那篇博客参考的文章,文章讲的更详细一些。

- 一次突发传输不能在传输完成前提前终止,即使发生错误,也要完成全部传输。

1.2 突发传输相关信号

- 传输长度

- ARLEN/AWLEN:从0开始,实际长度值为AxLEN + 1.

- 传输宽度

- 每周期传输数据的字节数量,具体的传输宽度 = 2^AxSIZE.

- 传输类型

- FIXED

- 所有数据都使用起始地址,可用于对某个固定地址进行多次数据更新。例如:FIFO的读写

- INCR

- 初始地址进行递增,例如:RAM的读写

- WRAP

- 例如:Cache Line访问,用于存放循环使用的数据。

- FIXED

1.3 读写数据结构

- 窄位宽写数据传输(Narrow Transfer)

- 传输的数据位宽比通道的数据位宽小。

- 需要通过WSTRB[n]信号置高,设置WDATA从LSB到MSB方向,第n个字节有效。

- 对于读数据传输,从机没有STRB信号,只能主机计算有效数据的位置,进行读取。

- 非对齐传输(Unaligned Transfer)

- 对齐:设总线位宽为32bit,32bit/1byte = 4,所以地址能够被4整除,即对齐。

- AXI允许突发传输的起始地址不对齐。

- 对于非对齐的传输,主机会填充数据,将突发传输中的第一个数据对齐,并使用WSTRB信号置填充数据为无效。

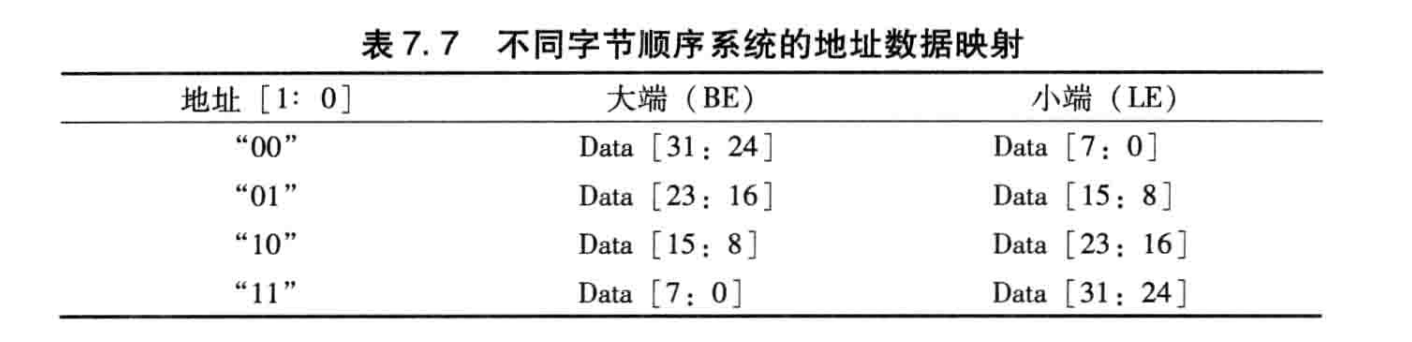

- 混合的大小端模式

- 大端:低地址写高位;小端:低地址写低位。

- 对于大端小端转换具体数据排列网上给出了很多答案,这里放出《硬件架构艺术》这本书中这部分的描述,以字节为单位摆放:

- 对于大端小端转换具体数据排列网上给出了很多答案,这里放出《硬件架构艺术》这本书中这部分的描述,以字节为单位摆放:

- AXI设定的要求是:

- 数据结构按照大小端模式决定字节的存储顺序。

- 传输时不考虑大小端。

- 网上有提到AXI的这种方案可以防止大小端共存产生数据覆盖,没有看懂是什么意思。

- 大端:低地址写高位;小端:低地址写低位。

1.4 读写回复结构

- RESP 信号

| Signal | Value | Description |

|---|---|---|

| OKAY | 00 | 常规访问成功 |

| EXOKAY | 01 | 独占访问成功 |

| SLVERR | 10 | 从机响应错误 |

| DECERR | 11 | 解码错误,一般由interconnect模块产生,主机给出的传输地址无效 |

如有问题,请指正

浙公网安备 33010602011771号

浙公网安备 33010602011771号