FPGA 入门 —— RAM(ip 核与原语的使用)

FPGA 入门 —— RAM(ip 核与原语的使用)

BRAM 简介

XILINX 系列的 FPGA ,如果想要做一个 RAM,有两种方式:

1、使用逻辑资源组成分布式 RAM,即 Distributed RAM

2、使用 XILINX 专用的 Block RAM,即 BRAM

前者是由 CLB 的 SLICEM 的 LUT 组合而成,构成 RAM 后,可能分布在不同的地方,具有一定的延迟;

后者是 Block RAM 是内嵌专用的 RAM,是 XILINX 做进 FPGA 内的专用资源,具有更好的时序性能;

这里我们以 ZYNQ-7000 为例:

可以看到红色方框中,标识出了此款 FPGA 的 BRAM 资源,我们也可以了解到,一个 BRAM 资源大小为 36Kbits(注意,这里是 bits),红色方框的这款含有 140 个这样的 BRAM,也就是一共含有 36Kbits * 140 = 4.9Mbits 大小的 BRAM 资源;

在 XILINX 的官方文档上,介绍这部分的文档是:

pg058-blk-mem-gen.pdf

有兴趣的可以下载来看下;

针对 BRAM 资源的接口形式,主要分为两种:

Native:本地 BRAM

AXI4:与 AXI4 总线互联的 BRAM

这里更多的来了解一下 Native 类型的 BRAM,等到要用到 BRAM 挂到 AXI 上的时候,再来仔细分析 AXI Interface 的 BRAM;

较为新的 XILINX 介绍这部分的内容叫 BMG(Block Memory Generator)

Block Memory Generator IP 核

分类

按照 BRAM 可以构成的器件类型来分,主要可以分为如下几种:

• Single-port RAM : 单口 RAM

• Simple Dual-port RAM:伪双口 RAM

• True Dual-port RAM:真双口 RAM

• Single-port ROM :单口 ROM

• Dual-port ROM:双口 ROM

信号描述

首先进行信号的描述,常用到信号含义如下表所示:

| Signal Name | Direction | Description |

|---|---|---|

| clka | Input | Port A 的同步时钟信号 |

| addra | Input | Port A 的地址信号 |

| dina | Input | Port A 写操作时候的输入数据信号 |

| douta | Output | Port A 读操作时候的输出数据信号 |

| ena | Input | Port A 的使能信号,在读,写,Rst 的时候需要此信号 |

| wea | Input | Port A 的写使能信号 |

| rsta | Input | Port A 的复位信号 |

| regcea | Input | Port A 的可选后级输出寄存器信号 |

| clkb | Input | Port B 的同步时钟信号 |

| addrb | Input | Port B 的地址信号 |

| dinb | Input | Port B 写操作时候的输入数据信号 |

| doutb | Output | Port B 读操作时候的输出数据信号 |

| enb | Input | Port B 的使能信号,在读,写,Rst 的时候需要此信号 |

| web | Input | Port B 的写使能信号 |

| rstb | Input | Port B 的复位信号 |

| regceb | Input | Port B 的可选后级输出寄存器信号 |

| sbiterr | Output | Single-Bit Error 信号 |

| dbiterr | Output | Double-Bit Error 信号 |

| injectsbiterr | Input | Inject Single-Bit Error: Available only for Zynq-7000 and 7 series ECC configurations. |

| rdaddrecc | Output | Read Address for ECC Error output: Available only for Zynq-7000 and 7 series ECC configurations |

| eccpipece | Input | ECC Pipe Line Register Clock Enable: Available only for UltraScale architecture-based devices. |

| sleep | Input | 动态功耗调整: If sleep pin is High , the Block Memory Generator core is in power saving mode. Available only for UltraScale architecture-based devices |

Single-port RAM

XILINX 官方的 pg058 部分描述了 Single-port RAM 的典型应用,可用于处理器暂存数据的 RAM,或者作为查找表等;它的图解如下所示,斜杠的信号为可选信号,其余的是必选信号;

CLKA 为输入的时钟信号,时钟上升沿对数据进行写入/读出

DINA 为写入的数据总线

DOUTA 为读出的数据总线

ADDRA 为地址总线

ENA 为使能端,当 ENA 为 1 的时候,可进行读写操作,ENA 为 0 的时候,无法进行读写

WEA 为写使能,当 ENA 为 1 同时 WEA 为 0 的时候,为读操作;当 ENA 和 WEA 同时为 1 的时候,为写操作;

由于只有一组地址总线,故,单口的 RAM 是无法同时进行读写操作的,只能读、写分开进行;

Simple Dual-port RAM

XILINX 官方的 pg058 部分描述了 Simple Dual-port RAM 的典型应用:Content addressable memories, FIFOs

它的图解如下所示:

与单口 RAM 不同的是,伪双口 RAM 输入有两路时钟 : CLKA/CLKB ,独立的两组地址信号 ADDRA/ADDRB,Port A 提供 DINA 写数据总线,作为数据写入的入口;Port B 仅仅提供数据读的功能,读出的数据为 DOUTB;

所以伪双口 RAM 能够提供同时读写 RAM 的功能

True Dual-port RAM

XILINX 官方的 pg058 部分描述了 True Dual-port RAM 的典型应用:多处理器存储方案,Multi-processor storage

它的图解如下所示:

真双口 RAM 提供了独立的 Port A 和 Port B 的读写功能,既可以同时处在读,也可以同时写,也可以一个读一个写;

Single-port ROM

BRAM 也可以做成 ROM,典型应用是:Program code storage, initialization ROM,如下图所示

与 Single-port RAM 几乎相同,唯一不同的是,没有 DINA 信号,因为是 ROM,所有不提供写入;

Dual-port ROM

BRAM 也可以做成 ROM,典型应用是:Single ROM shared between two processors/systems

双口的 ROM,提供 Port A 和 Port B 两路读;

选项说明

Selectable Memory Algorithm

使用 XILINX 的 BMG 生成上述类型的 RAM/ROM 的时候,有一个可选项叫做生成的算法,这里有三种可选的算法:

Minimum Area Algorithm : 面积最优

Low Power Algorithm:功耗最低

Fixed Primitive Algorithm:固定原语

Configurable Width and Depth

在使用 BMG 生成 RAM 的时候,位宽支持配置从 1 bits ~ 4608 bits,深度支持大于等于 2,具体最大能够配置出多少 RAM,需要查看当前的器件手册中包含的 BRAM 的个数;

Selectable Operating Mode per Port

BRAM 组成 RAM 后的读写模式可以分为三种,并且 Port A 和 Port B 可以独立配置:

1. Write First Mode

2. Read First Mode

3. No Change Mode

这些 mode 是针对一个 Port 来说的;

Write First Mode

这种模式下,写操作的优先级高于读操作,它的时序如下所示:

这个时序很生动的描述了这种 mode :

1、刚刚开始,ENA 信号一直为 0,即,没有使能;

2、第一个虚线,也就是 CLKA 的上升沿位置,采到 ENA 为 1,同时 WEA 为 0,则代表为 READ 时序,同时,在这个上升沿,采集到 ADDRA 上为 aa(ADDRA 为并行地址总线),那么就会在获取到 aa 这个地址中的值后(经过了一点延时),将数据打到 DOUTA[15:0] 上,所以这里可以看到 DOUTA 上是 MEM(aa),也就是 aa 这个 RAM 地址中存储的数据;

3、第二个虚线,CLKA 上升沿的时候,同样会检测 ENA 和 WEA,此刻,它们都为 1,则代表 WRITE 时序来了,此刻采集到写入数据总线 DINA 上的数据为 1111,地址总线上是 bb,那么此刻是将地址 bb 的值放到 DOUTA 上呢,还是直接将 DINA 的值放到 DOUTA 上呢,这个 Operating Mode 就是解决这个问题的,在 Write First Mode 的情况下,DINA 的 1111 数据直接被送到了 DOUTA 总线上,同时,MEM(bb) 的内容被写入 1111,;

4、第三个虚线,CLKA 上升沿的时候,同理,2222 数据被直接写到 MEM(cc),同时被输出到 DOUTA 上

5、第四个虚线,CLKA 上升沿的时候,WEA 信号被拉到 0,但是 ENA 信号还是 1,说明当前不存在 WRITE了,只有 READ 时序,那么会将 ADDRA 上采集到的 dd 地址的数据读出到 DOUTA 上;

Read First Mode

这种模式下,读操作的优先级高于写操作,它的时序如下所示:

有了 Write First Mode 的分析过程,分析这个也不算困难:

1、刚刚开始,ENA 信号一直为 0,即,没有使能;

2、第一个虚线,也就是 CLKA 的上升沿位置,采到 ENA 为 1,同时 WEA 为 0,则代表为 READ 时序,同时,在这个上升沿,采集到 ADDRA 上为 aa(ADDRA 为并行地址总线),那么就会在获取到 aa 这个地址中的值后(经过了一点延时),将数据打到 DOUTA[15:0] 上,所以这里可以看到 DOUTA 上是 MEM(aa),也就是 aa 这个 RAM 地址中存储的数据;

3、第二个虚线,CLKA 上升沿的时候,同样会检测 ENA 和 WEA,此刻,它们都为 1,则代表 WRITE 时序来了,此刻采集到写入数据总线 DINA 上的数据为 1111,地址总线上是 bb,由于是在 Read First Mode 的情况下,DOUTA 读出的数据是 bb 地址的数据,读操作完成后同时,MEM(bb) 的内容更新为 1111,;

4、第三个虚线,CLKA 上升沿的时候,DOUTA 读出的数据是 cc 地址的数据,读操作完成后同时,MEM(cc) 的内容更新为 2222;

5、第四个虚线,CLKA 上升沿的时候,WEA 信号被拉到 0,但是 ENA 信号还是 1,说明当前不存在 WRITE了,只有 READ 时序,那么会将 ADDRA 上采集到的 dd 地址的数据读出到 DOUTA 上;

No Change Mode

还有一个 No Change Mode,这个 No Change 指的是当在写的时候, DOUTA 读的数据总线数据保持不变,也就是 No Change;

可以看到,当在往 RAM 里面写的时候,DOUTA 读出的数据保持了不变,即,一直为 aa 的内容,直到 WEA 被拉低,重新进入 READ 模式;

综上所述,这几种模式,主要都是针对的是读数据总线的行为,是直接读出 DINA 呢?还是读出旧的内存地址的数据呢?还是在写的时候被拉住;

Selectable Port Aspect Ratios

支持 Port A 和 Port B 配置不同的位宽,甚至同一个 Port 配置 Read 和 Write 的位宽不同;

Optional Byte-Write Enable

BMG 支持可选的一个叫做 Byte-Write 模式,这是一个针对 Write 的模式,在这个模式下,WEA 信号由之前的 1 bit 扩展为了 N 个 bit,在这 N 个 bit 中,1 代表对应的 DINA 中对应 Bytes 会被更新到 ADDRA 对应的地址上去,如果 N bit 中,0 代表对应的 DINA 对应的 Byte 不会被更新到 ADDRA 对应的地址上去,有点拗口,下面是一个基于 Singal-port RAM,输入数据总线 DINA 为 24 bits 宽度,也就是 3 个 Bytes,WEA 为 3 个 bit 宽度,直接看 Timing

DINA 的每个 Byte,对应到 WEA 的每一个 bit,可以看到:

1、第一个虚线 CLKA 上升沿,WEA[2:0] 是 3b'011,ADDRA 是 0x0000 地址,DINA[23:0] 是 FF EE DD,那么他的行为是,由于 WEA=011,代表控制器会去将 DINA 的 后面两个 Bytes 更新到 RAM ADDRA 对应的地址上去,也就是 EE DD 被更新到 0000 的对应位置;

2、第二个虚线 CLKA 上升沿,WEA[2:0] 是 3b'010,ADDRA 还是 0x0000 地址,DINA[23:0] 是 CC BB AA,那么它的含义是,将 BB 更新进去,也就是看到 RAM Contents 内容为 00 BB DD

3、第三个虚线 CLKA 上升沿,WEA[2:0] 是 3b'101,ADDRA 还是 0x0000 地址,DINA[23:0] 是 99 88 77,那么它的含义是,将 99 和 77 按照位置定义关系更新进去,也就是看到 RAM Contents 内容为 99 BB 77

4、第四个虚线 CLKA 上升沿,WEA[2:0] 是 3b'000,所以即便是 DINA 有数据,那么 RAM 内容也不会被更新进去;

5、第五个虚线 CLKA 上升沿,WEA[2:0] 是 3b'110,ADDRA 还是 0x0000 地址,DINA[23:0] 是 33 22 11,那么它的含义是,将 33 和 22 按照位置定义关系更新进去,也就是看到 RAM Contents 内容为 33 22 77

6、第六个虚线 CLKA 上升沿,WEA[2:0] 是 3b'010,ADDRA 还是 0x0000 地址,DINA[23:0] 是 00 FF 00,那么它的含义是,将 FF 按照位置定义关系更新进去,也就是看到 RAM Contents 内容为 33 FF 77

Collisions

既然是支持多 Port 同时写入,那么就会存在这个冲突的问题,在冲突发生的时候,存储内容不可预知;

冲突主要出现在一下场景:

- 两个 Port 的异步时钟,一个 port 正在往一个地址写数据,另一个 port 在指定时间内,必须不能够去读写这个地方;

- 两个 Port 同步时钟的情况下,两个 Port 同时企图写同一个 memory 的情况下;

- 使用 Byte-Writes 的时候,正好同时写到了同一个地方的情况下;

Write-Write Collision

以 Byte-Writes 为例,假设 Port A 和 Port B 的 ADDR 都是 0x0000;

如上图所示:

1、第一个虚线时钟上升沿,WEA 是 1100,WEB 是 0011,所以写入的内容正好错开,并不冲突

2、第二个虚线时钟上升沿,WEA 是 0101,WEB 是 1010,所以写入的内容正好错开,也不冲突

2、第三个虚线时钟上升沿,WEA 是 1110,WEB 是 0011,第三个 bit 冲突,往同一个地址写内容,所以看到的是 7777 XX00,其中的 XX 是不可预知的内容;

后面的分析类似,不在赘述;

Optional Output Registers

BMG 允许可选的在输出级增加一级寄存器,来改善输出性能;

可以选择在两个输出的地方增加寄存器:

1、在每个 Block RAM 输出的地方增加寄存器;

2、在整个 BMG Core 输出的地方增加寄存器;

这两个配置都可以针对 Port A 和 Port B 进行单独的配置;

Notes:增加一级输出寄存器,会增加一个 Clock Cycle 的延时;

如果是使用每个 Block RAM 输出端增加 Register,这个触发器是属于 BRAM 的内部资源,不会占用其他的 FPGA 资源;如下图所示:

Block RAM 中的那个寄存器就是指的第一种在输出端增加寄存器;

Core Output Register 那个寄存器,就是第二种,在整个 BMG 输出端增加 Register 的方式;

界面说明

Basic 界面

说明:

1、Interface Type:接口类型,可选择的有

Native:可以与旧版本的块内存生成器(Block Memory Generator)相兼容。没有AXI4的高速接口一般选择此项即可。

AXI4:接口直接与AXI4高速串行接口进行通信时可以选择此项。

2、Memory Type:IP 核的功能选择,可供选择的包括:

° Single Port RAM :单口RAM,IP 核包括 地址端口、时钟端口、输入数据端口、输出数据端口、时钟使能、写使能。

° Simple Dual Port RAM :简单双口RAM,IP 核包括 两个彼此独立的端口,其中一个端口负责写入数据,另一个负责读出数据。

° True Dual Port RAM :真正双口RAM,IP 核包括两个独立的端口,并且每个端口都可读可写。

° Single Port ROM :单口ROM,IP 核包括 地址端口、时钟端口、时钟使能、输出数据端口。

° Dual Port ROM :双口ROM,IP 核有两个彼此独立的端口。3、Generate address interface with 32 bits:勾选此项后,接口地址线变为32位,一般来说,没有那么大的内存需求,不做勾选。

4、Common Clock:当 IP 核的输入端为双端口时,此项可选,勾选后表示 端口 A、B 的时钟由同一时钟驱动,即读写时钟同步。勾选与否视实际应用情况而定。

5、Byte Write Enable:字节写使能,一般不做选择,默认字节为8位。

6、Algorithm Options:内存实现的算法选择

Algorithm:可供选择的有:

Minimum Area:最小面积,将用最少数量的原语来实现 IP 核;(没特殊要求,一般来说,就保持此默认选项)

Low Power:低功耗,在读操作或写操作时,使能最少数量的块RAM原语。

Fixed Primitives:固定原语,用所选择的原语类型来实现 IP 核。

Primitive:原语选择,仅当 Algorithm 中选择 Fixed Primitives 时,此项才可选。

Port A Options 界面

说明:

1、Operating Mode:操作模式,每一个端口都可以选择相应的操作模式,供选择的模式有三种:

Write First:此模式下,输入的数据同时被送到内存和输出端口。

Read First:此模式下,当前输入的数据送到内存中存储,前一个数据被送到输出端口。

No Change:此模式下,在写操作进行时,读数据端口已经读到的数据在此期间保持不变。

(关于三种模式具体的时序图,可以查看文末的 参考说明[1])

关于模式配置,为了避免数据冲突,保证设计的安全性,XILINX在官方文档中给出如下建议:

- 对于简单双口 RAM (Simple Dual Port RAM),如果读写时钟同步,端口A 的写模式 建议配置为Read First;如果读写时钟异步,那么端口A 的写模式建议配置为 Write First;

Port B Options 界面

说明:

1、Optional Output Register:输出寄存选项,包括:

Primitives Output Registers:原语输出寄存,勾选此项,在内存原语之后将插入输出寄存器。选择后可以提高 IP 核的运行性能。

Core Output Registers:IP 核输出寄存,勾选此项,在IP 核的输出端将插入输出寄存器。选择后可以提高 IP 核的运行性能。但是会增加读数据的shi'zhong'yan'chi

REGCE[A|B] Pin:勾选此项,IP 核将用独立的输入管脚 REGCEA 或 REGCEB 去控制内存最后一级输出寄存器的使能端。否则,所有的寄存器都由 ENA或者ENB 去控制。

2、Output Reset Options:输出复位选项,主要包括:

RST[A|B] Pin (Set/Reset Pin):勾选此项表示,选择复位/置位引脚。

Other Options 界面

说明:

1、Memory Initialization:内存初始化,一般在配置为ROM 使用COE文件来初始化。

Fill Remaining Memory Locations:剩余内存空间的初始化,意思就是说,当内存空间数量大于COE文件内数据数量时,那么剩下未被初始化的内存将用设定的置进行初始化。

Summary 界面

使用 IP

在雷达信号处理中,对于多周期的回波信号进行MTD多普勒滤波时,难免要进行数据重排。原来的回波按周期进入处理单元,数据读出时需要按照距离门单元读出。此处以 8 周期的回波数据点(每个周期 256 点数据)为例,利用刚才配置的 RAM 进行数据重拍。

说明:距离重拍的方式方法不唯一,不必拘泥于此,仅提供思路之一。

具体程序:

module DATA_REARRANGEMENT_RAM_CONFG (

//--------------------输入端口列表-----------------------//

// Port A

input I_CLKA, //

input I_WEA,

input [7:0] I_DATA,

// Port B

input I_CLKB, //

//--------------------输出端口列表-----------------------//

output [7:0] O_DATA,

output O_Rsta_busy

);

//------------------内部参数、变量定义-------------------//

// IP 核的输入

wire ena;

reg [10:0] addra;

reg [10:0] R_ADDRA;

reg [7:0] dina;

wire enb;

wire rstb;

wire [10:0] addrb;

reg [7:0] R_256_COUNTER;

reg [2:0] R_8_COUNTER;

// 不用作输出的信号

wire rsta_busy;

wire rstb_busy;

//--------------------模块的程序设计---------------------//

// 端口A输入配置

assign ena = 1'b1; // 让端口 A 一直处于使能状态

always @ (posedge I_CLKA)

begin

if(!I_WEA ||(rsta_busy))

begin

R_ADDRA <= 0;

end

else

begin

R_ADDRA <= R_ADDRA + 1;

end

end

always @ (posedge I_CLKA)

begin

addra <= R_ADDRA;

end

always @ (posedge I_CLKA)

begin

if(!I_WEA ||(rsta_busy))

begin

dina <= 8'b0000_0001;

end

else

begin

dina <= I_DATA;

end

end

// 端口B输入配置

assign enb = 1'b1; // 让端口 B 一直处于使能状态

assign rstb = I_WEA; //端口 A 写入完成后 端口 B 便开始工作 结束复位

// 模8的计数器

always @ (posedge I_CLKB)

begin

if(rstb||(rstb_busy))

begin

R_8_COUNTER <= 0;

end

else

begin

R_8_COUNTER <= R_8_COUNTER + 1;

end

end

// 模256的计数器

always @ (posedge I_CLKB)

begin

if(rstb ||(rstb_busy))

begin

R_256_COUNTER <= 0;

end

else

begin

if (R_8_COUNTER == 3'b111)

begin

R_256_COUNTER <= R_256_COUNTER + 1;

end

else

begin

R_256_COUNTER <= R_256_COUNTER;

end

end

end

assign addrb = R_256_COUNTER + R_8_COUNTER * 256;

// 输出

assign O_Rsta_busy = rsta_busy;

// RAM IP 例化

DATA_REARRANGE_RAM your_instance_name (

// Port A input

.clka(I_CLKA), // input wire clka // Port A 的操作时钟(同步)

.ena(ena), // input wire ena // Port A 的时钟使能

.wea(I_WEA), // input wire [0 : 0] wea // Port A 的写使能

.addra(addra), // input wire [10 : 0] addra // Port A 的地址线

.dina(dina), // input wire [7 : 0] dina // Port A 的数据线

// Port B input

.clkb(I_CLKB), // input wire clkb // Port B 的操作时钟(同步) 同步RAM的话 二者的时钟必须是 同一个外部时钟驱动

.rstb(rstb), // input wire rstb // 复位内存锁存器和输出寄存器 高电平复位有效

.enb(enb), // input wire enb // Port B 的时钟使能

.addrb(addrb), // input wire [10 : 0] addrb // Port B 的地址线

// Output

.doutb(O_DATA), // output wire [7 : 0] doutb // Port B 的数据线 RAM输出

.rsta_busy(rsta_busy), // output wire rsta_busy // Port A 正处在复位状态

.rstb_busy(rstb_busy) // output wire rstb_busy // Port B 正处在复位状态

);

endmodule

程序说明:尽管配置时,用的异步RAM 但是 使用时还是用的同步时钟共同驱动。

验证 IP 设计

TestBench 如下:

`timescale 1ns/1ps

module TB_DATA_REARRANGEMENT ();

//-----------------被测试模块输入接口声明--------------------//

reg I_CLK ;// 公共时钟 100 MHz

reg I_WEA ;// 写使能

reg [7:0] I_DATA;

//----------------被测试模块的输出接口声明-------------------//

wire [7:0] O_DATA ;

wire O_Rsta_busy;

//-----------------------内部变量声明-----------------------//

reg [7:0] R_DATA [1:3000];

//-----------------------测试程序---------------------------//

//产生激励时钟

`define CLK_PERIOD 10

initial I_CLK = 0 ;

always #(`CLK_PERIOD/2) I_CLK = ~I_CLK ;

//初始化控制信号

initial

begin

I_WEA = 0;

#(`CLK_PERIOD * 10);

// I_WEA = 1;

#(`CLK_PERIOD * 5000);

$stop;

end

//数据输入

integer K = -1;//读取数据计数变量

initial $readmemb("D:/Vivado_WorkSpace/CSDN_BLOG_EXAMPLE/TEST_FILES/RAM_2048.txt",R_DATA);

always @ (posedge I_CLK)

if (O_Rsta_busy)

begin

I_WEA = 0;

K = -1;

end

else

begin

if(K <= 2047)

begin

I_WEA = 1;

K=K+1;

I_DATA=R_DATA[K+1];

end

else

begin

I_WEA = 0;

K=K+1;

end

end

//被测试模块例化

DATA_REARRANGEMENT_RAM_CONFG inst_DATA_REARRANGEMENT_RAM_CONFG

(

.I_CLKA (I_CLK),

.I_WEA (I_WEA),

.I_DATA (I_DATA),

.I_CLKB (I_CLK),

.O_DATA (O_DATA),

.O_Rsta_busy (O_Rsta_busy)

);

endmodule

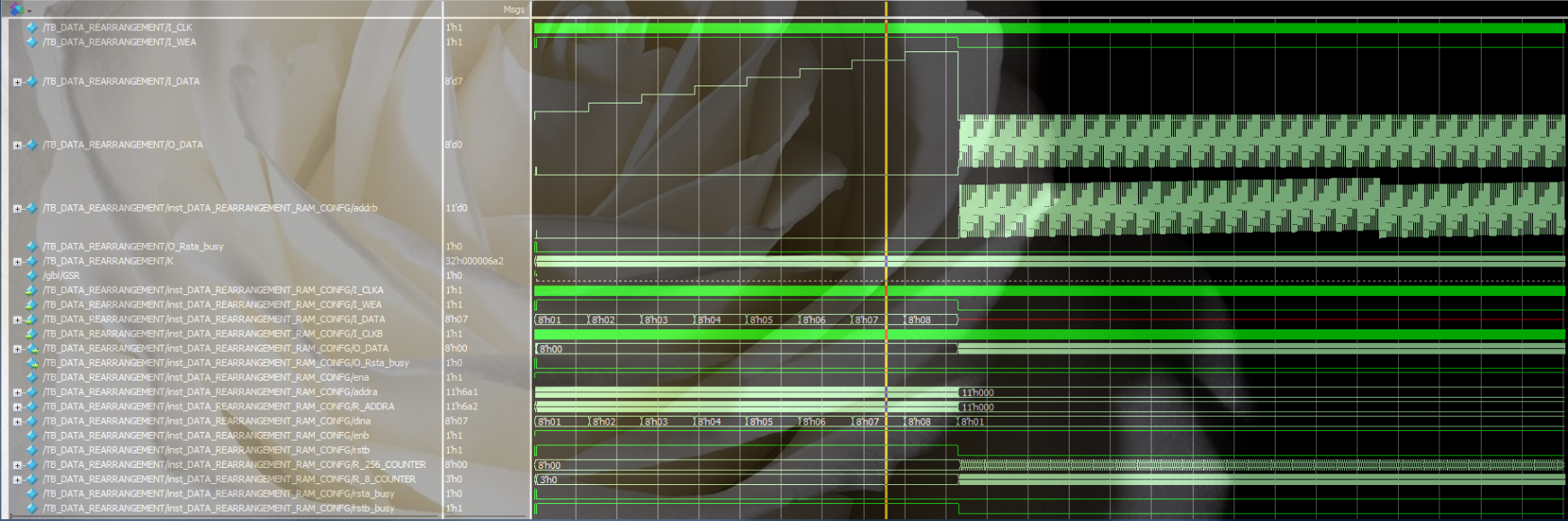

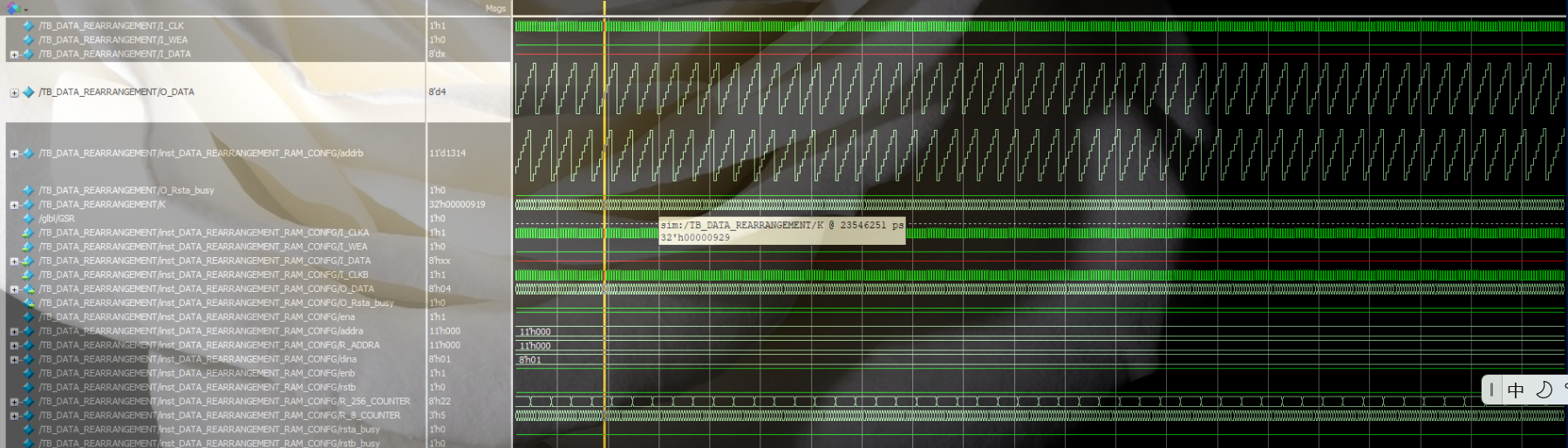

波形如下:

参考说明

[1] PG058. Xillinx Inc.

链接:pg058

浙公网安备 33010602011771号

浙公网安备 33010602011771号