Quartus 入门 —— 加法器

Quartus 入门 —— 加法器

设备与软件版本

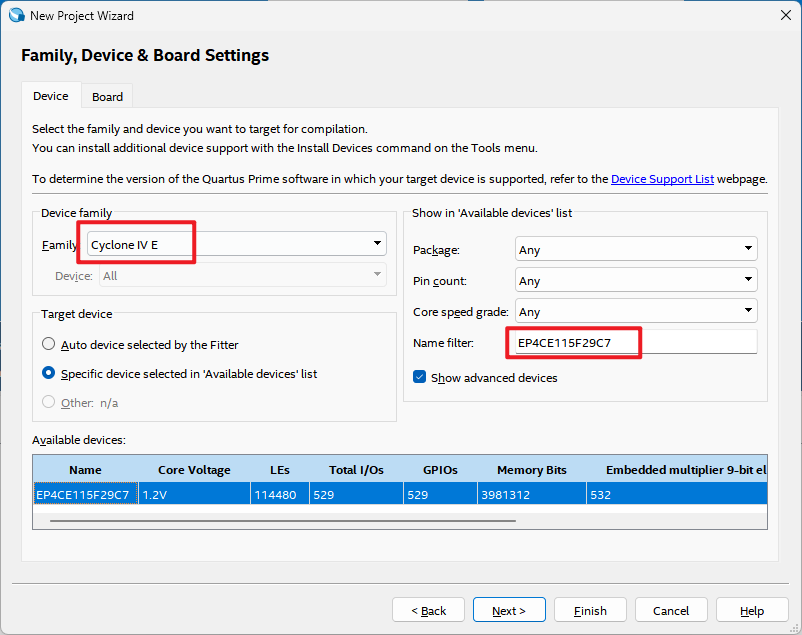

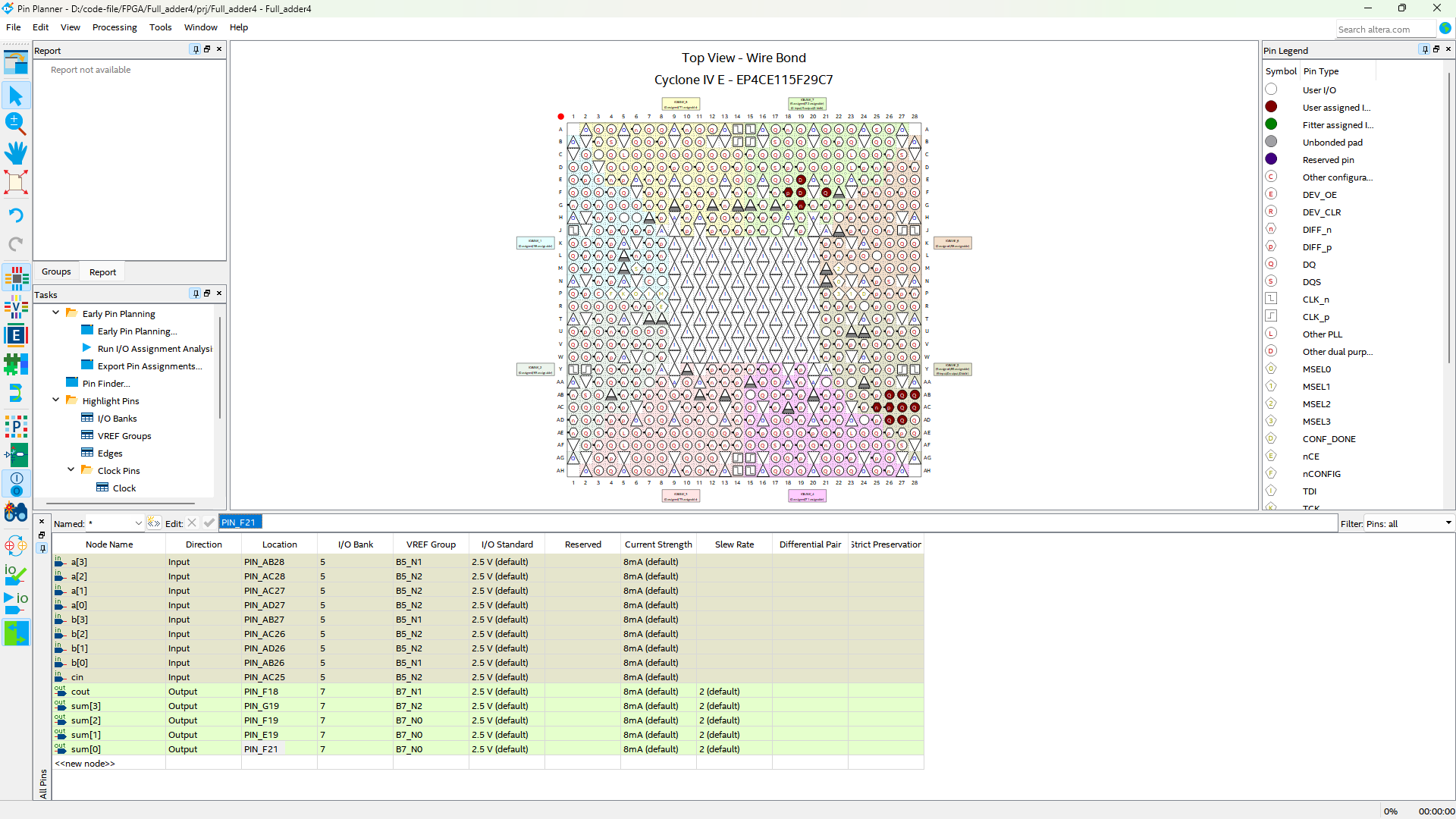

这里使用的 intel 的 芯片为 EP4CE115F29C7 的开发板,软件使用的是 Quartus(Quartus Prime 18.1) 的版本

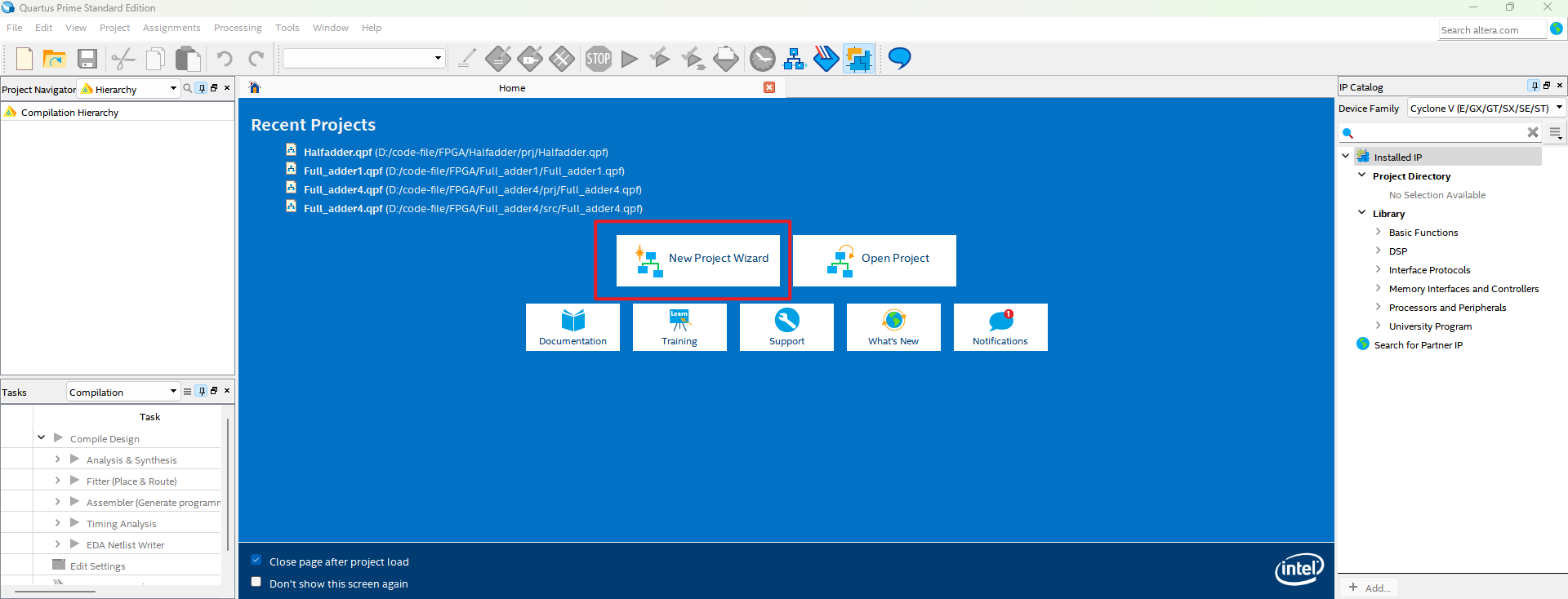

创建项目

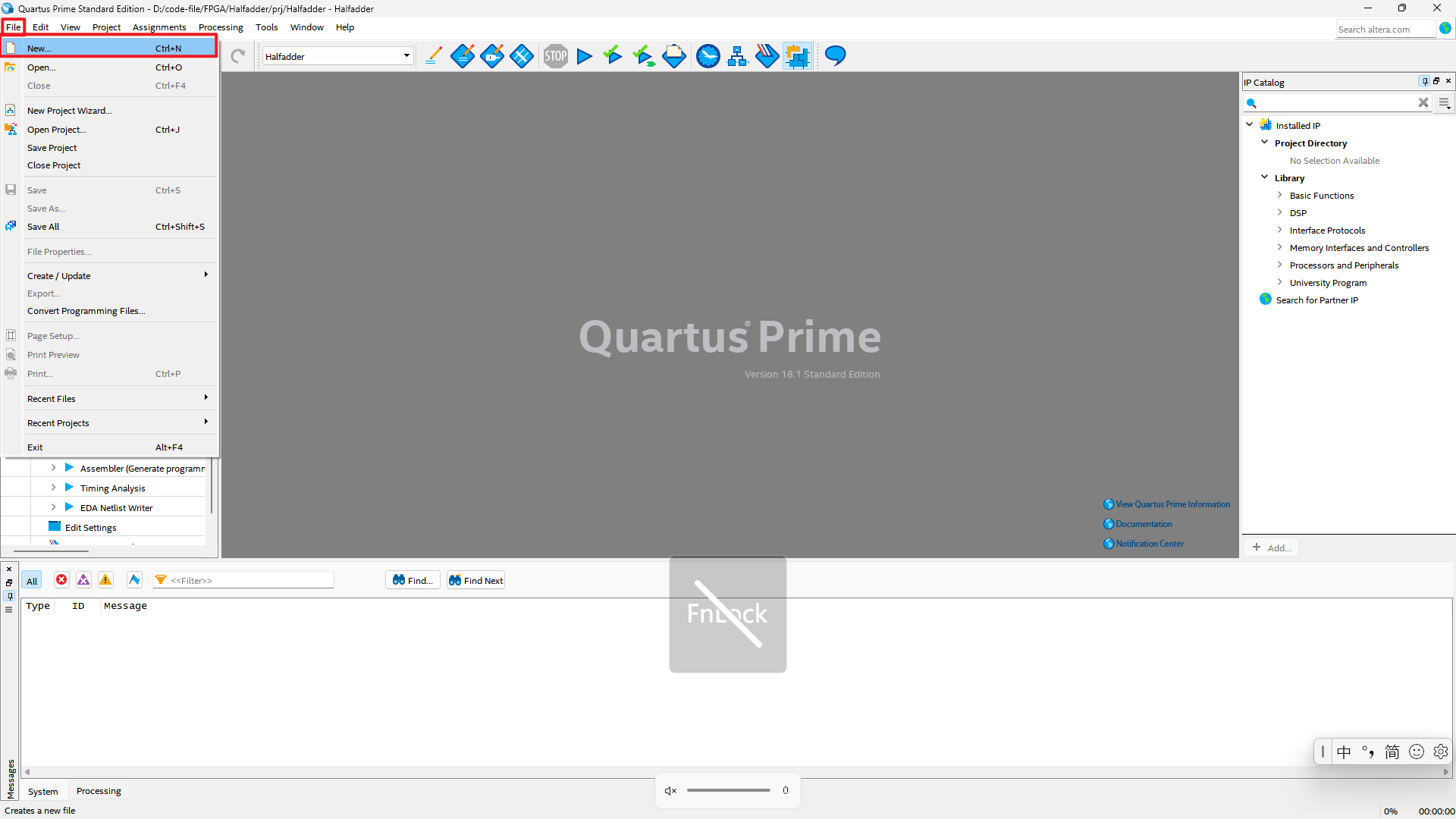

首先点击新建项目:

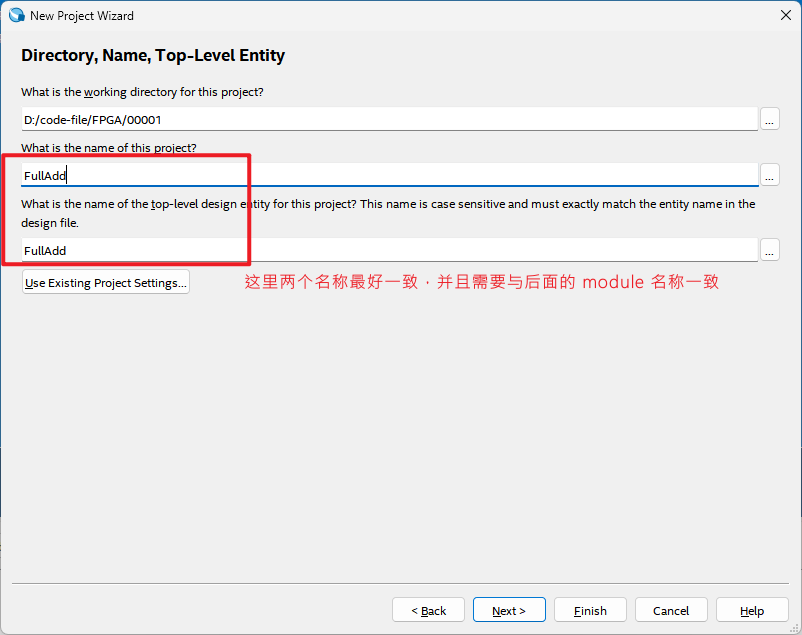

下面我们就直接点击下一步到芯片选择部分:

这里我们需要选择 Cyclone IV E 的 EP4CE115F29C7 芯片

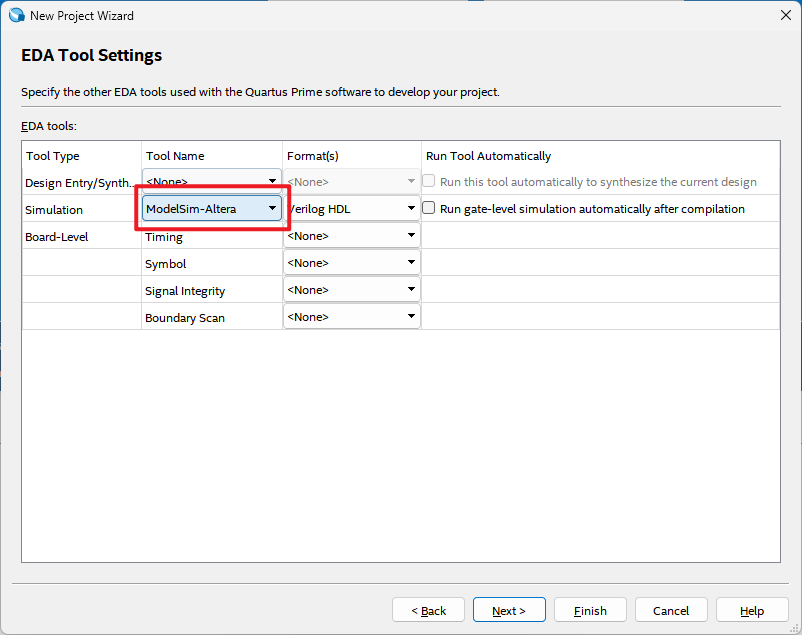

然后这里我们选择使用 ModelSim-Altera 进行仿真,然后我们直接点击下一步直接到结束即可

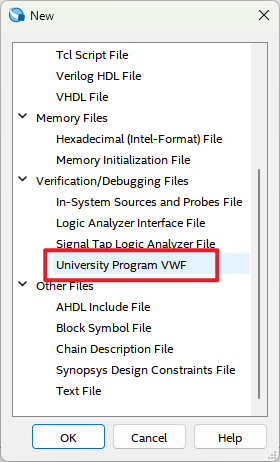

然后我们开始创建文件,这里我们可以创建多种类型的文件:

这里我们是主要使用图中圈出的这两种文件类型:

-

Block Diagram/Schematic File :这种文件类型就是我们平时绘制原理图需要使用的文件,后缀是 .bdf 和 .bsf

-

Verilog HDL File : 这种文件类型就是我们需要写 verilog 代码的文件类型,后缀是 .v

原理图设计

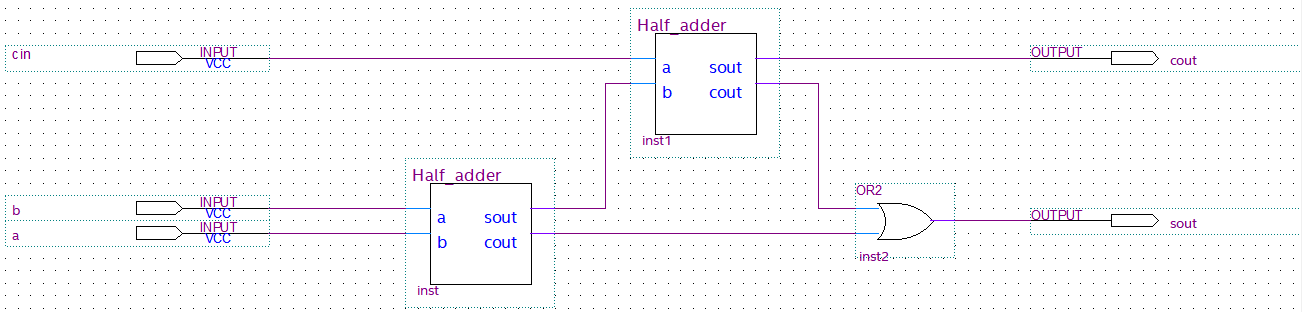

首先我们新建一个项目,我们这里将名称全部设置为 Full_adder1,首先我们需要新建一个原理图文件,由于我们的全加器是由两个半加器和一个二位或门组成的电路,所以这里我们先绘制一个半加器原理图

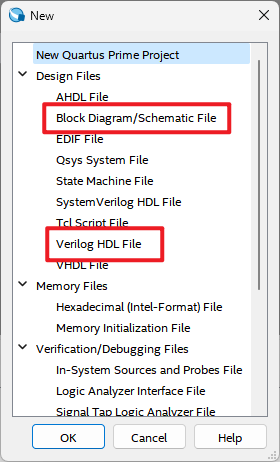

首先我们介绍一下如何进行原理图绘制即工具如何使用:

这里再软件中种提供了很多种不同元器件,我们也可以去安装一些其他的元器件包:

这里我们不尽可以使用软件自带的原件,我们也可以选择使用自己封装的元器件

我们将文件名设置为 Half_adder ,原理图如下:

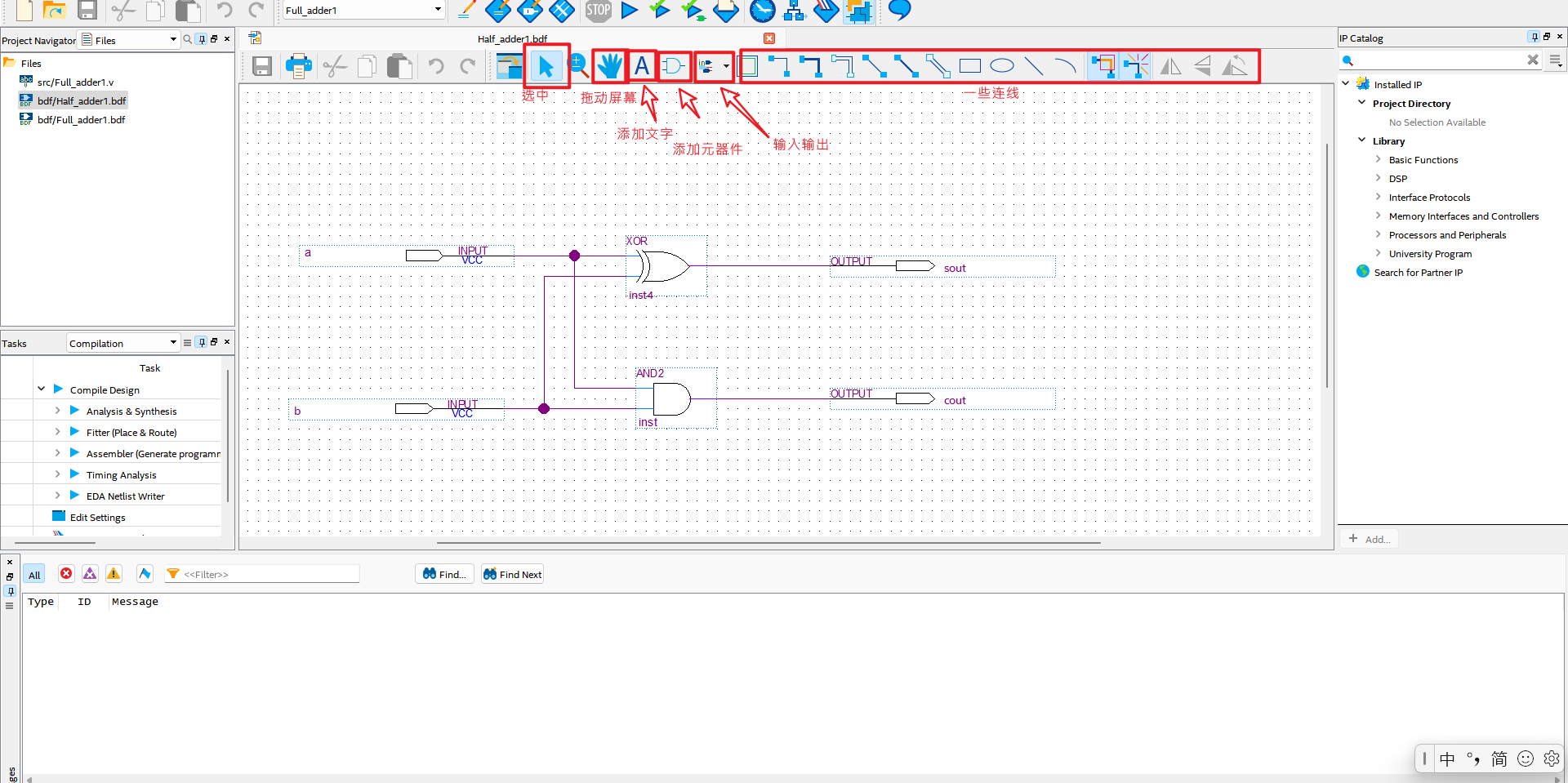

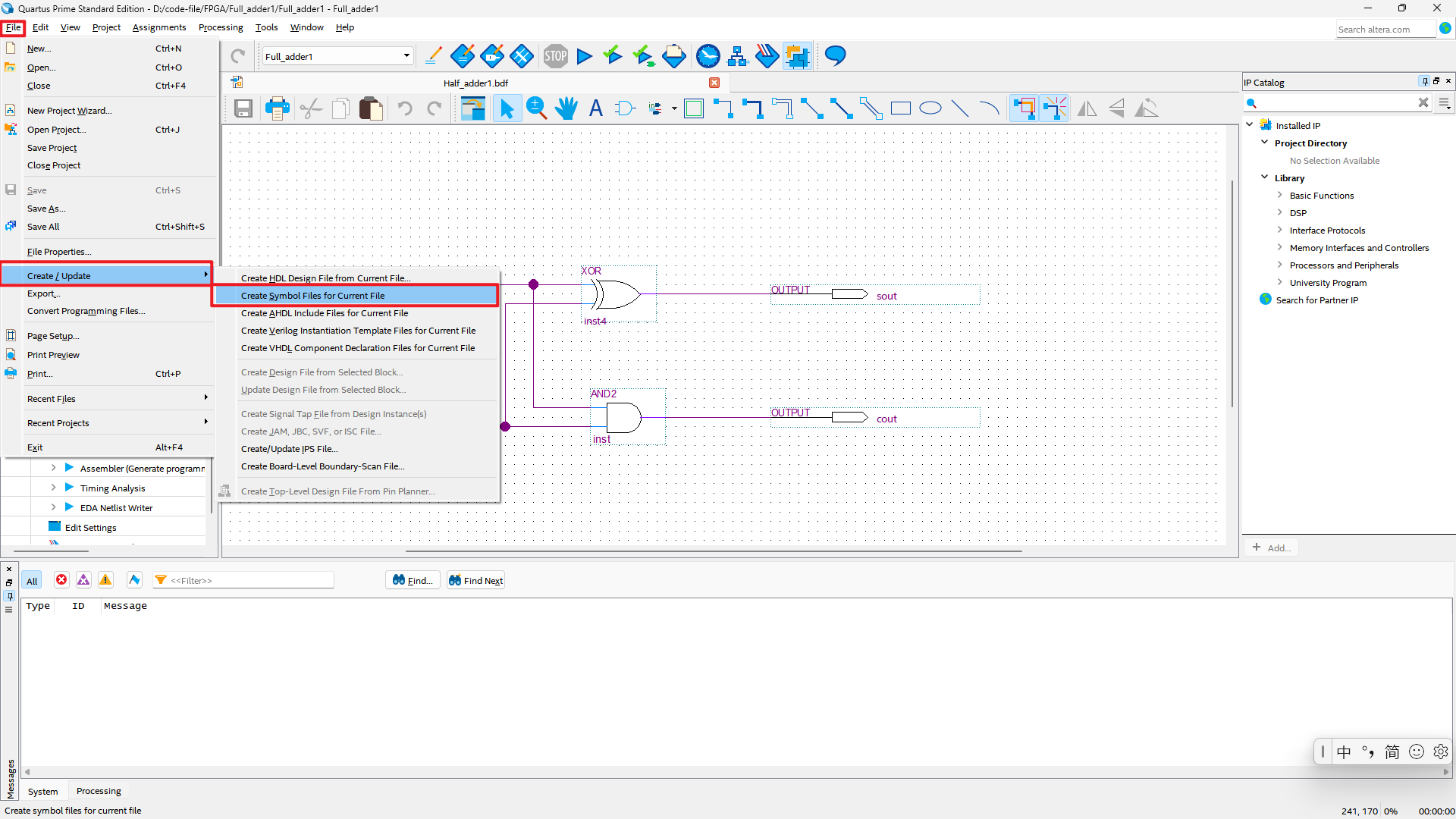

然后我们将半加器封装为可以调用的元器件:

这里我们所绘制的原理图存储文件的类型是 .bdf ,我们封装好的元器件的文件格式为 .bsf

最后我们进行绘制一位全加器,这里我们就需要调用我们前面封装好的半加器的元器件,过程不进行演示,这里直接给出原理图:

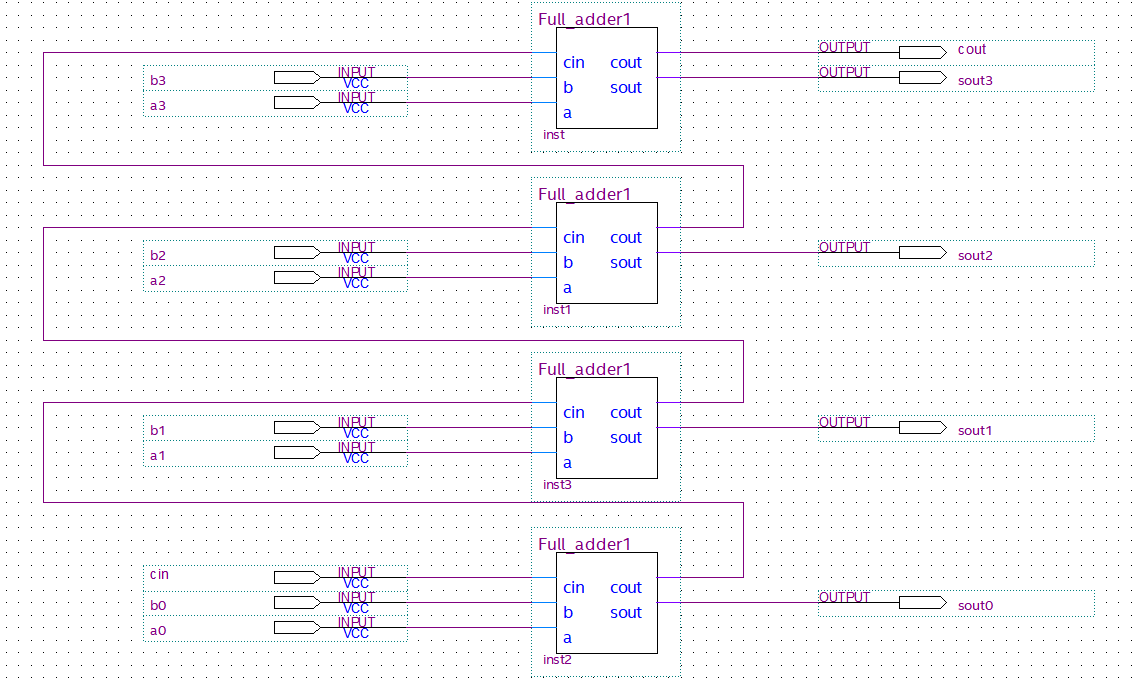

这里实现四位加法器的过程与实现一位加法器的过程相同,只需要将一位全加器设置为可调用元件,然后继续进行绘制即可,这里我们的四位全加器的原理图如下:

代码设计

这里我们需要添加一个代码文件,然后使用 Verilog 语言进行编程,Verilog 语言的语法参考前面的博客:

这里直接给出我们设计好的代码:

半加器:

module Hallfadder

(

input a,b,

output cout,sum

);

assign sum = a^b;

assign cout = a&b;

endmodule

一位全加器:

module Full_adder1

(

input a,b,

output sum,

output cout,

input cin,

);

assign{cout,sum} = a+b+cin;

endmodule

四位全加器:

module Full_adder4

(

input [3:0] a,

input [3:0] b,

input cin,

output [3:0] sum,

output cout

);

assign{cout,sum} = a+b+cin;

endmodule

编译仿真

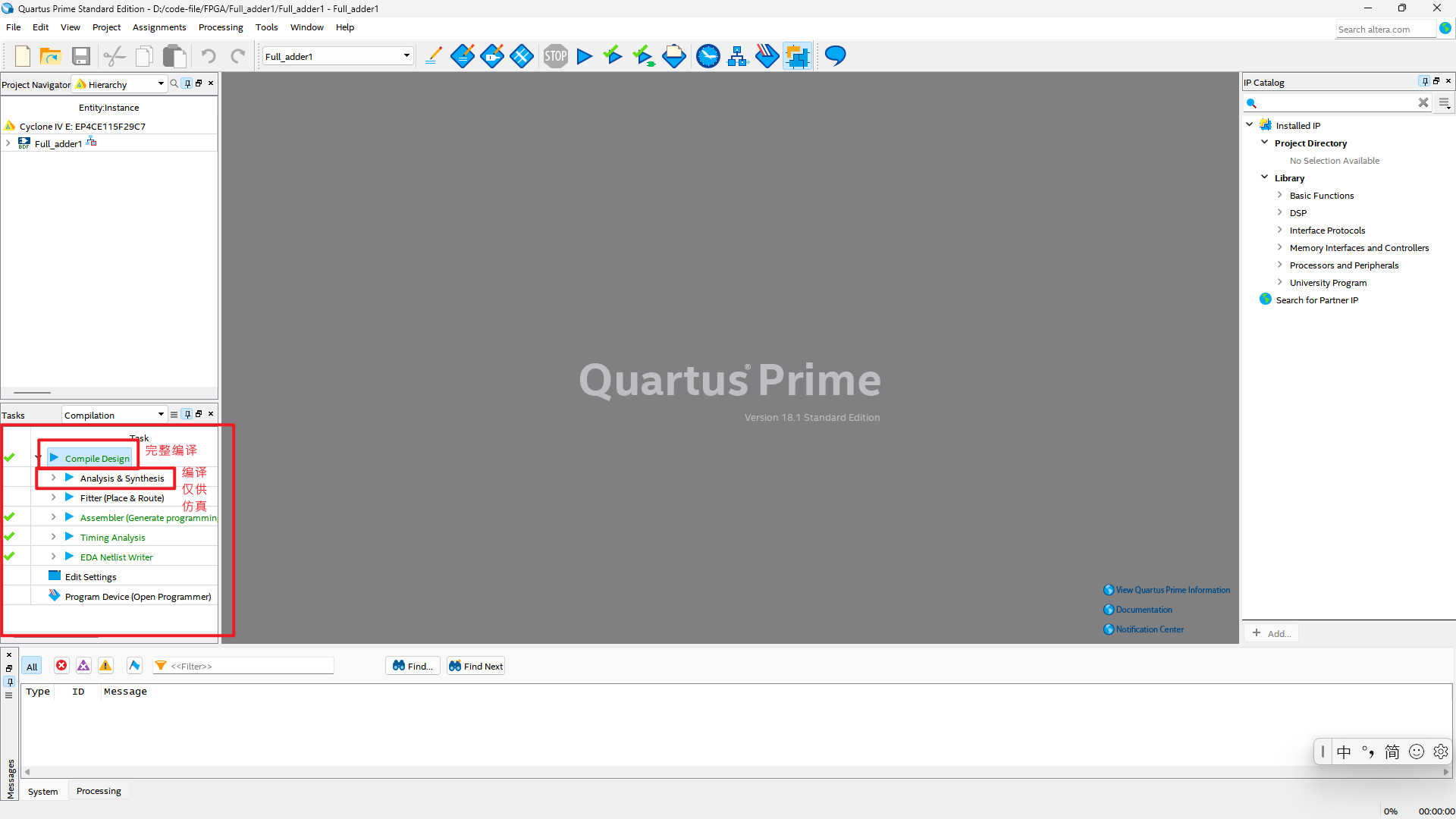

这里编译仿真我们以一位全加器为例:

原理图编译仿真

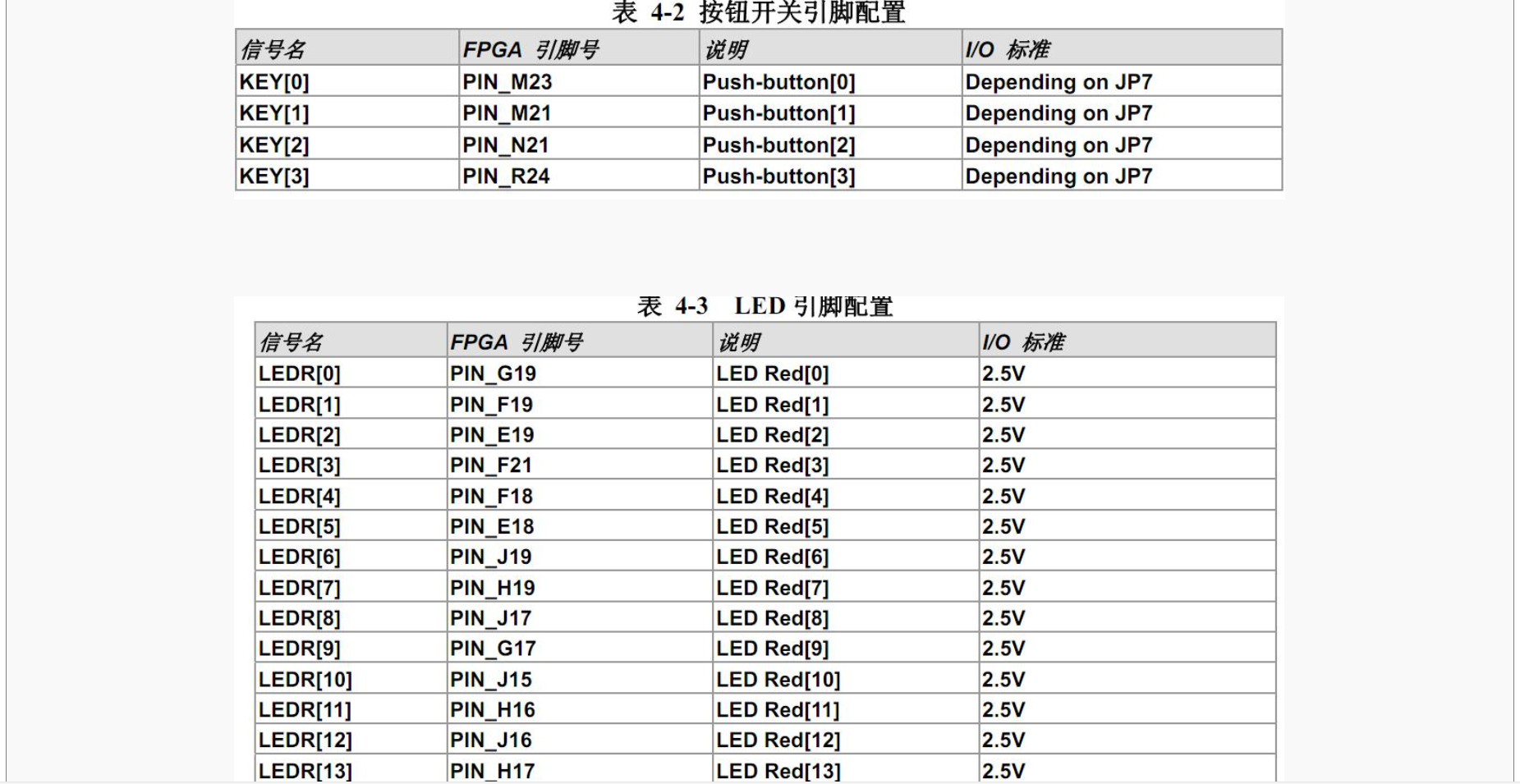

这里我们直接点击编译即可:

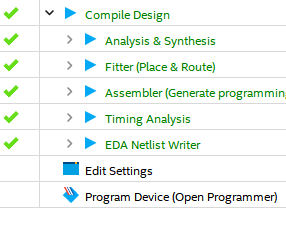

这里给出两种编译方式,如果我们只需要编译仿真,我们就直接选择 Analysis & Synthesis 编译选项即可,要是我们有烧录的需要,我们就需要选择 Compile Design 编译选项,当然,我们使用完整编译需要的时间也就更长,这里我们直接选择完整编译:

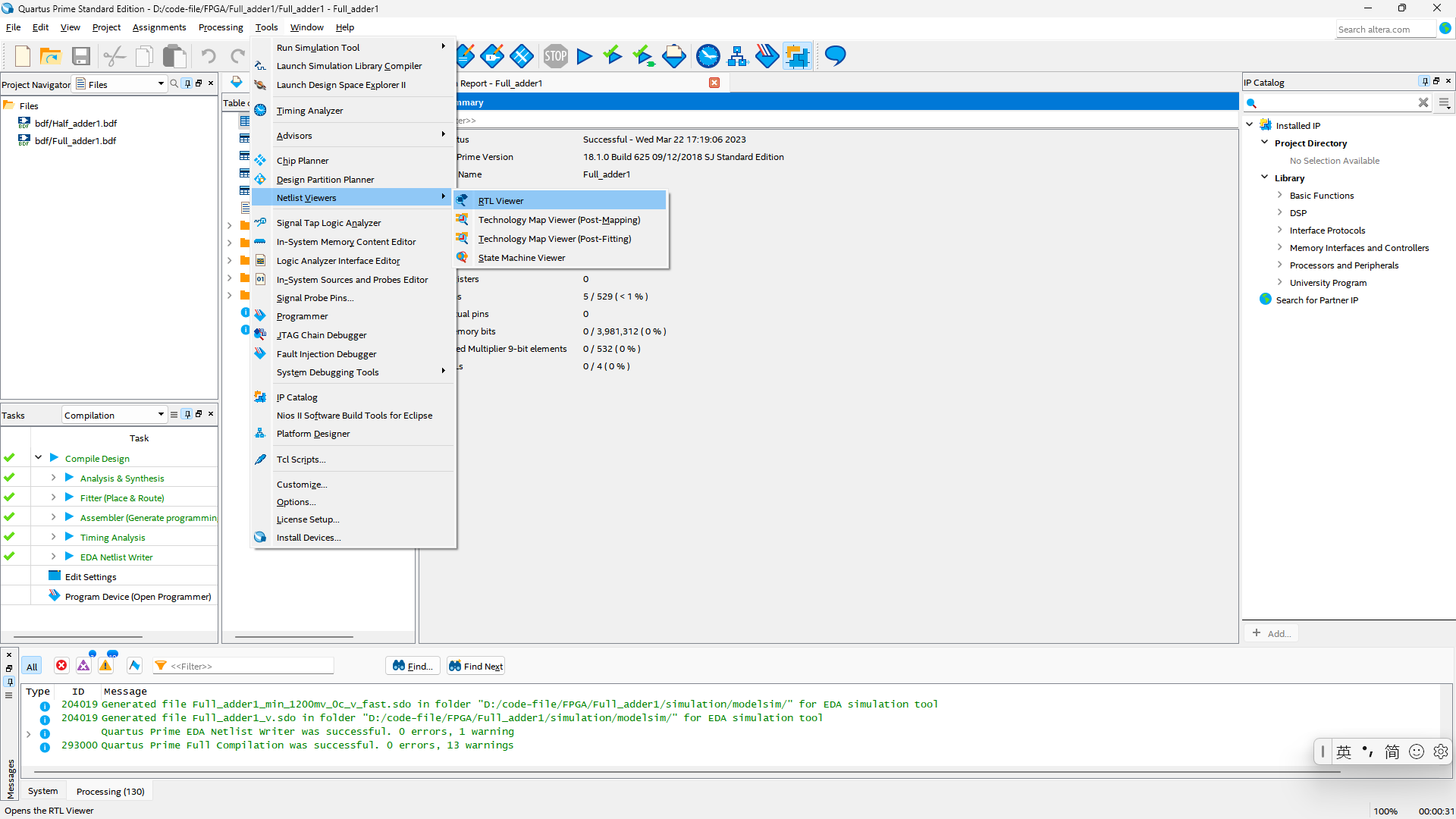

这里我们已经编译成功了,下一步我们就可以开始仿真了,首先我们先生成对应的电路图:

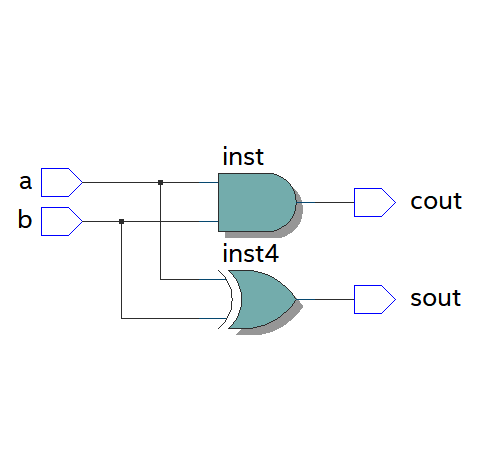

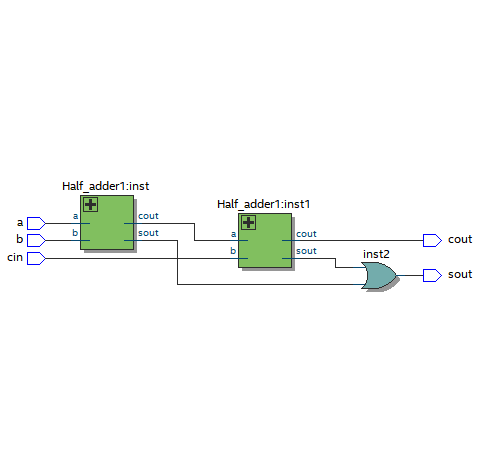

然后我们就可以看到我们生成的电路图:

半加器:

一位全加器:

四位全加器:

然后我们以一位全加器为例,来介绍图和通过原理图进行仿真

首先我们在编译完成生成原理图之后,需要添加一个波形图文件:

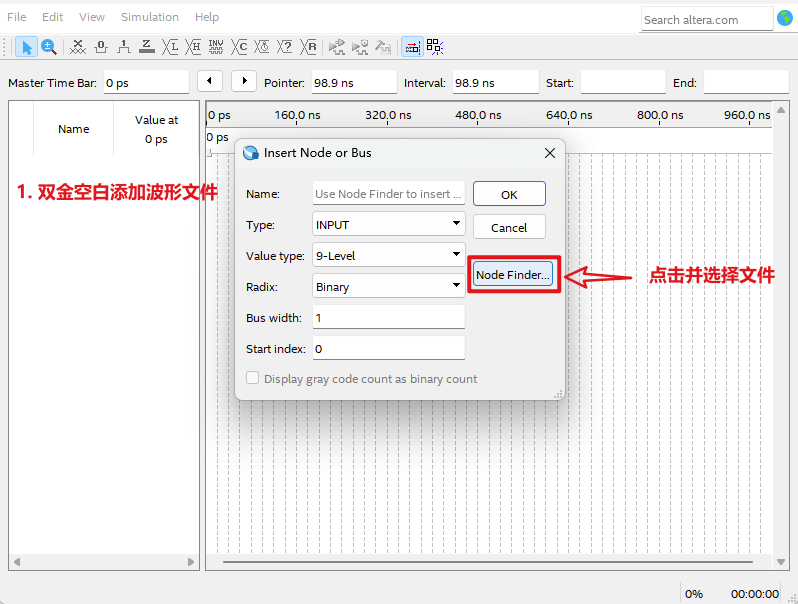

然后我们需要双击空白处添加波形文件:

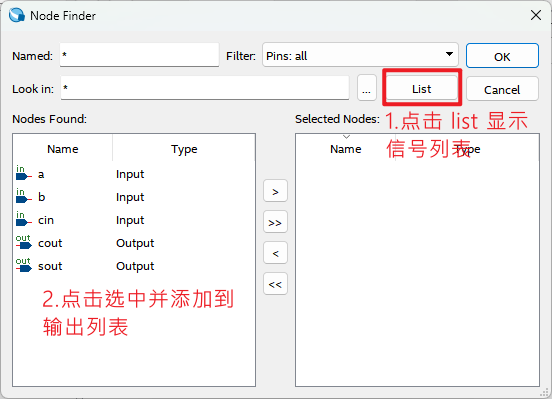

下面我们选择要输出的信号:

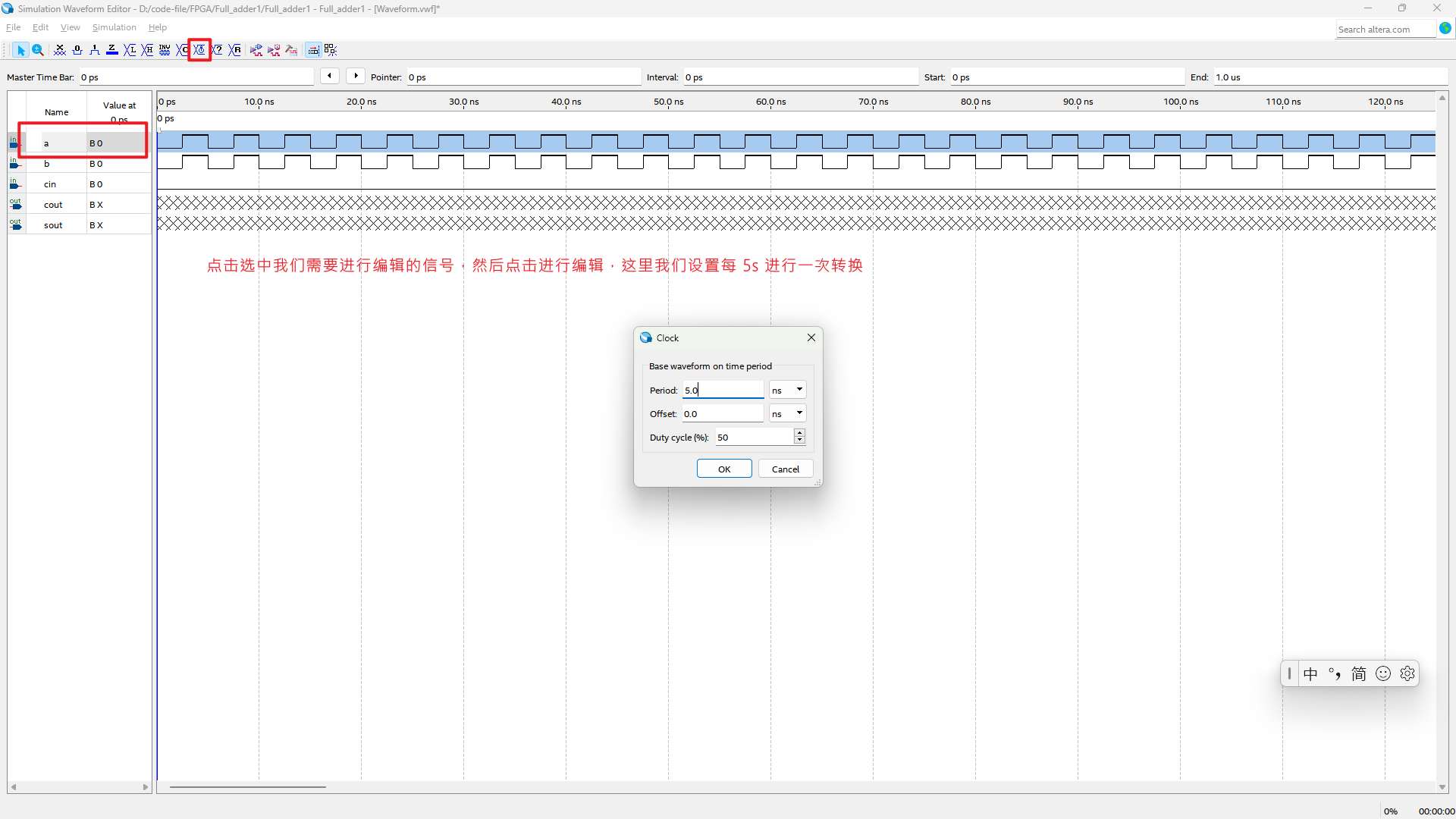

编辑我们的输入信号:

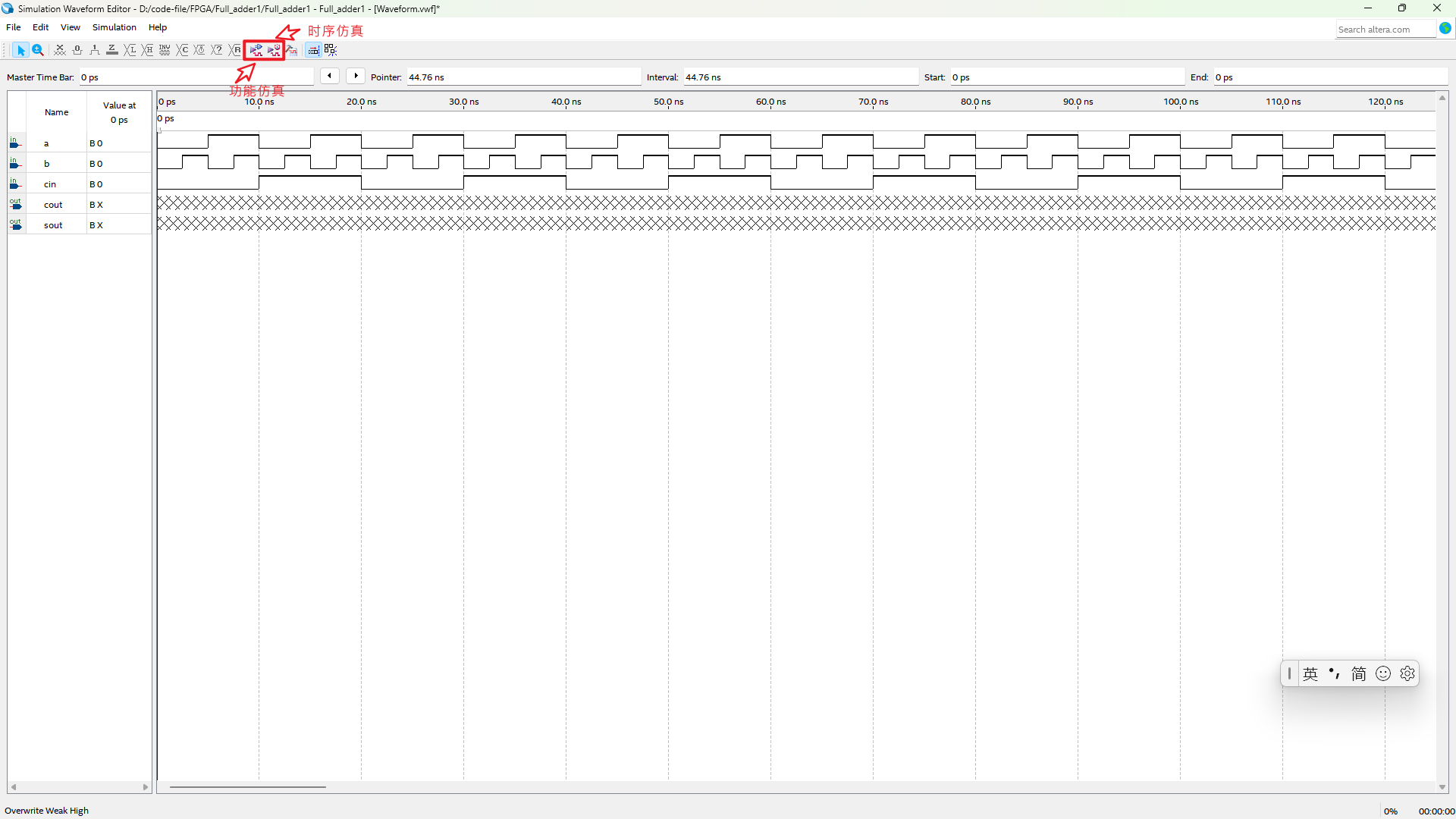

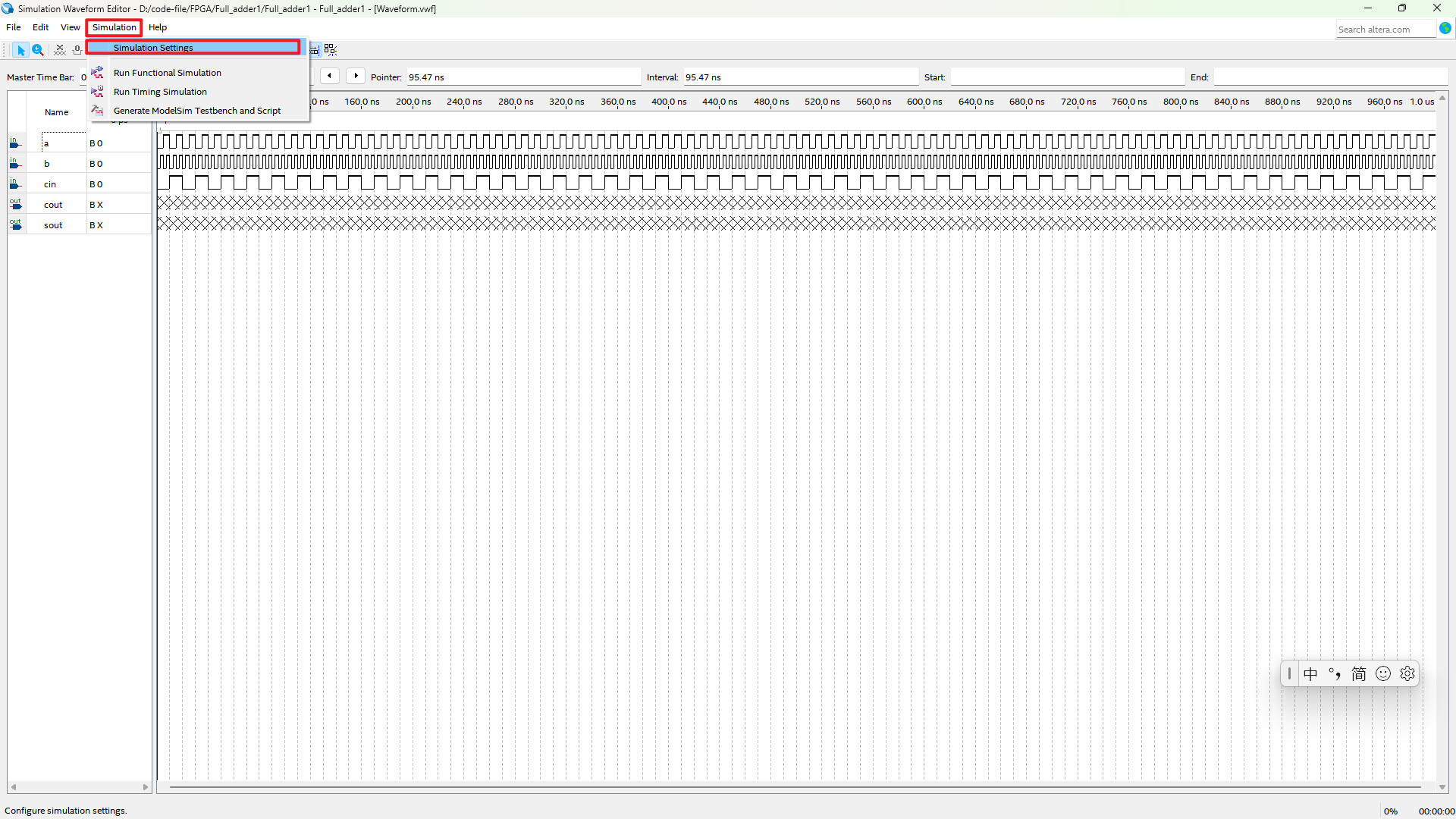

在我们将所有的输入信号都编辑完成之后,我们开始进行仿真:

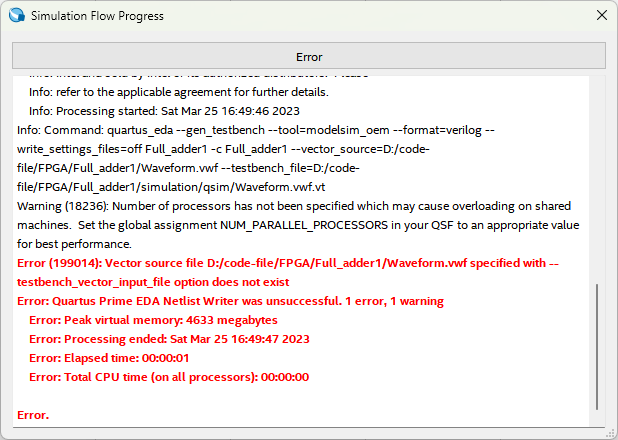

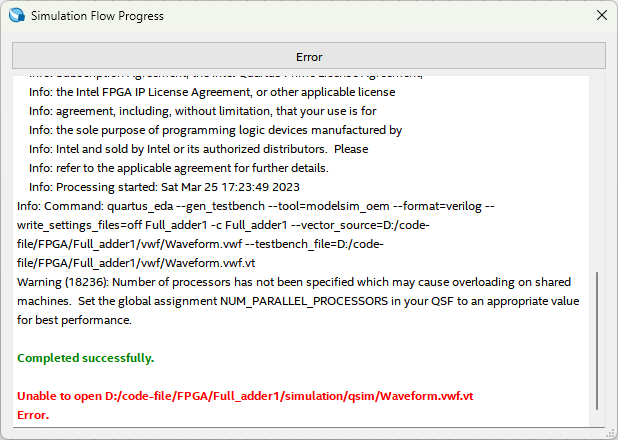

如果在仿真时出现如下报错:

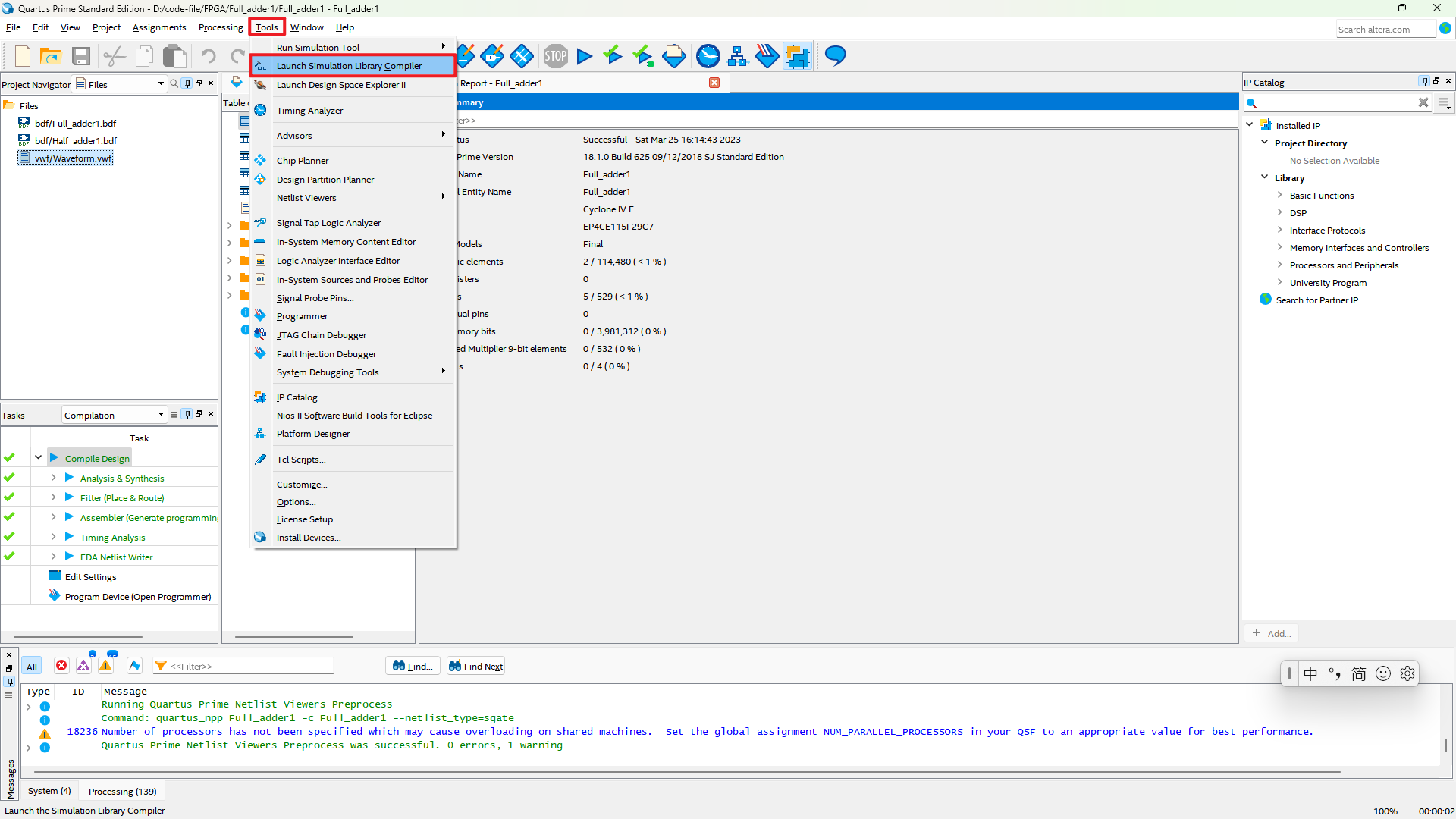

这里我们需要手动添加 Modelsim:

然后点击 start compilation 没有报错即为成功

然后我们再次运行还有可能会出现如下报错:

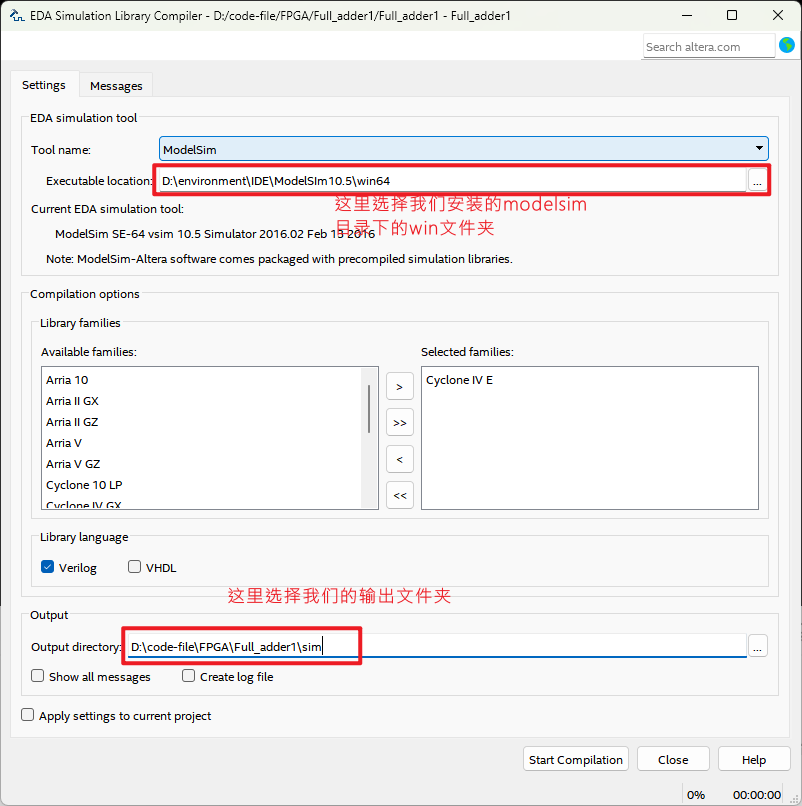

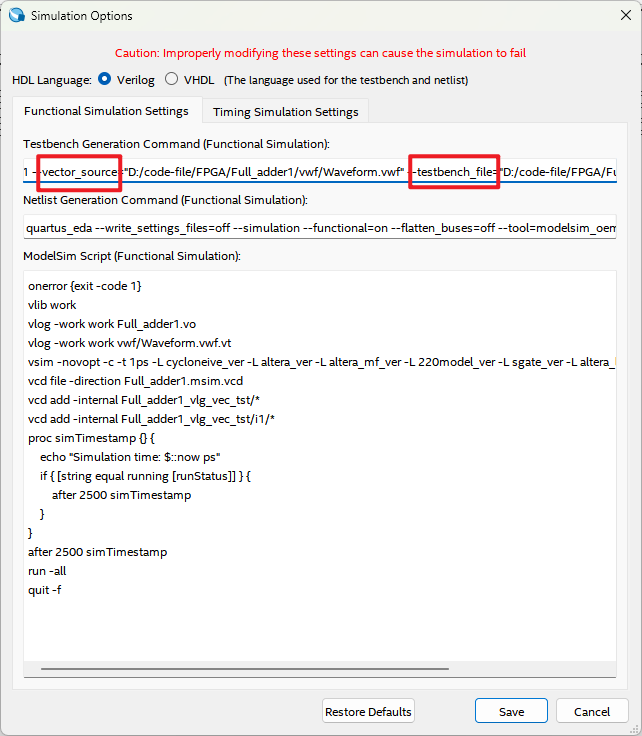

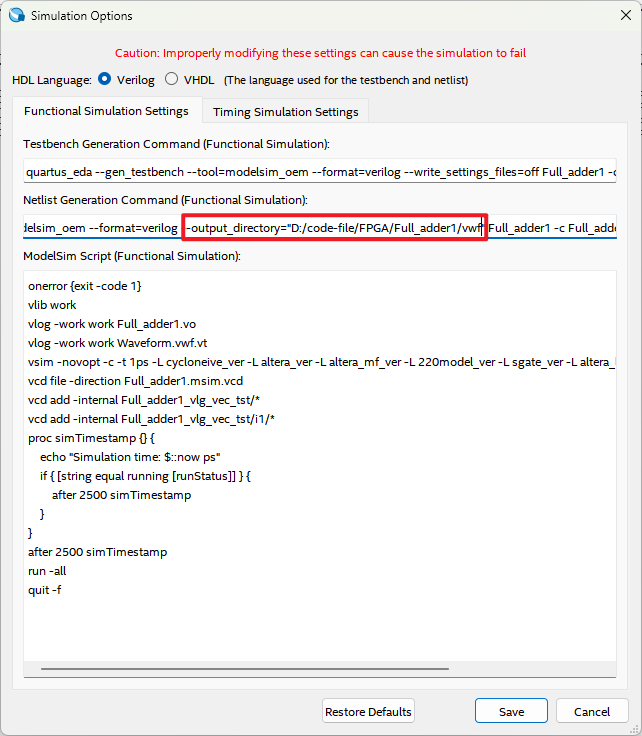

我们需要修改设置:

这里我们要保证我们 vector_source 和 testbench_file 的文件名称要一致,都选择我们的仿真文件即可,并且一定要选择好路径

同时这里我们需要经路径设置为我们刚存放仿真文件的文件夹的上级目录

注意:这里我们没有进行全部编译也有可能会进行报错,并且我们在修改仿真设置的时候,这里我们的时序和功能仿真对应的选项都要进行修改

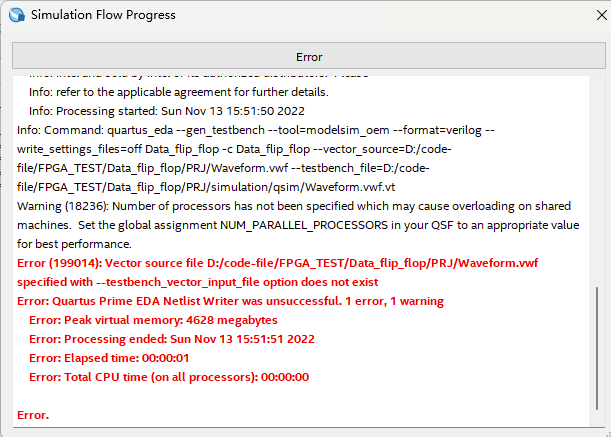

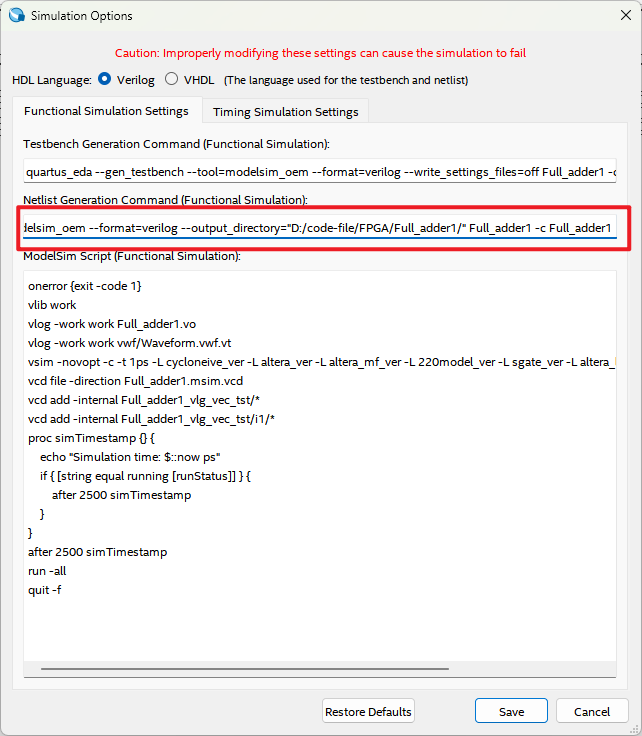

如果再次出现如下报错:

就说明刚刚我们在修改配置文件的时候有错误,直接修改下图位置即可:

这里修改为我们刚存储波形图文件的位置

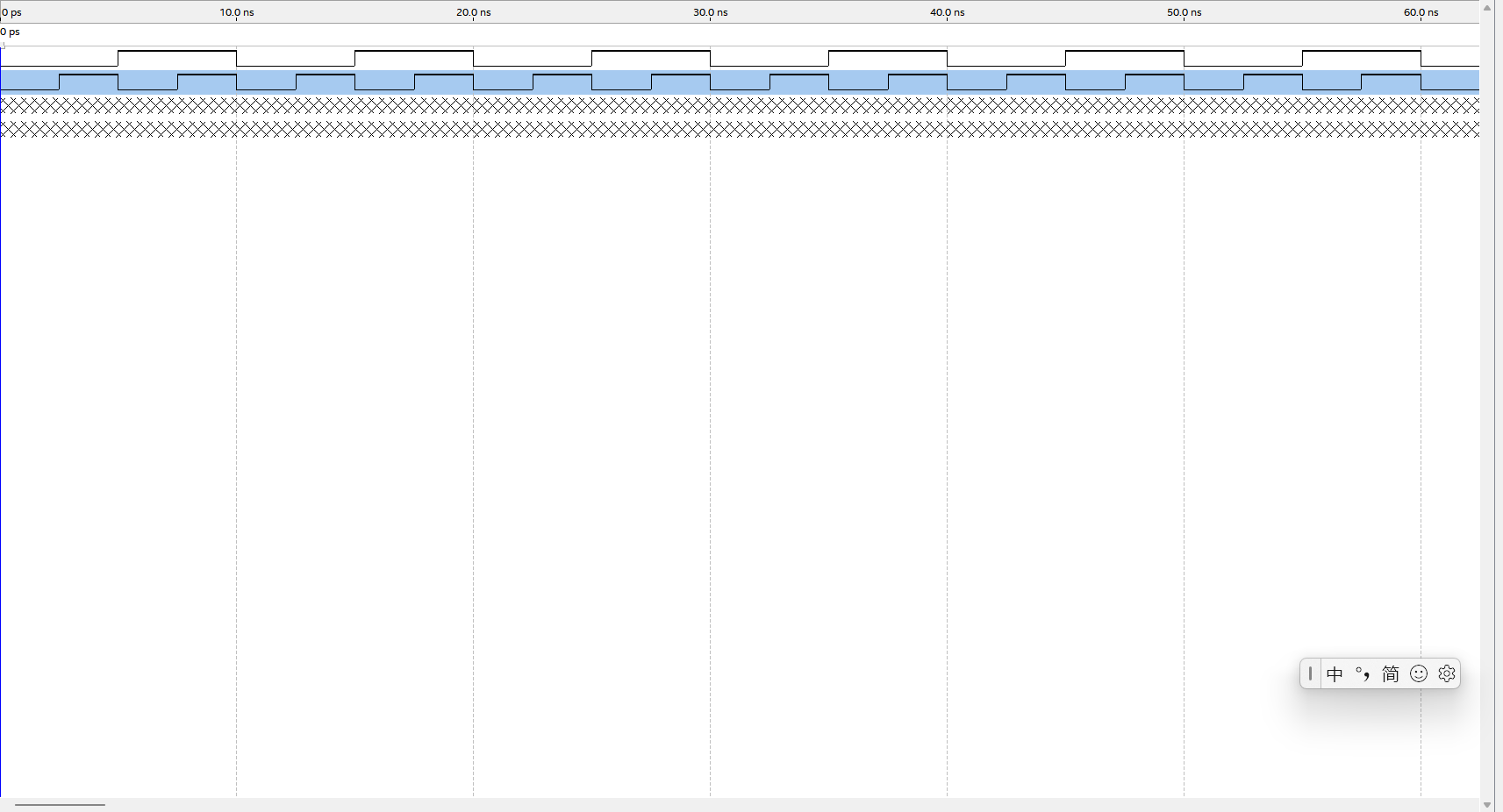

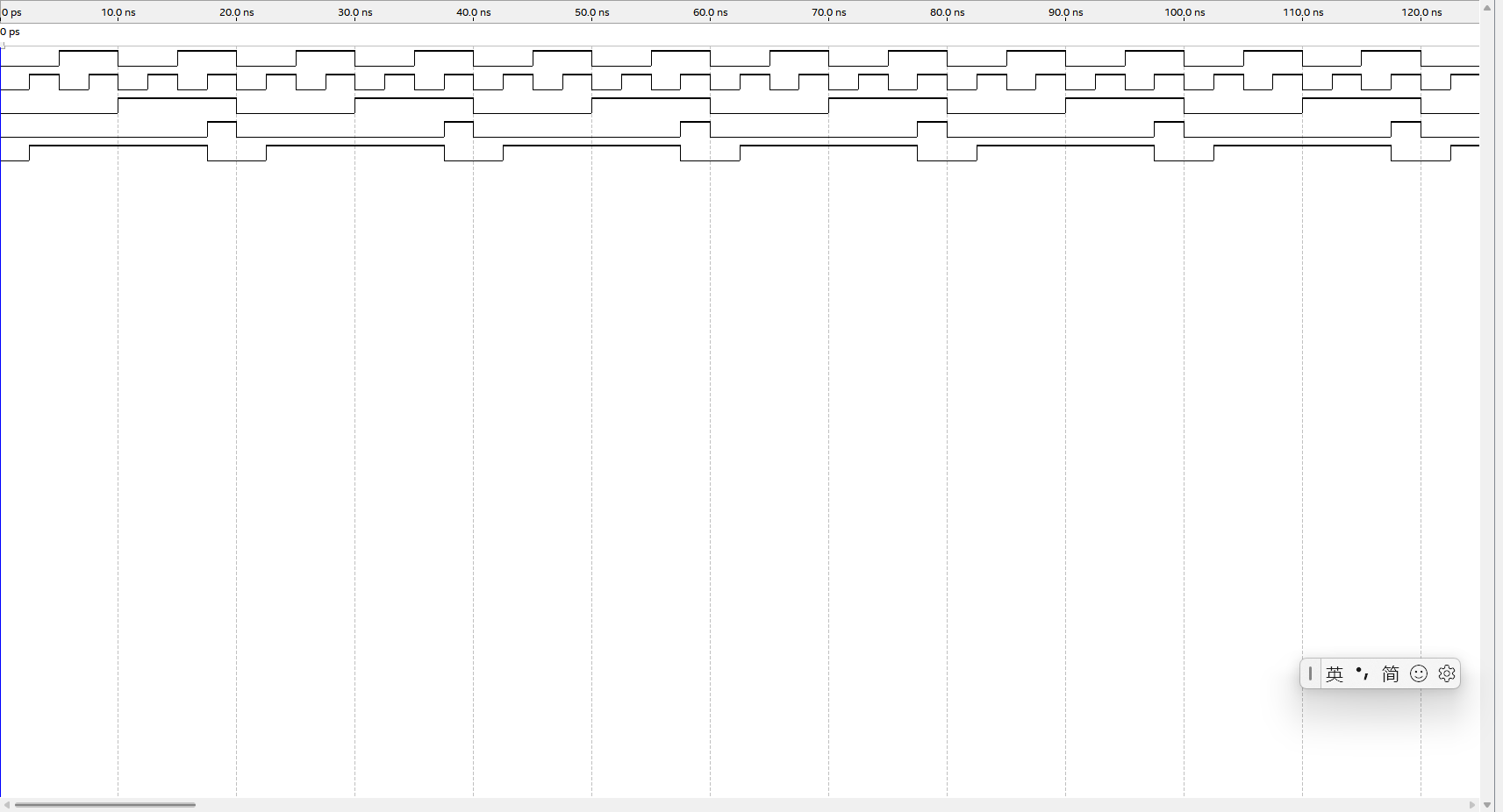

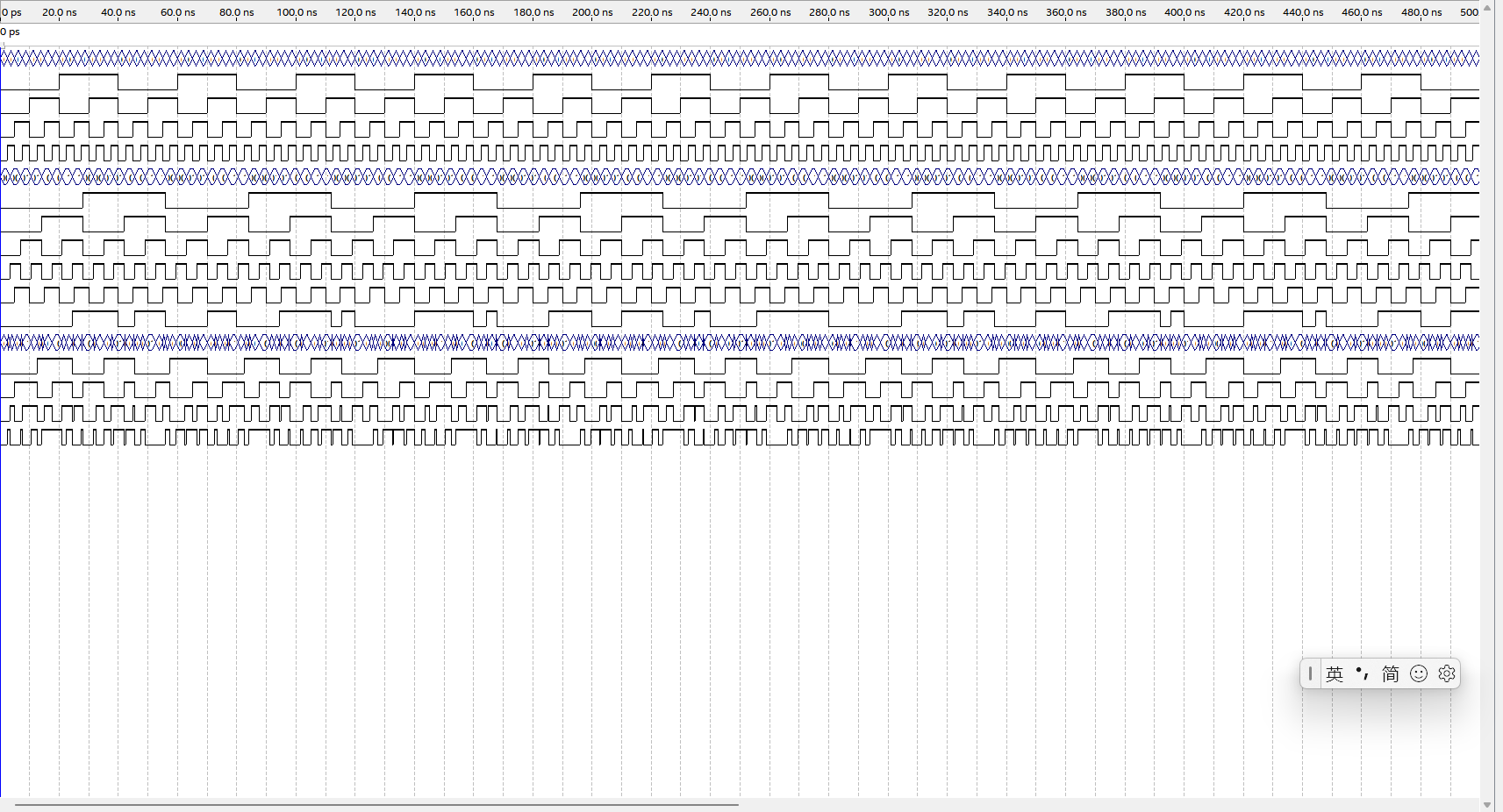

下面给出半加器、一位全加器、四位全加器的仿真结果:

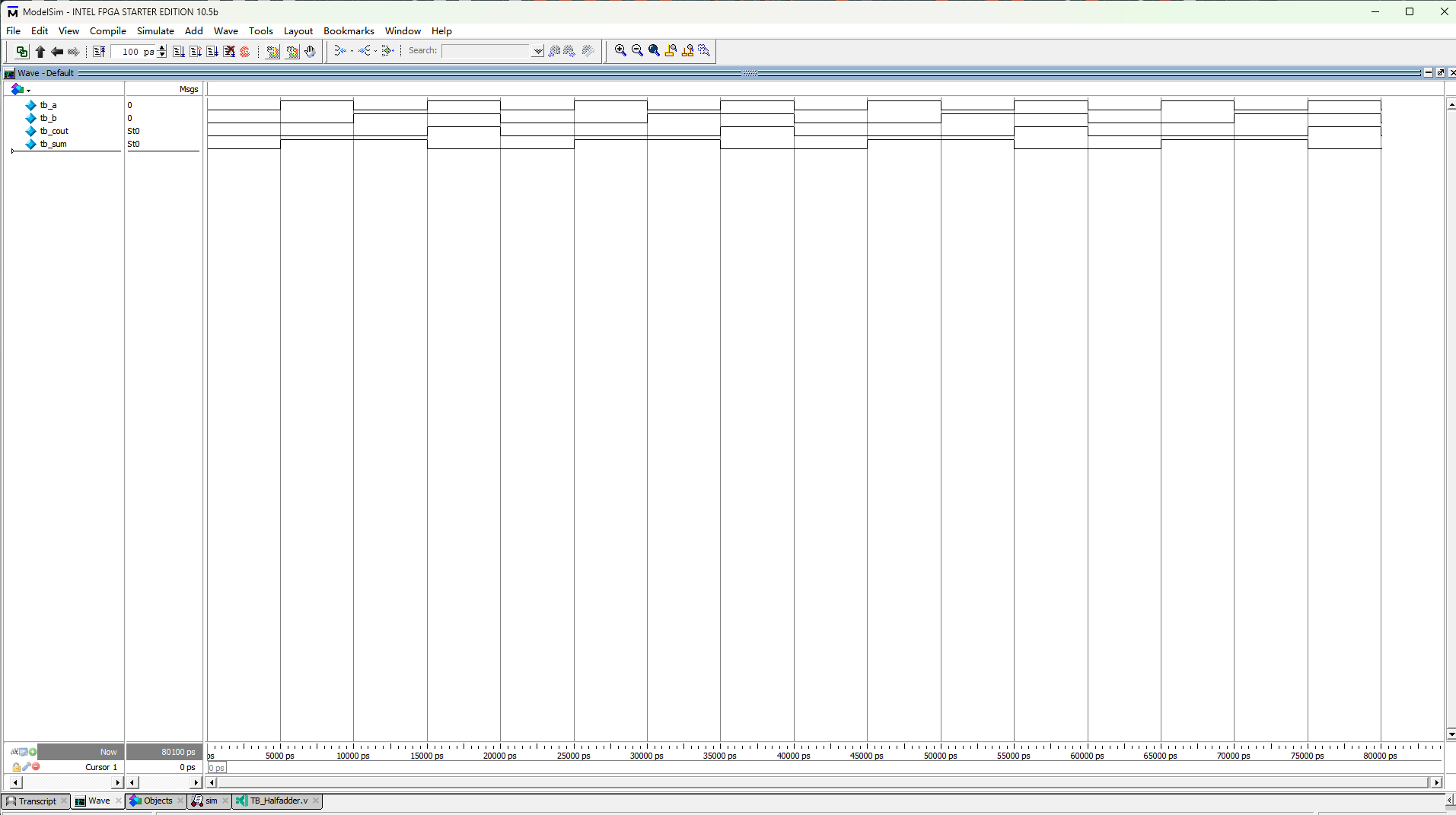

半加器

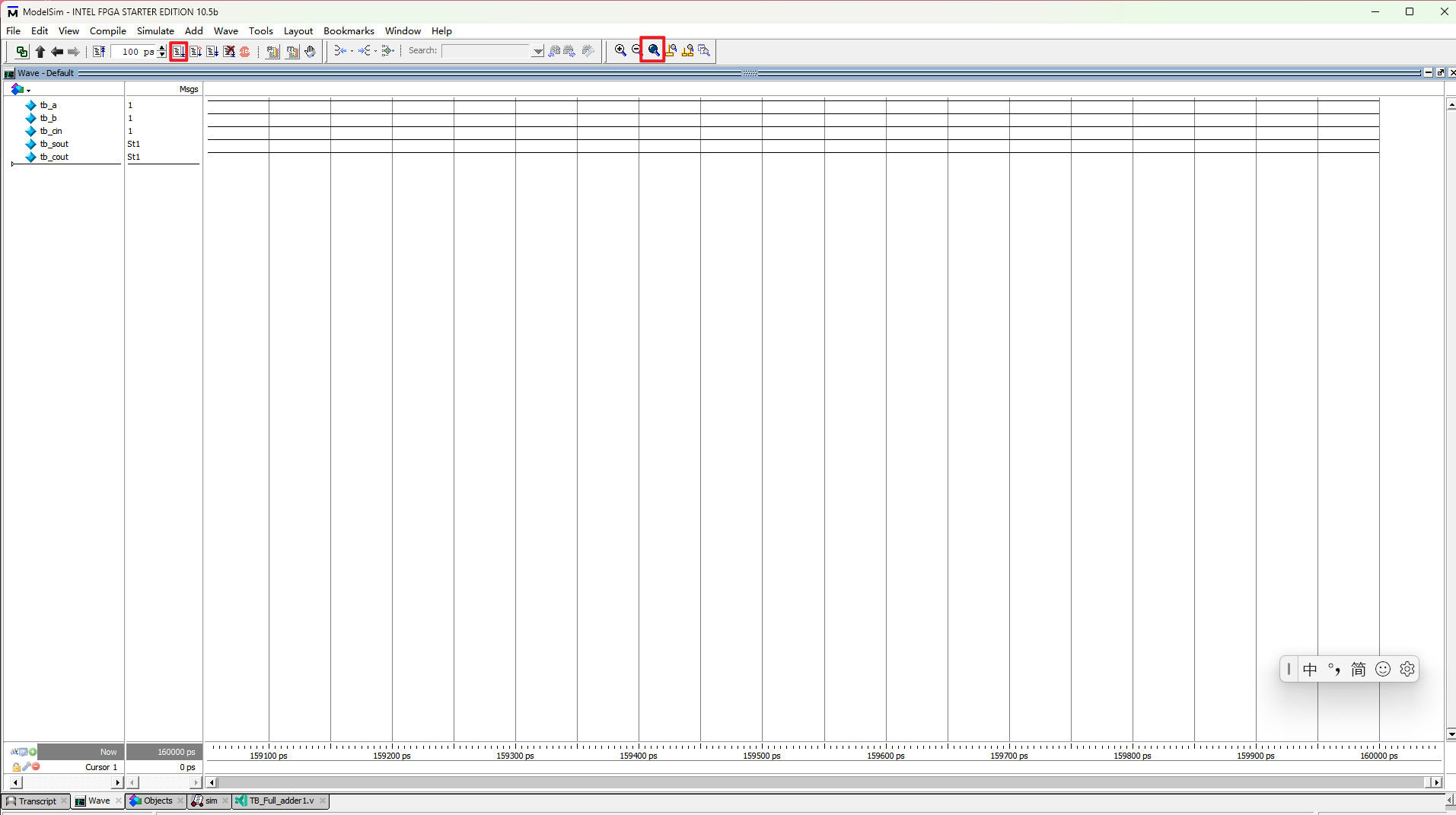

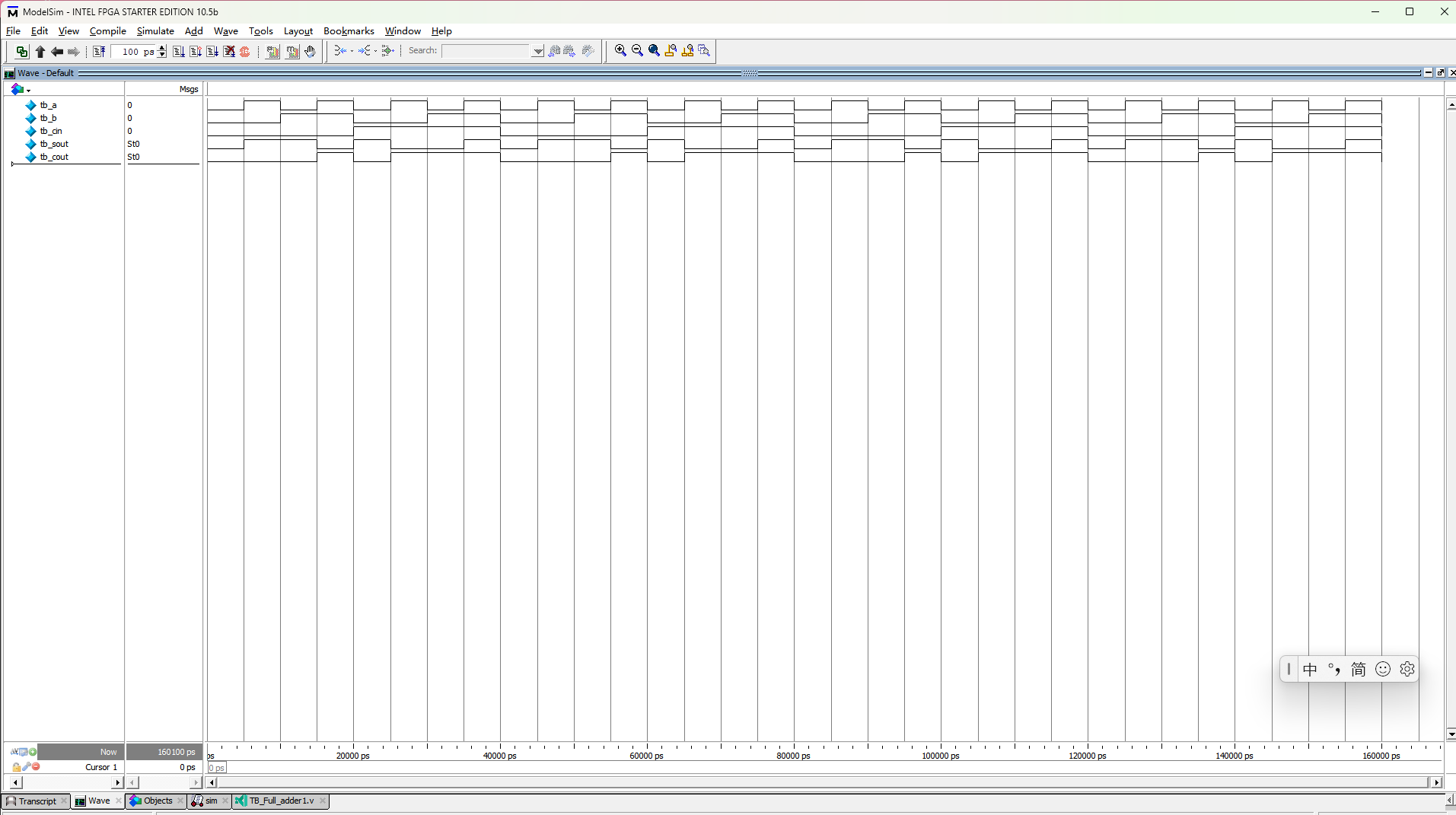

一位全加器

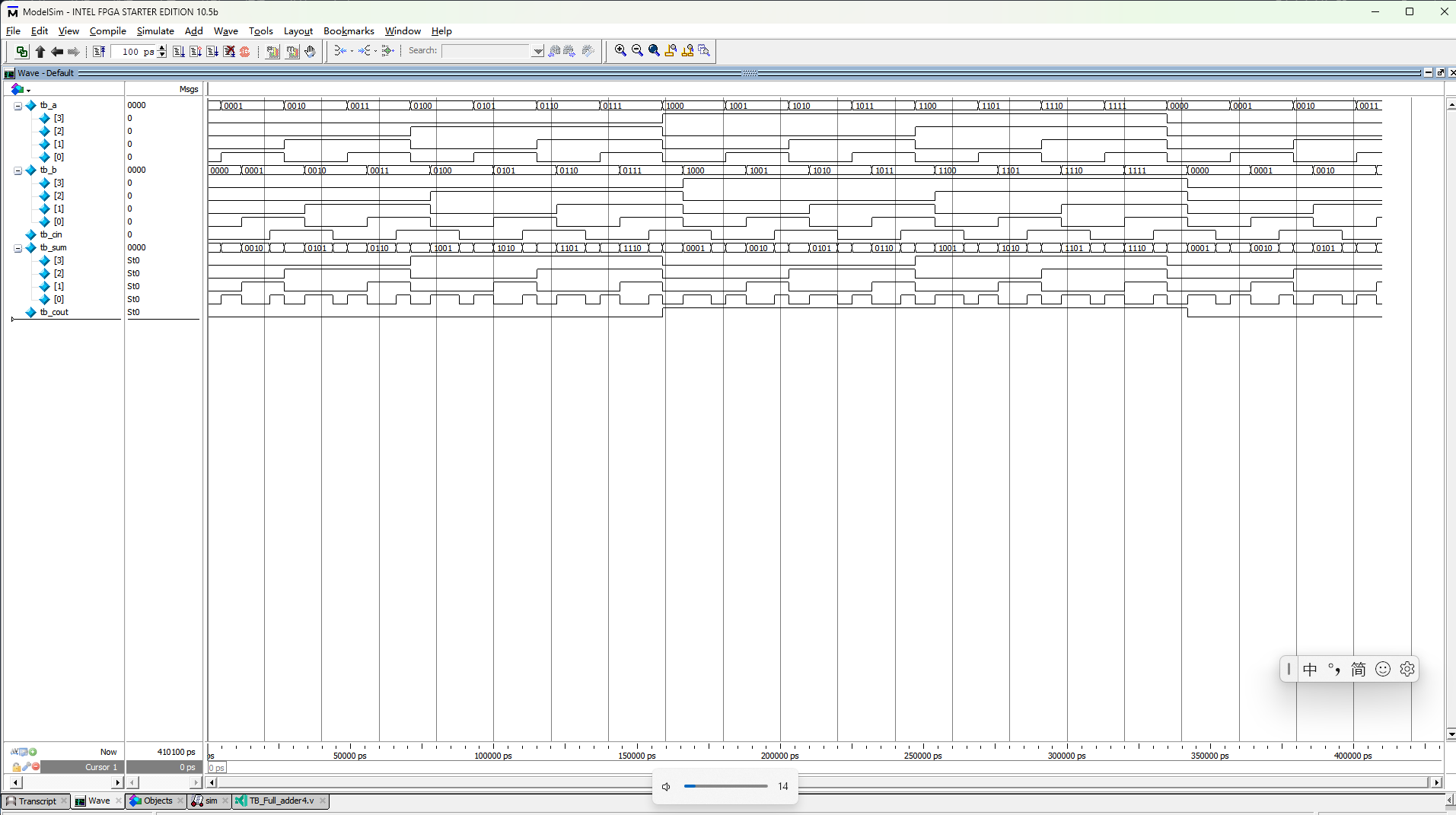

四位全加器

代码编译仿真

我们同样是创建一个新的 verilog 代码文件作为仿真文件,由于我们已经在前面的博客中介绍过如何进行代码仿真了,这里我们直接给出仿真代码:

`timescale 1ns/1ns

module TB_Full_adder1(); // 设置仿真引脚

reg tb_a ;

reg tb_b ;

reg tb_cin ;

wire tb_sout ;

wire tb_cout ;

Full_adder1 u_Full_adder1( // 绑定引脚,绑定仿真文件与源代码文件中对应的引脚

.a (tb_a) ,

.b (tb_b) ,

.cin (tb_cin) ,

.cout (tb_cout) ,

.sum (tb_sout)

);

parameter CYCLE = 40; // 设置周期

always # 5 tb_a = ~tb_a ; // 设置输入变量

always # 10 tb_b = ~tb_b ;

always # 20 tb_cin = ~tb_cin ;

initial begin // 初始化变量

tb_a = 1'b0 ;

tb_b = 1'b0 ;

tb_cin = 1'b0 ;

#(CYCLE * 4) ; // 设置到达指定周期停止

$stop ;

end

endmodule

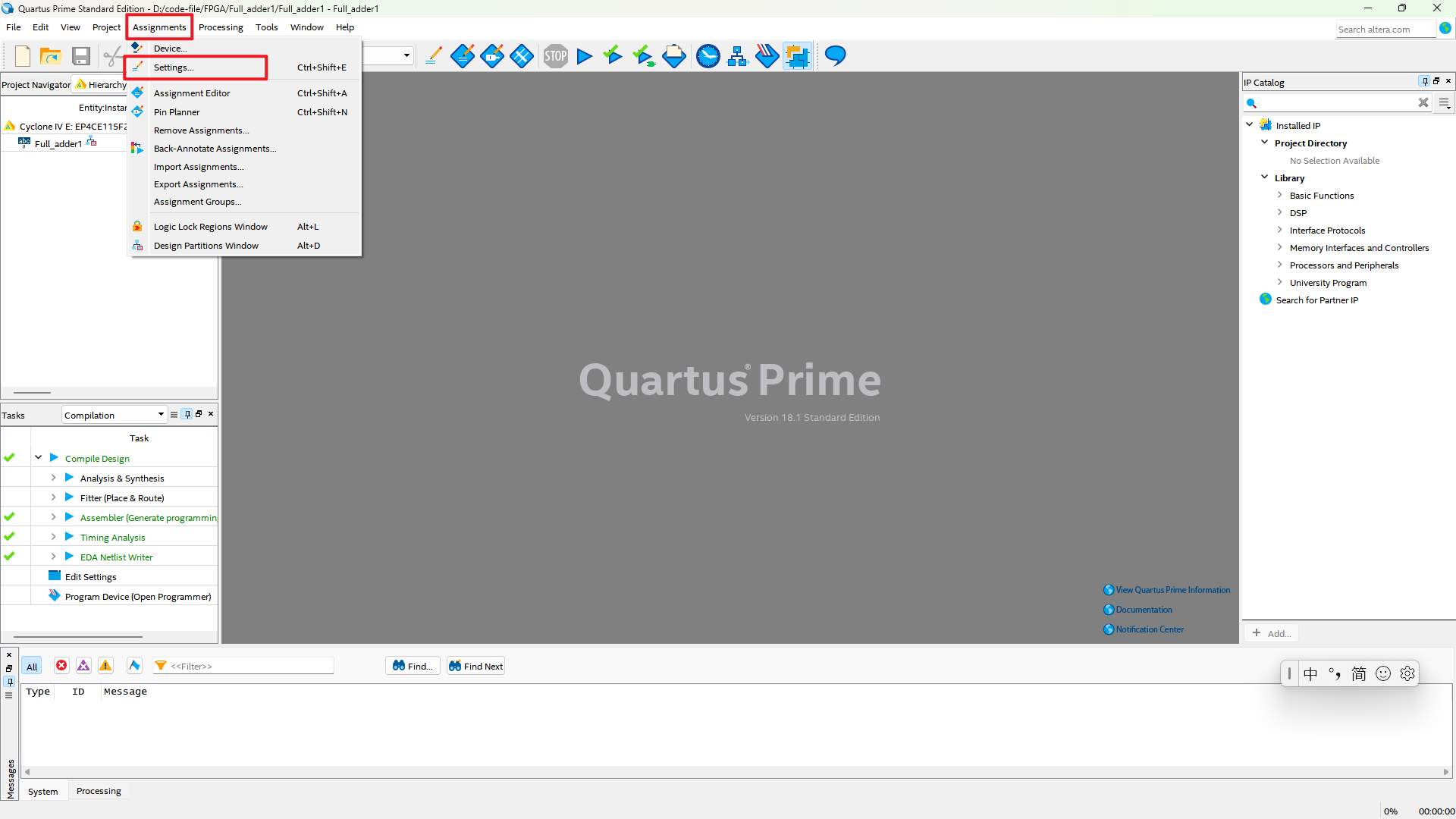

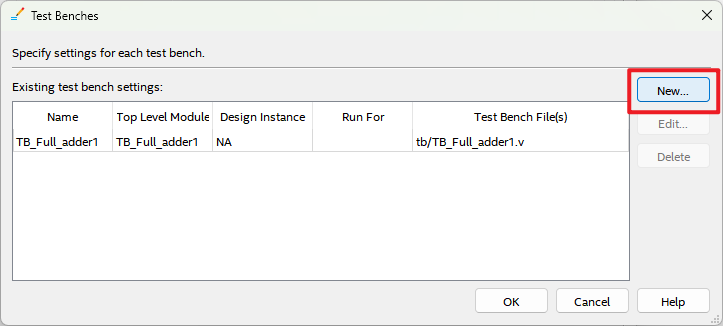

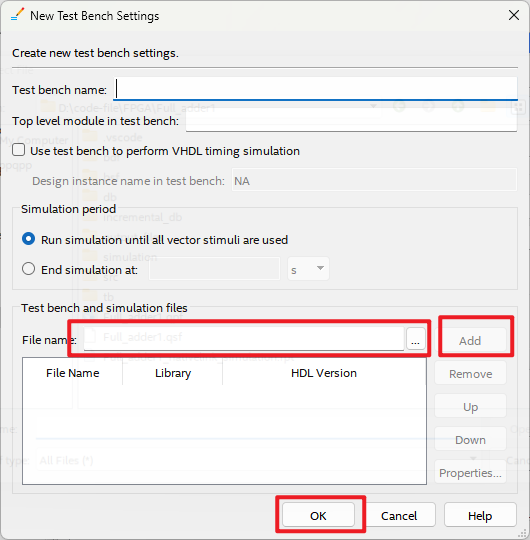

然后我们选择进行完整编译,编译成功后,我们在进行仿真之前,我们需要绑定仿真文件,下面给出完整步骤:

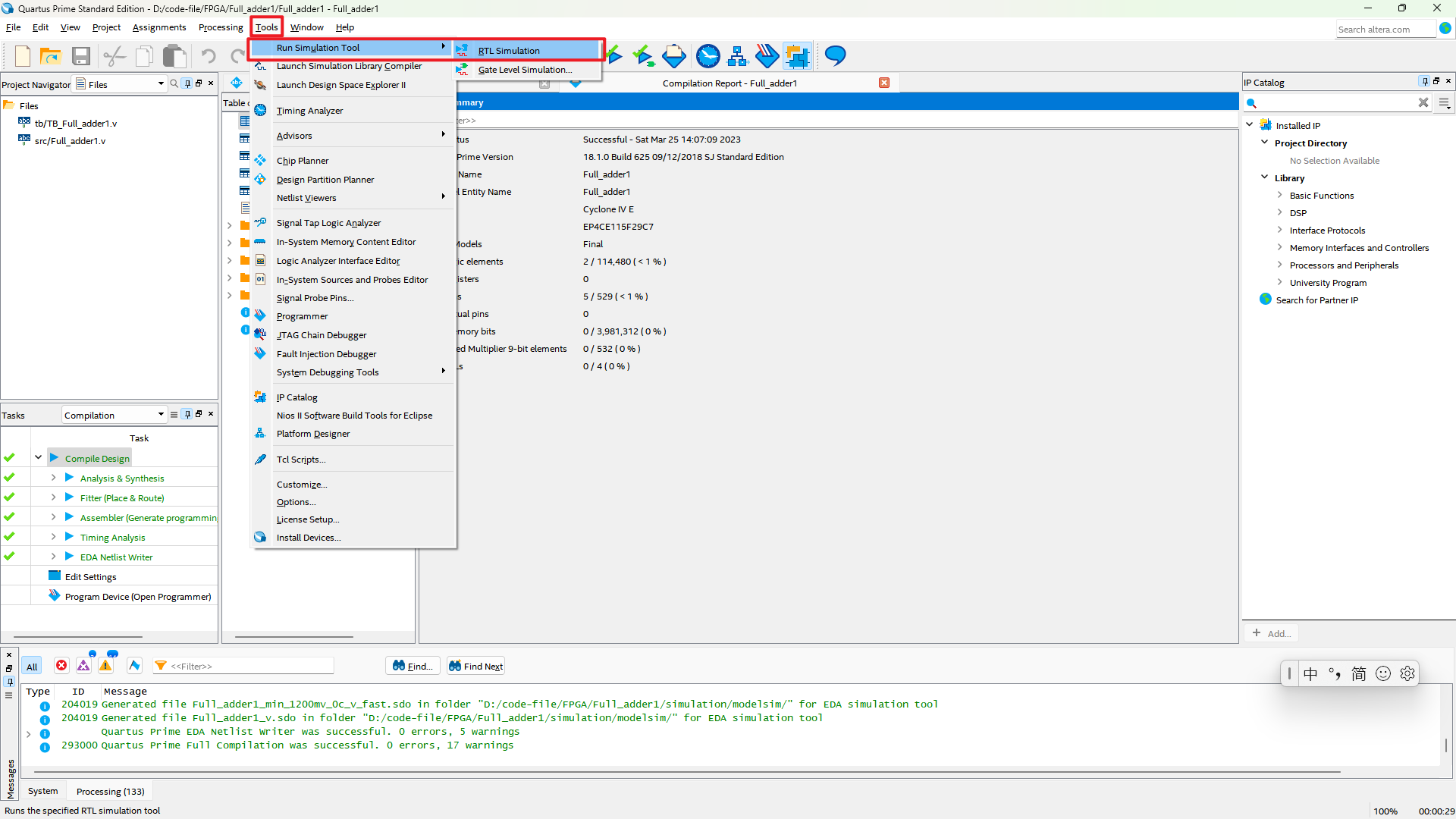

成功添加 testbench 仿真文件之后重新编译,然后就可以进行仿真了:

我们可以先点击运行,然后点击右面的缩放,最后我们只需要缩放到自己需要的大小即可,我们仿真后生成的波形如下:

波形与我们需要的完全相同,说明我们的代码没有问题

这里我们直接给出半加器和四位全加器的仿真代码和波形图:

半加器:

`timescale 1ns/1ns

module TB_Halfadder();

reg tb_a ;

reg tb_b ;

wire tb_cout ;

wire tb_sum ;

Halfadder u_Halfadder(

.a (tb_a) ,

.b (tb_b) ,

.cout (tb_cout) ,

.sum (tb_sum)

);

parameter CYCLE = 20;

always # 5 tb_a = ~tb_a ;

always # 10 tb_b = ~tb_b ;

initial begin

tb_a = 1'b0 ;

tb_b = 1'b0 ;

#(CYCLE * 4) ;

$stop ;

end

endmodule

四位全加器:

`timescale 1ns/1ns

module TB_Full_adder4();

reg [3:0] tb_a ;

reg [3:0] tb_b ;

reg tb_cin ;

wire [3:0] tb_sum ;

wire tb_cout ;

Full_adder4 u_Full_adder4(

.a (tb_a) ,

.b (tb_b) ,

.cin (tb_cin) ,

.sum (tb_sum) ,

.cout (tb_cout)

);

parameter CYCLE = 205;

always begin

# 5 tb_a = tb_a+1 ;

# 7 tb_b = tb_b+1 ;

# 10 tb_cin = ~tb_cin ;

end

initial begin

tb_a = 4'b0000 ;

tb_b = 4'b0000 ;

tb_cin = 0 ;

#(CYCLE * 2) ;

$stop ;

end

endmodule

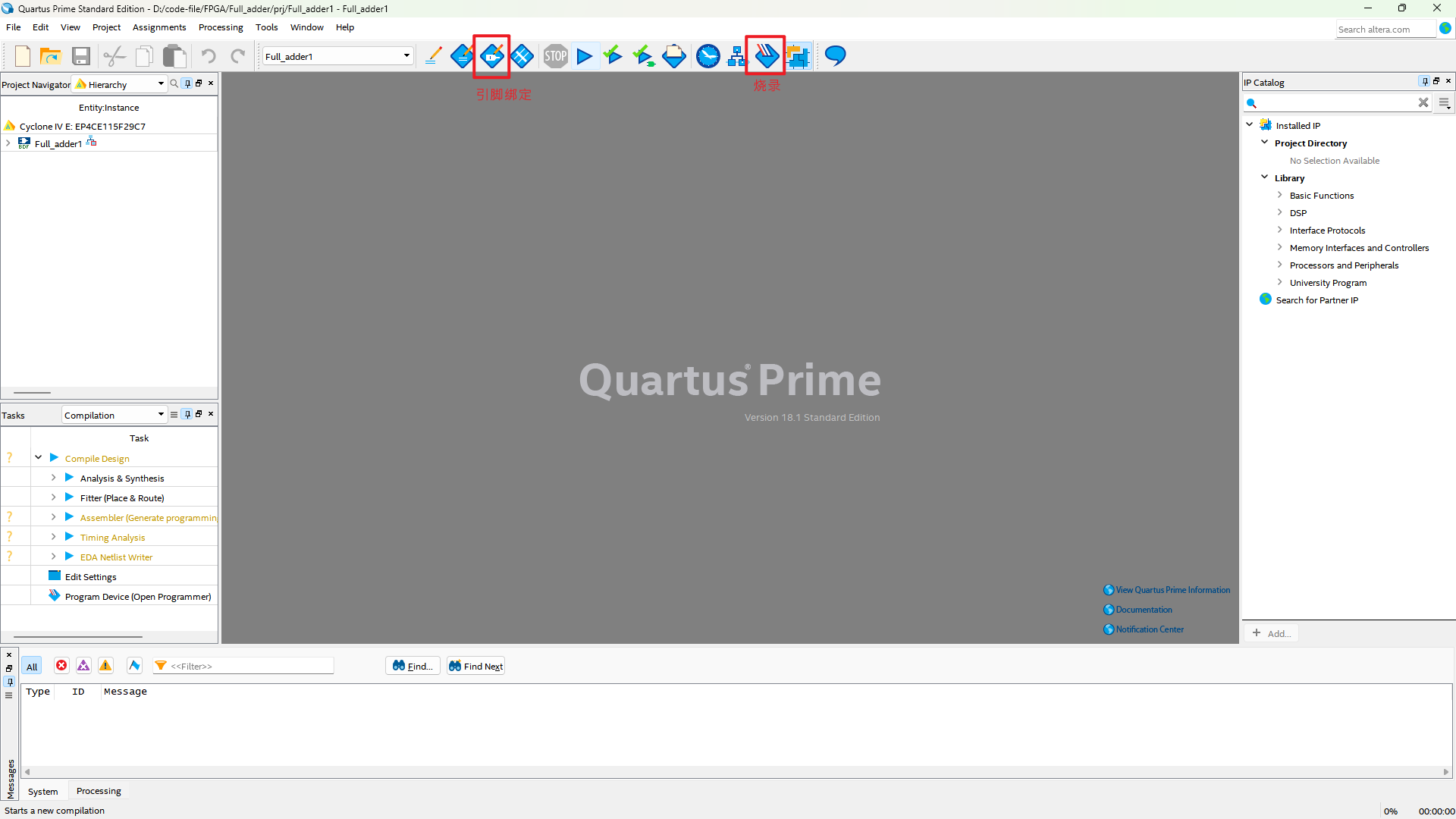

烧录测试

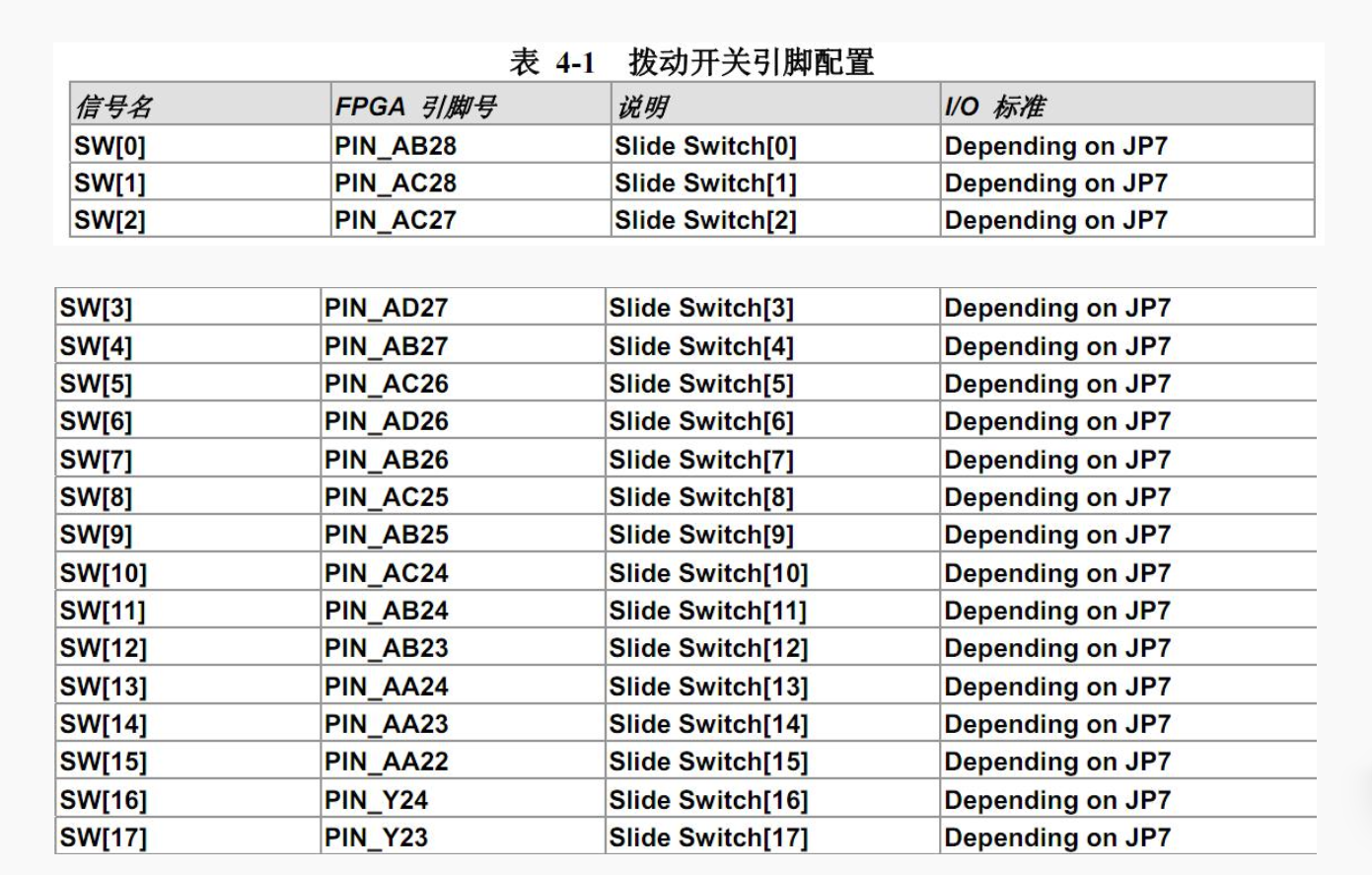

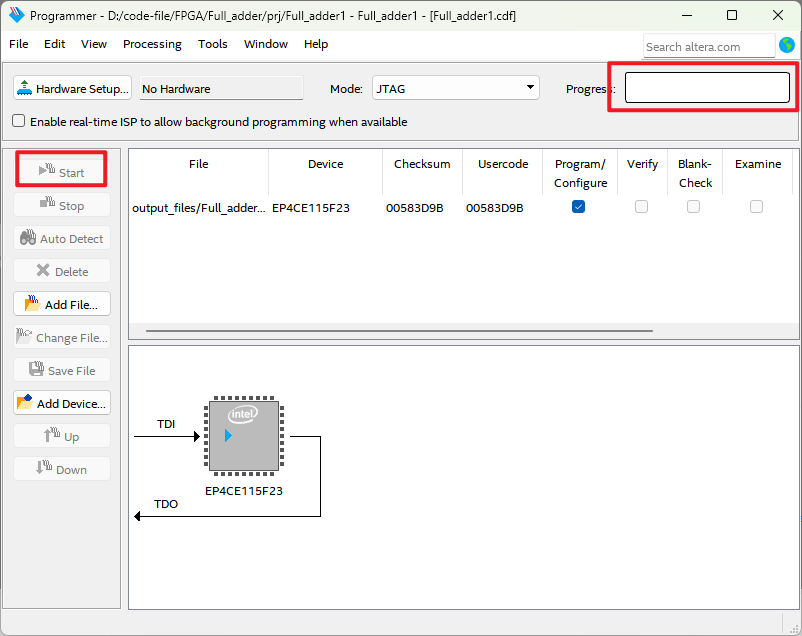

首先我们给出对应引脚:

这里我们先进行引脚的绑定:

下面分别给出一位全加器和四位全加器对应的引脚:

一位全加器:

四位全加器:

下面我们给出一位全加器与四位全加器的实验结果:

一位全加器:

四位全加器:

浙公网安备 33010602011771号

浙公网安备 33010602011771号