FPGA 入门 —— 加法器

FPGA 入门 —— 加法器

加法器

在电子学中,加法器(英语:adder)是一种用于执行加法运算的数位电路部件,是构成电子计算机核心微处理器中算术逻辑单元的基础。在这些电子系统中,加法器主要负责计算地址、索引等数据。除此之外,加法器也是其他一些硬件,例如二进制数的乘法器的重要组成部分

尽管可以为不同计数系统设计专门的加法器,但是由于数位电路通常以二进制为基础,因此二进制加法器在实际应用中最为普遍。在数字电路中,二进制数的减法可以通过加一个负数来间接完成。为了使负数的计算能够直接用加法器来完成,计算中的负数可以使用二补数(补码)来表示

半加器

在了解什么是全加器之前,我们需要知道什么是半加器:

(英语:half adder)的功能是将两个一位二进制数相加。它有两个输出:

和:记作 S,来自对应的英语 Sum

进位:记作 C,来自对应的英语 Carry一位的数字。因此,这两个一位二进制数的和用十进制表示即等于2C + S

下图是一个最简单的半加器设计:

使用一个异或门来产生 S,一个与门来产生 C 和 S 的布尔逻辑是 A'B+AB',进位 C 的布尔逻辑是 AB。如果再添加一个或门处理两个半加器的进位信号,就构成了一个全加器

半加器将两个输入位加和,产生进位与和,是半加器的两个输出。半加器的输入变量叫做被加数或被加位。输出变量为和与进位

半加器的真值表如下:

| a | b | s | c |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

全加器

全加器(full adder)将两个一位二进制数相加,并根据接收到的低位进位信号,输出和、进位输出。全加器的三个输入信号为两个加数 A、B 和低位进位 Cin。全加器通常可以通过级联(cascade)的方式,构成多位(如8位、16位、32位)二进制数加法器的基本部分。全加器的输出和半加器类似,包括向高位的进位信号 Cout 和本位的和信号 S,相加结果的总和用十进制表达为:

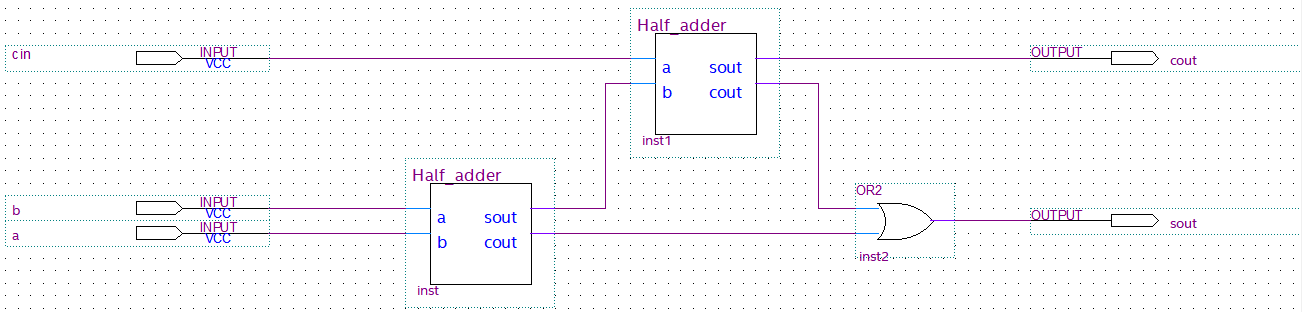

下图是一个最简单的一位全加器设计:

图中的方框是我们设计好的半加器

一位全加器的真值表为:

| A | B | Cin | Cout | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

在实际的应用中,全加器可以通过不同的方式制造,例如直接利用晶体管级的电路,或者由其他现成的逻辑门来构成。和、进位信号对应的逻辑函数表达式分别为

以及

另一种全加器电路与之前的方式略有不同,它用一个异或门来代替或门对其中两个输入信号进行求和,其进位信号对应的逻辑函数表达式分别为

通过适当的逻辑函数变化,可以证明它与前面的计算方法结果一致

在这个实现中,将最后的或门换成异或门不会影响逻辑。如果电路使用的是每个芯片上只有一种闸的简单集成电路芯片,仅使用两种闸会比较方便

全加器可以用两个半加器来构造,将输入端A和B连接到一个半加器上,然后将其和输出信号与进位输入信号分别作为第二个半加器的两个输入,并将两个进位输出信号进行逻辑或运算。全加器的关键路径(critical path,即经历最多逻辑门的路径)经过两个异或门,终止于和位 S ,假定异或门耗费3个延迟来完成,一个全加器的关键路径上施加的延迟等于

进位模块( carry-block )包括 2 个逻辑门,因此延迟为

全加器还可以使用一个三输入的异或门来求和,再使用一个两级与或结构来实现进位信号对应的积之和(sum of products)式

多位全加器

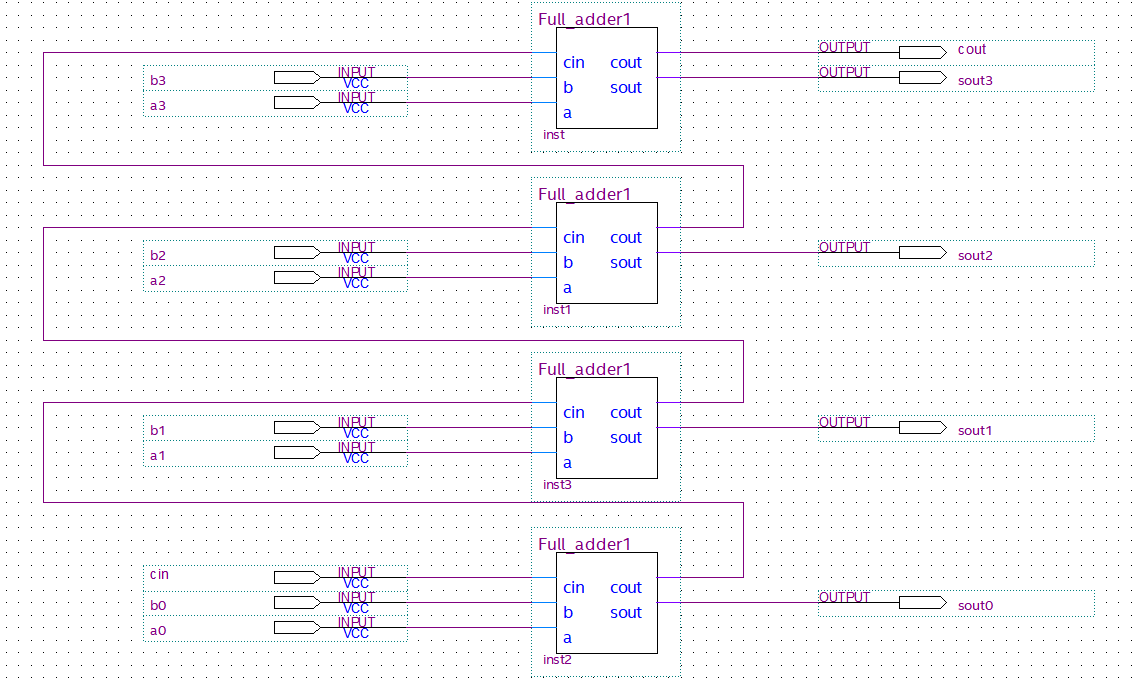

这里我们以四位全加器为例,我们使用一种最简单的方法对多位全加器进行构造,就是把我们的一位全加器进行加和

下图是一个最简单的四位全加器设计:

图中的方框是我们设计好的一位全加器

代码设计

半加器:

module Hallfadder

(

input a,b,

output cout,sum

);

assign sum = a^b;

assign cout = a&b;

endmodule

一位全加器:

module Full_adder1

(

input a,b,

output sum,

output cout,

input cin,

);

assign{cout,sum} = a+b+cin;

endmodule

四位全加器:

module Full_adder4

(

input [3:0] a,

input [3:0] b,

input cin,

output [3:0] sum,

output cout

);

assign{cout,sum} = a+b+cin;

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号