STM32 —— SPI 协议入门

STM32 —— 标准 SPI 协议入门

简介

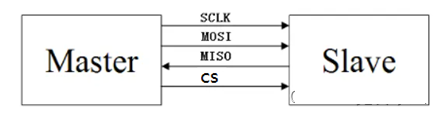

SPI 是由摩托罗拉(Motorola)公司 20 世纪 80 年代中期开发的全双工同步串行总线,标准 SPI 有 4 根线,它们是 MISO(主设备数据输入)、MOSI(主设备数据输出)、SCLK(时钟)、CS(片选),如下图:

SPI是串行扩展总线,串行总线技术可以使系统的硬件设计大大简化、系统的体积减小、可靠性提高。同时系统的更改和扩充极为容易。常用的串行扩展总线有:I2C( Inter IC Bus )总线、单总线( 1-WIRE BUS )、SPI( Serial Peripheral Interface )总线及 Microwire/PLUS 等

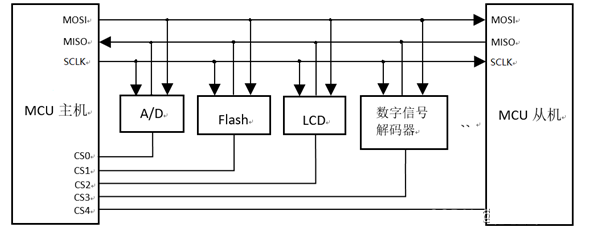

SPI 是微处理控制单元( MCU )和外围设备之间进行通信的同步串行端口。主要应用在 EEPROM、Flash、实时时钟( RTC )、数模转换器( ADC )、网络控制器、MCU、LCD 屏、数字信号处理器( DSP )以及数字信号解码器之间。SPI 典型系统框图如下图,接线方式:主设备 MISO 接从设备 MISO ,主设备 MOSI 接从设备 MOSI ,主从设备所有 SCLK 接在一起,主设备 CS0-CSn 接不同从设备 CS

SPI 总线是微控制器四线的外部总线。SPI 没有明文标准,是一种事实总线,对通信操作的实现由芯片厂商和驱动开发者通过 data sheet 和 application notes 沟通实现的细节。SPI 是四根信号线协议,如下:

主要特点

全双工

可以当作主机或从机工作

提供频率可编程时钟

发送结束中断标志

写冲突保护,总线竞争保护等

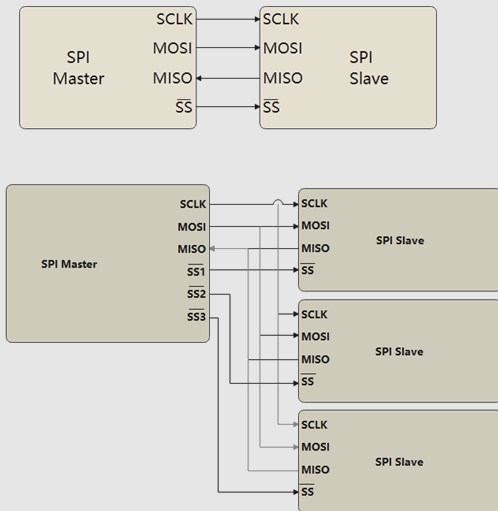

工作方式

SPI 是单主设备通信,总线中只有一个设备发起通信,能发起通信的设备称为主设备。当 SPI 主设备想读/写从设备时,首先拉低对应从设备的 SS 线( SS 是低电平有效);然后发送工作脉冲到时钟线上,在相应的脉冲时间上,主设备把信号发到 MOSI 实现写,同时可以对 MISO 线采样实现读

SPI 有四种操作模式:模式 0、模式 1、模式 2、模式 3,下面将分别进行介绍

通讯过程

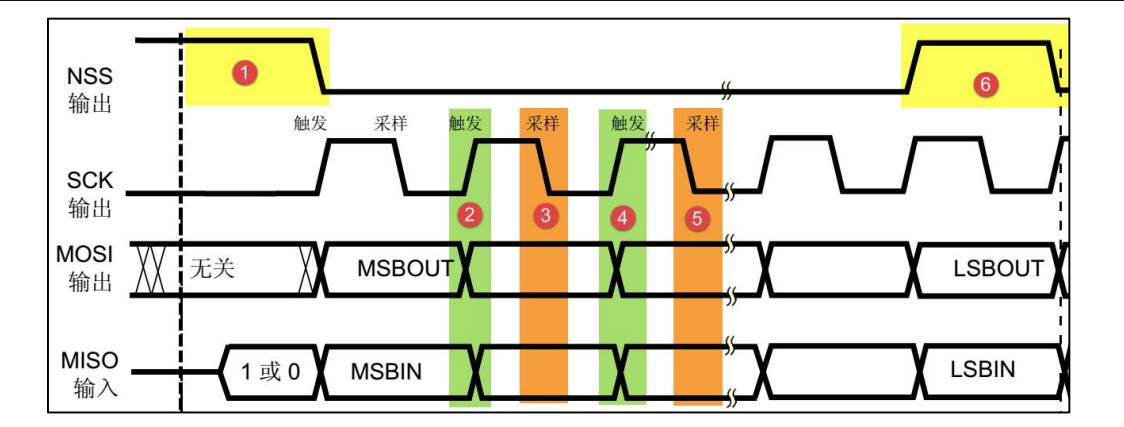

MOSI 与 MISO 的信号只在 NSS 为低电平的时候才有效,在 SCK 的每个时钟周期 MOSI 和 MISO 传输一位数据

CPOL 和 CPHA

这几个模式之间的区别是定义了在时钟脉冲的哪条边沿转换(toggles)输出信号,哪条边沿采样输入信号,还有时钟脉冲的稳定电平值(即时钟信号无效时是高还是低)。每种模式由两个参数描述,称为时钟极CPOL(clock polarity)与时钟期CPHA(clock phase)

CPOL:时钟极性为 0 时 SPI 总线空闲为低电平,为1时SPI总线空闲为高电平

CPHA:时钟相位为 0 时在 SCK 第一个跳变沿采样,为1时在SCK第二个跳变沿采样

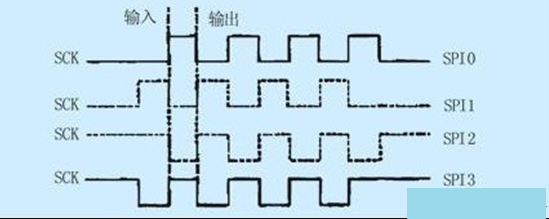

下图 SPI 总线时钟和相位不同延伸出四种工作方式,其中使用的最为广泛的是 SPI0 和 SPI3 方式 (实线表示):

Mode = Bit[CPOL]Bit[CPHA]

CPOL=0 表示 SCK 在空闲状态时为 0

CPOL=1 表示 SCK 在空闲状态时为 1

CPHA=0 表示在 SCK 第一个边沿时输入输出数据有效

CPHA=1 表示在 SCK 第二个边沿时输入输出数据有效

一般从器件的工作模式是固定的,主机要跟从机采用一样的工作模式,双方才能正常通信。如果有多个从设备,且从设备使用了不同的工作参数,那么主设备与不用的从设备通信时必须重新配置这些参数

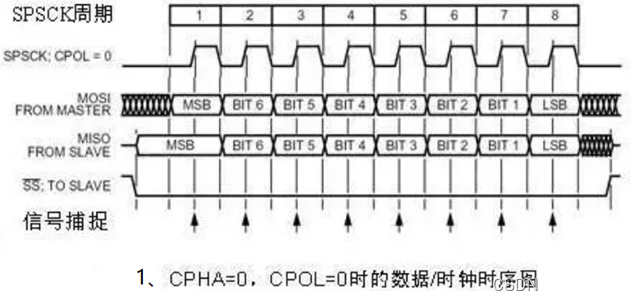

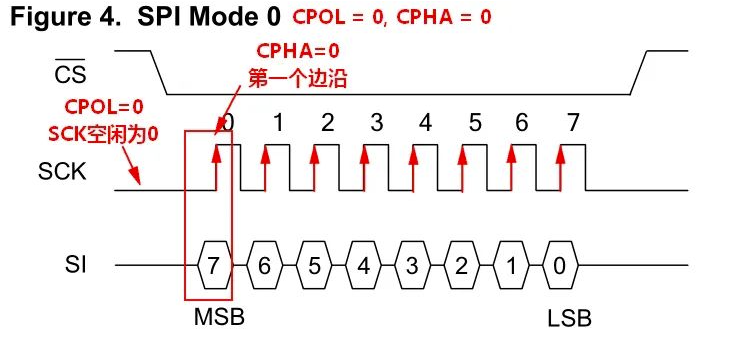

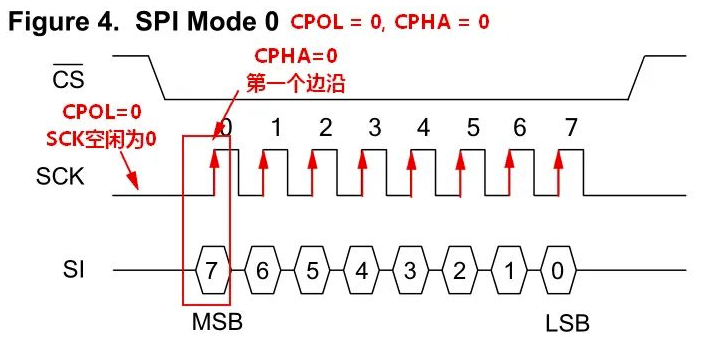

Mode 0

当 CPHA=0、CPOL=0 时 SPI 总线工作在方式 1,SCK空闲状态为低电平,主机数据在每个上升沿被从机采样。MISO 引脚上的数据在第一个 SPSCK 沿跳变之前已经上线了,而为了保证正确传输,MOSI 引脚的 MSB 位必须与 SPSCK 的第一个边沿同步,在 SPI 传输过程中,首先将数据上线,然后在同步时钟信号的上升沿时,SPI 的接收方捕捉位信号,在时钟信号的一个周期结束时(下降沿),下一位数据信号上线,再重复上述过程,直到一个字节的 8 位信号传输结束

Mode 0

当 CPHA=0、CPOL=0 时 SPI 总线工作在方式 0 。SCK 空闲状态为低电平,主机数据在每个上升沿被从机采样,数据输出同理。 MISO 引脚上的数据在第一个 SPSCK 沿跳变之前已经上线了,而为了保证正确传输,MOSI 引脚的 MSB 位必须与 SPSCK 的第一个边沿同步,在 SPI 传输过程中,首先将数据上线,然后在同步时钟信号的上升沿时,SPI 的接收方捕捉位信号,在时钟信号的一个周期结束时(下降沿),下一位数据信号上线,再重复上述过程,直到一个字节的 8 位信号传输结束

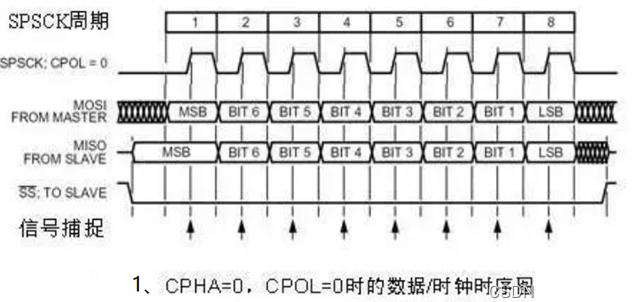

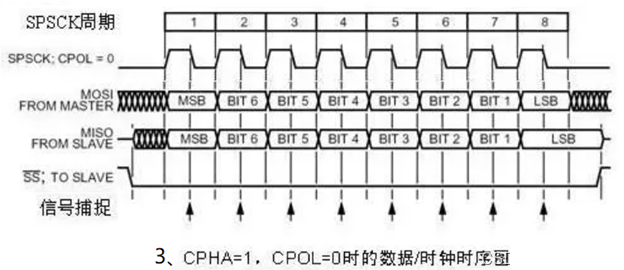

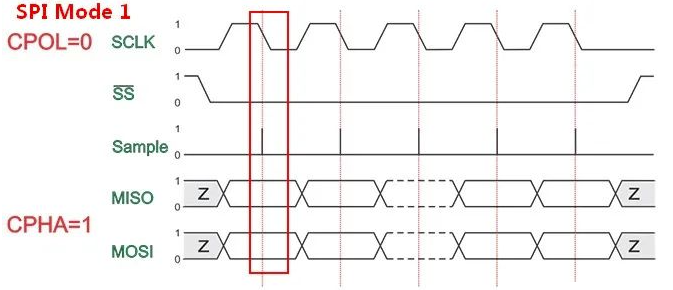

Mode 1

当 CPHA=1、CPOL=0 时,SCK 空闲时为低电平,在 SCK 第二个边沿时数据有效,即 SCK 下降沿有效。SPI 总线工作在方式 1 。MISO 引脚和 MOSI 引脚上的数据的MSB位必须与 SPSCK 的第一个边沿同步,在 SPI 传输过程中,在同步时钟信号周期开始时(上升沿)数据上线,然后在同步时钟信号的下降沿时,SPI 的接收方捕捉位信号,在时钟信号的一个周期结束时(上升沿),下一位数据信号上线,再重复上述过程,直到一个字节的 8 位信号传输结束

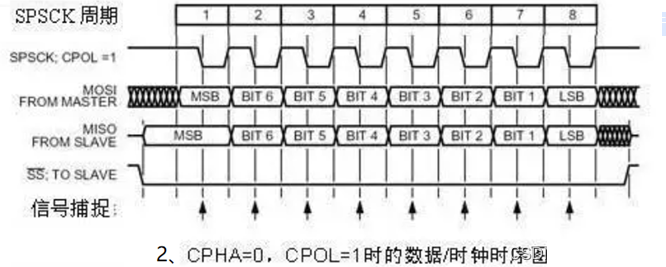

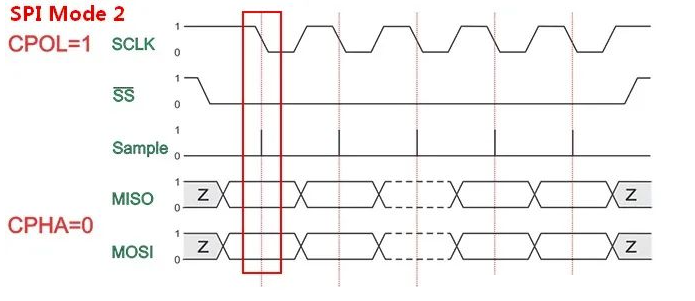

Mode 2

当 CPHA=0、CPOL=1 时 SPI 总线工作在方式 2 ,SCK 空闲时为高电平,在 SCK 第一个边沿时数据有效,即 SCK 下降沿有效。与前者唯一不同之处只是在同步时钟信号的下降沿时捕捉位信号,上升沿时下一位数据上线

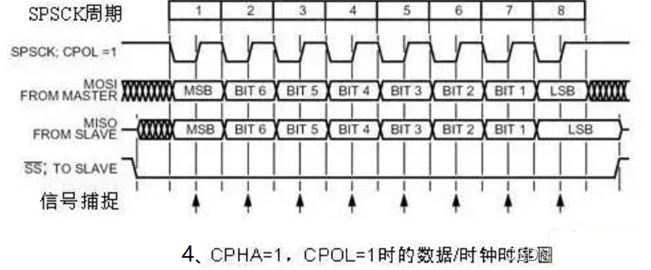

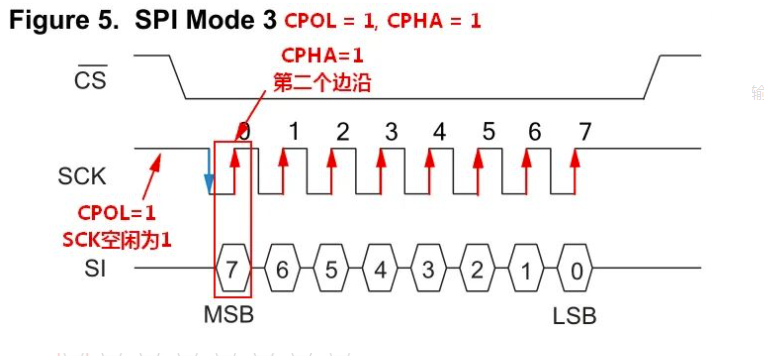

Mode 3

当 CPHA=1、CPOL=1 时 SPI 总线工作在方式3。SCK 空闲状态为高电平,主机数据在第二个边沿时有效,即每个上升沿被从机采样。与前者唯一不同之处只是在同步时钟信号的上升沿时捕捉位信号,下降沿时下一位数据上线

基本时序

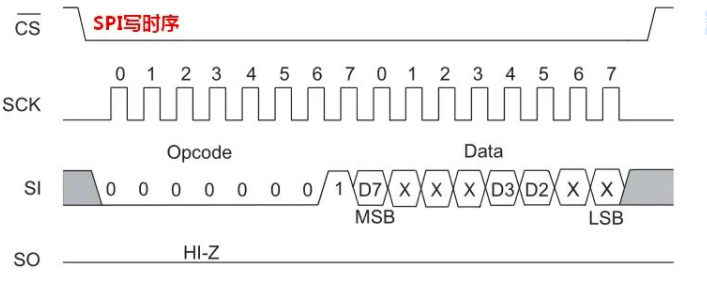

SS 为低电平时,表示对应的从机设备被使能,在每个 SCK 周期可以传输 1Bit 数据,采样时刻取决于器件支持的 SPI mode ,根据不同 SPI 器件的控制方法,在进行正式的数据读写操作前,一般需要先写入控制字,然后是寄存器地址和数据

如下是 FM25V05 铁电存储器采用 SPI 模式 0 的写时序,SS(CS) 被拉低,主机数据在每个上升沿被从机采样,Opcode 是控制字,控制字采样结束后开始采样数据:

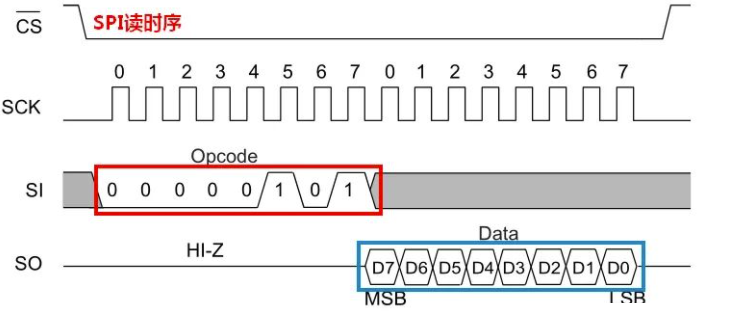

如下是FM25V05铁电存储器采用SPI模式0的读时序:

需要注意的是在 SS 下降沿和 SCLK 第一个边沿,或 SS 上升沿和 SCLK 最后一个边沿之间要留有一定的延迟时间,一般是 0.5 个 SCLK 周期。

浙公网安备 33010602011771号

浙公网安备 33010602011771号